vivado 与系统设计师接口

与系统设计师接口

作为迭代I/O和时钟规划过程的一部分,您可以交换有关AMD设备通过导出CSV文件和IBIS模型,与PCB或系统设计者进行引脚连接。根据PCB或设计规范的变化,您可能需要将引脚重新导入为如定义和配置I/O端口中所述。完成I/O和时钟中的步骤后规划流程,您可以返回引脚以及用于信号完整性分析的设备模型,使用CSV文件和IBIS模型。

导出I/O引脚和包数据

您可以出于以下目的导出I/O引脚和封装引脚信息:

•I/O引脚信息:您可以将I/O端口列表导出到用于RTL编码或PCB的文件中图例创建。

•封装引脚信息:当使用精心设计、合成或实施的设计时,您可以将设备包引脚信息导出到CSV文件中。包装引脚导出列表的部分是在中定义I/O端口定义的良好起点电子表格格式。导出的信息包括有关所有程序包的信息设备中的引脚以及设计特定的I/O端口分配及其配置。添加的列和用户定义的值将被保留并导出到输出文件中。对于有关导出的CSV文件格式的信息,请参阅定义和配置I/O端口和使用CSV文件格式的I/O端口列表。要导出I/O端口列表信息,请执行以下操作:

1.选择文件 → 出口 → 导出I/O端口。

2.在“导出I/O端口”对话框中,指定要生成的I/O端口类型和路径,然后单击“确定”。

注意:XDC文件中只显示固定的约束,这些约束表示端口是由用户分配的。

生成IBIS模型

输入/输出缓冲区信息规范(IBIS)是一种设备建模标准。IBIS允许开发用于描述设备信号行为的行为模型互连。与结构模型不同,这些模型保留了专有的电路信息例如由集成电路重点仿真程序(SPICE)生成的那些模拟。IBIS缓冲模型基于测量或通过电路仿真。IBIS模型是为每个IOB标准构建的,IBIS文件是IBIS模型的集合用于设备中的所有I/O标准。IBIS文件还包含设备上使用的引脚列表被绑定到IOB,IOB被配置为支持与引脚相关联的特定I/O标准具有特定的IBIS缓冲模型。IBIS标准规定了包含文件头的输出信息文件的格式部分和组件描述部分。

Golden Parser是由IBIS开发的

开放论坛小组(www.ibis.org)通过验证语法符合IBIS数据格式。

当您在AMD Vivado中导出IBIS模型时™ IDE中,该工具输出一个.ibs文件。此文件包括您的设计使用的引脚列表,连接到的设备内部信号那些引脚和IBIS缓冲区

导出IBIS模型

为了更好地理解系统级的信号完整性,PCB设计者通常需要用IBIS模型模拟设计。设计者必须考虑信号完整性问题,例串扰、接地反弹和SSN。IBIS模型有助于表征电流-电压(I-V)曲线以及封装器件的寄生信息。

提示:您可以从Xilinx下载页面下载通用IBIS模型。连接到引脚的IOB的模型。

从Vivado IDE,您可以根据设计和每个引脚的包数据生成IBIS模型。Vivado IDE使用设计中的网表和实现细节,并将其结合起来具有可用的每个引脚寄生封装信息的信息,以创建自定义IBIS设计模型。打开详细的、综合的或实现的设计后,可以导出IBIS文件以供使用在对设计进行如下分析时:

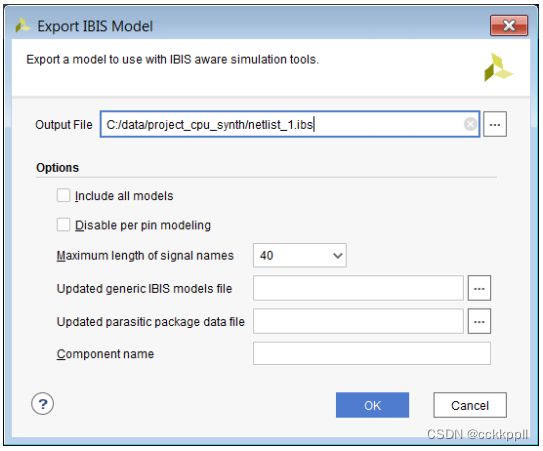

1.选择文件 → 出口 → 导出IBIS模型。

2.在“导出IBIS模型”对话框中,设置以下选项,然后单击“确定”:

•输出文件:指定输出IBIS文件的文件名和路径。

•包括所有型号:包括此设备的所有可用I/O缓冲区型号。默认情况下,仅包括设计中使用的缓冲区模型。

•禁用每引脚建模:禁用包的每引脚建模。这是从器件的管芯焊盘到封装的引脚的路径。

具有按引脚建模

禁用时,封装被简化为应用于所有引脚的单个RLC传输线模型并在IBIS文件的[Package]部分中定义。

•信号名称的最大长度:将信号名称截断到指定的极限

•40:将信号名称截断为40个字符,IBIS 4.2版支持此操作默认值。

•20:将信号名称截断为20个字符。

•无限制:不要截断信号名称。

•更新的通用IBIS模型文件:可选择为设备提供IBIS模型档案。这用于覆盖在部件目录下的安装中找到的IBIS模型。

重要!未包含IBIS模型的设备需要IBIS模型文件安装软件。

•更新的寄生软件包数据文件:(可选)提供一个寄生软件包文件(.pkg扩展名)文件以用于逐引脚提取。这用于覆盖寄生封装在parts目录下的安装层次结构中找到的文件。

•组件名称:可以选择指定一个新的组件名称来更改默认名称值,即设备系列。

与PCB设计的接口

Vivado引脚规划器提供了一种为设计选择引脚分配的有效方法。选择正确的资源可以实现更快、更干净的设计过程。中的建议本节有助于防止电路板布局、引脚分配和FPGA资源冲突。了解更多有关PCB和引脚规划的信息,请参阅以下设备指南之一:

•7系列FPGA PCB设计指南(UG483)

•UltraScale体系结构PCB设计用户指南(UG583)

•Zynq-7000 SoC PCB设计指南(UG933)

部件兼容性

如定义备用兼容零件中所述,为您的设计设置零件兼容性。Vivado IDE识别所有选定备用零件的公共端号,并指定禁止对并非所有设备都通用的引脚进行约束,从而消除使用的可能性这些针脚。有关详细信息,请参阅目标设备的产品表。

DRC

要检查I/O分配的整体完整性,请按照运行DRCs中的说明运行DRCs。它重要的是,在启动板之前解决DRC报告的所有警告和错误规划。

SSN分析

要生成潜在噪声干扰的估计值,请按照工作中的说明运行SSN分析使用SSN分析。AMD建议您在启动主板之前解决与噪音相关的问题规划。有关更多信息,请参阅SelectIO™ 设备的资源:

•7系列FPGA SelectIO资源用户指南(UG471)

•UltraScale体系结构SelectIO资源用户指南(UG571)

以及设备的内存资源:

•《UltraScale体系结构内存资源用户指南》(UG573)

•Zynq 7000 SoC和7系列设备内存接口解决方案(UG586)

IBIS仿真

要运行IBIS模拟,请使用Vivado IDE生成的IBIS文件,如生成中所述IBIS模型。

包跟踪长度

Vivado Design Suite提供的不是跟踪长度数据,而是跟踪延迟数据,即估计包裹延迟的最准确方法。

1.在Vivado中打开一个设计,可以是RTL、网表或已实现的。

2、选择文件 → 出口 → 导出CSV类型电子表格的I/O端口,该电子表格显示最小值和每个引脚的最大封装延迟。最小/最大跟踪延迟也显示在Package中两个独立列中每个封装引脚的引脚窗口。

3.如果没有项目,可以使用以下Tcl命令:

CSV导出

运行DRC和SSN分析后,将CSV文件导出为如导出I/O引脚和封装数据中所述。支持的第三方PCB工具为了在整个板的上下文中优化I/O分配,AMD还支持Cadence Allegro FPGA系统规划师和图形I/O设计师导师。欲了解更多信息,请参阅第三方工具文档。