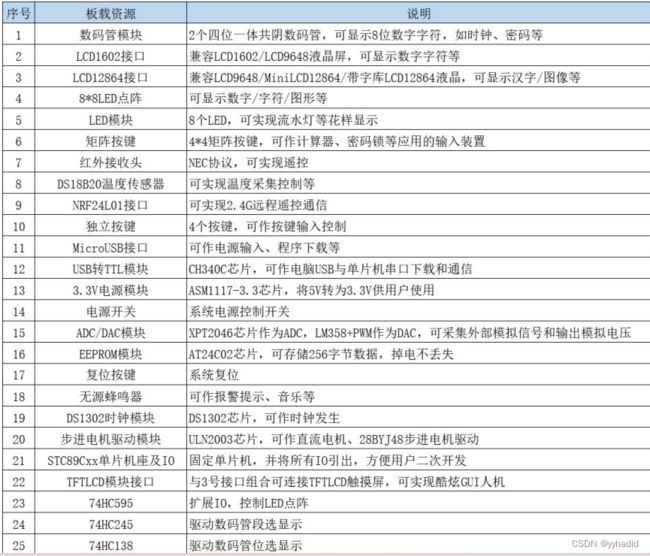

51单片机A2开发板功能介绍

一.开发板各功能模块

1、TTL (Transistor-Transistor Logic)电平是一种数字电平标准,常用于数字电路和逻辑电路中,TTL电平信号用的最多,这是因为数据通常用二进制表示。TTL电平使用电压来表示逻辑状态,通常有两个级别:

(1)高电平(High Level):TTL逻辑中的高电平通常被定义为2.4V至5V之间的电压范围。在TTL电路中,高电平表示逻辑1或“真”状态。

(2)低电平(Low Level):TTL逻辑中的低电平通常被定义为0V至0.8V之间的电压范围。在TTL电路中,低电平表示逻辑0或“假”状态。

2、RS232(Recommended Standard 232)是一种常用的串行通信接口标准,用于在计算机和外部设备之间传输数据。RS232使用电压来表示逻辑状态,有以下两个基本电平:

(1)正电平(Positive Voltage Level):在RS232中,正电平通常定义为-3V至-15V之间的电压范围。正电平表示逻辑1或“真”状态。

(2)负电平(Negative Voltage Level):在RS232中,负电平通常定义为+3V至+15V之间的电压范围。负电平表示逻辑0或“假”状态。

3、(1)VOH(voltage output high)数字逻辑电路参数,用于描述逻辑门输出的高电平电压的最小值;对于接收voh作为输入的下游器件,如果其输入电压高于VOH ,它将被认为是高电平(逻辑1),若低于voh则被认为是低电平(逻辑0)。

(2)VOL逻辑电平0的输出电压,用于描述逻辑门输出低电平电压的最大值;对于接收vol作为输入的下游器件,如果其输入电压高于vol,它将被认为是高电平(逻辑1),若低于vol则被认为是低电平(逻辑0)。

(3)VIH(voltage input high)逻辑电平1的输入电压,逻辑门输入的最小高电平电压

(4)VIL,逻辑电平0的输入电压,逻辑门输入的最大低电平电压

4、(1) TTL电平临界值

VOH=2.4V VOL=0.4V VIH=2.0V VIL=0.8V

(2) CMOS电平临界值(假设电源电压为+5V)

VOH=4.99V VOL=0.01V VIH=3.5V VIL=1.5V

注:TTL和CMOS的逻辑电平转换:CMOS电平能驱动TTL电平,但TTL电平不能驱动CMOS电平(因为CMOS电平范围包括TTL电平范围),需要加上拉电阻,上拉电阻的作用是将信号线或节点拉高至供电电压(例如VDD)或高电平。

二.漏极开路

漏极开路(Open-Drain)是一种特殊的输出模式,常见于某些集成电路和单片机的引脚设计中。在漏极开路模式下,输出引脚可以主动拉低(输出低电平),但不能主动拉高(输出高电平)。

当引脚处于漏极开路模式时,它可以分为两种状态:

-

拉低状态(Low state):引脚被拉低,输出一个低电平(通常接近地(GND)电位)。在这种状态下,引脚被连接到地,形成一个低电平电路。

-

高阻态(High-Z state):引脚不被拉高,处于高阻抗状态。在这种状态下,引脚与外部电路断开,相当于一个高电阻。引脚不会主动拉高,而是由外部电路提供上拉电阻来拉高引脚。

漏极开路模式的一个重要应用是实现多个引脚的共享总线。通过将多个漏极开路引脚连接到同一总线线路上,并通过上拉电阻将总线拉高,可以实现多个设备在同一总线上进行通信。每个设备可以通过拉低自己的引脚来将数据传输到总线上,而通过释放引脚进入高阻态,设备可以监听总线上的数据。

需要注意的是,漏极开路模式通常不适用于直接驱动电路或需要主动输出高电平的情况。为了输出高电平,通常需要使用外部上拉电阻或其他驱动电路。漏极开路模式更适用于共享总线、多设备通信和开关控制等应用场景。

当需要在该引脚上输出高电平时,确实需要使用外部上拉电阻。上拉电阻会将该引脚连接到正电源,以提供高电平信号。

一种常见的连接方式是通过上拉电阻将P0口连接到正电源(通常是Vcc)。这样,在引脚没有被拉低时,外部上拉电阻会将引脚拉高,使其保持在高电平(逻辑1)状态。

下图显示了P0口的连接方式,其中R为上拉电阻,Vcc为正电源:

+----- Vcc

|

R

|

P0 -----+

三、reg52.h头文件介绍

1.和“reg52.h”的区别

在代码中加入头文件有两种书写方法,如标题所示。

- 当使用 <> 包含头文件时,编译器先进入到软件安装文件夹处开始搜索这个头文件,也就是KEILC51/C51/INC这个文件夹下,如果这个文件夹下没有引用的头文件,编译器将会报错。

- 当使用 " " 包含头文件时,编译器先进入到当前工程所在文件夹处搜索该头文件,如果当前工程文件夹没有该头文件,编译器将继续回到软件安装文件夹处搜素该头文件,若搜不到该头文件,编译器报错。

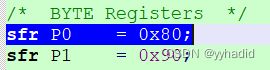

2.sfr和sbit关键字

- “sfr P0=0X80”语句的意义是把单片机内部地址0X80这个寄存器命名为P0,以后我们可以在程序中直接操作P0,相当于对单片机内部的0X80这个地址的寄存器进行操作。

- “ sbit CY=PSW^7; ”语句的意义是将PSW这个寄存器的最高位命名为CY,我们要单独操作PSW寄存器的最高位时,可直接操作CY.

四、点亮一个LED灯

1.P0端口

2.与非门

与非门由两个输入和一个输出构成,其输出与&的结果相反