6678DSP基础

环境:CCS12.5

1、ti官网下载CCS

CCSTUDIO IDE, configuration, compiler or debugger | TI.com

2、ti官网下载多核开发组件mcsdk

BIOSLINUXMCSDK Software development kit (SDK) | TI.com

下载 bios_mcsdk_02_01_02_06_setupwin32.exe

版本竟然是2013年发布的

3、安装

。。。。。。

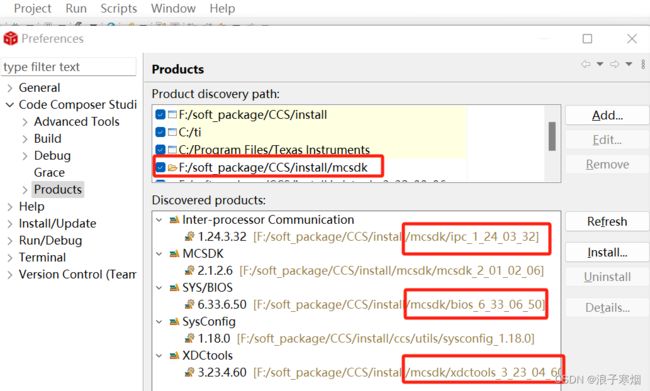

需要注意的是 xdctools/bios/ipc 版本要按官网的建议匹配,不然会出现编译、运行等莫名其妙的问题,由于mcsdk里ipc版本比较老,和CCS自带的bios和xdctools不匹配。懒得折腾,笔者选择xdctools/bios/ipc这三个组件都用mcsdk里的

打开CCS,Window->Preferences->Products 指定安装的组件路径

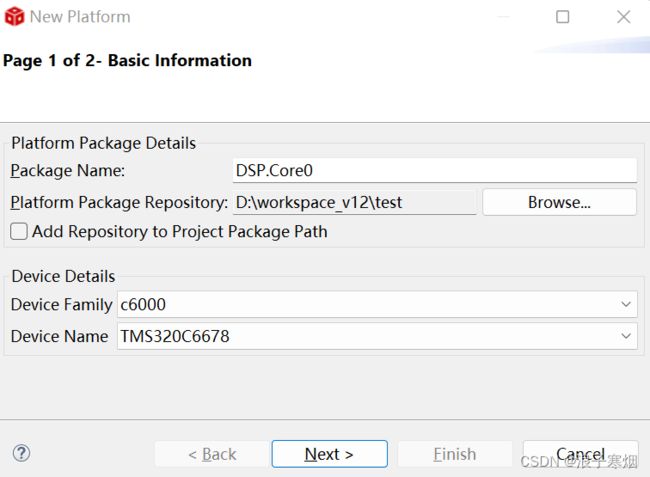

4、新建platform

Project->RTSC Tools->Platform->New

随便取名,因为有多个核,DSP.Core0表示 DSP/Core0目录下

然后根据意愿定制内存划分:L1P/L1D/L2/MSM/DDR

配置生成的文件是Platform.xdc

metaonly module Platform inherits xdc.platform.IPlatform {

config ti.platforms.generic.Platform.Instance CPU =

ti.platforms.generic.Platform.create("CPU", {

clockRate: 1000,

catalogName: "ti.catalog.c6000",

deviceName: "TMS320C6678",

customMemoryMap:[

["BOOT_L2", {name: "BOOT_L2", base: 0x10800000, len: 0x200, space: "code/data", access: "RWX",}],

["ISRAM_L2", {name: "ISRAM_L2", base: 0x10800200, len: 0x3FE00, space: "code/data", access: "RWX",}],

["CACHE_L2", {name: "CACHE_L2", base: 0x10840000, len: 0x40000, space: "code/data", access: "RWX",}],

["MSMCSRAM", {name: "MSMCSRAM", base: 0x0c000000, len: 0x80000, space: "code/data", access: "RWX",}],

["MSMCSRAM_IPC", {name: "MSMCSRAM_IPC", base: 0x0c200000, len: 0x200000, space: "code/data", access: "RWX",}],

["SDRAM_CACHED_DATA_CORE0", {name: "SDRAM_CACHED_DATA_CORE0", base: 0x90000000, len: 0x400000, space: "code/data", access: "RWX",}],

["SDRAM_CACHED_CODE_CORE0", {name: "SDRAM_CACHED_CODE_CORE0", base: 0x90400000, len: 0x200000, space: "code/data", access: "RWX",}],

["SDRAM_NOCACHE_DATA_CORE0", {name: "SDRAM_NOCACHE_DATA_CORE0", base: 0x9F000000, len: 0x100000, space: "code/data", access: "RWX",}],

],

l2Mode: "256k",

l1PMode: "32k",

l1DMode: "32k",

});

instance :

override config string codeMemory = "SDRAM_CACHED_CODE_CORE0";

override config string dataMemory = "SDRAM_CACHED_DATA_CORE0";

override config string stackMemory = "SDRAM_CACHED_DATA_CORE0";

}同理,配DSP.Core1...DSP.Core7,配齐8核

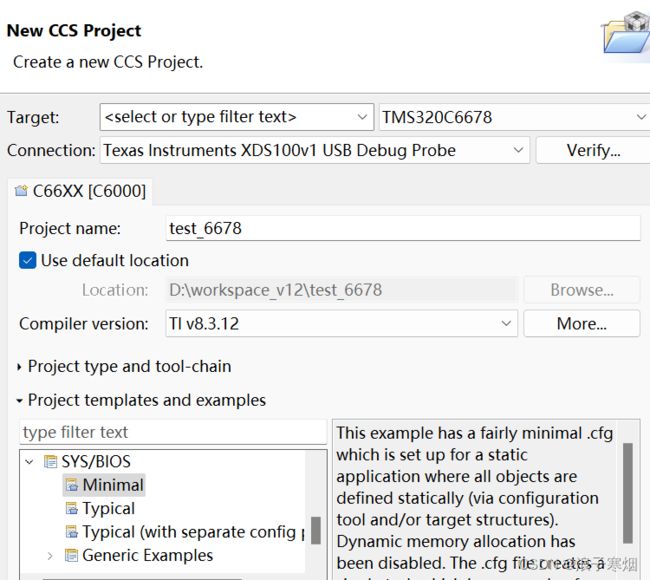

5、新建工程

选择SYS/BIOS工程

Products项Add增加IPC,有多个xdctools/bios版本也可以修改,注意各版本匹配

XDCpath项Add指定platform路径,上文新建过的

Target 选择 ti.targets.elf.C66

Platform选择DSP.Core0,其他核工程选择对应的platform

6、cfg

根据自己需要修改cfg

/* Load and configure SYSBIOS packages */

var BIOS = xdc.useModule('ti.sysbios.BIOS');

var Clock = xdc.useModule('ti.sysbios.knl.Clock');

var Swi = xdc.useModule('ti.sysbios.knl.Swi');

var Task = xdc.useModule('ti.sysbios.knl.Task');

var Semaphore = xdc.useModule('ti.sysbios.knl.Semaphore');

var Hwi = xdc.useModule('ti.sysbios.hal.Hwi');

var HeapBuf = xdc.useModule('ti.sysbios.heaps.HeapBuf');

var HeapMem = xdc.useModule('ti.sysbios.heaps.HeapMem');

var BiosCache = xdc.useModule('ti.sysbios.hal.Cache');

var Cache = xdc.useModule('ti.sysbios.family.c66.Cache');

var CpIntc = xdc.useModule('ti.sysbios.family.c66.tci66xx.CpIntc');

var Memory = xdc.useModule('xdc.runtime.Memory');

var Load = xdc.useModule('ti.sysbios.utils.Load');

/*

* The SysStd System provider is a good one to use for debugging

* but does not have the best performance. Use xdc.runtime.SysMin

* for better performance.

*/

var System = xdc.useModule('xdc.runtime.System');

var SysStd = xdc.useModule('xdc.runtime.SysStd');

System.SupportProxy = SysStd;

/* Config heap size */

Program.sysStack = 0x8000;

Program.stack = 0x10000;

Program.heap = 0x200000;

Memory.defaultHeapSize = 0x200000;

/*

* Enable Event Groups here and registering of ISR for specific GEM INTC is done

* using EventCombiner_dispatchPlug() and Hwi_eventMap() APIs

*/

/*

var Ecm = xdc.useModule('ti.sysbios.family.c64p.EventCombiner');

Ecm.eventGroupHwiNum[0] = 7;

Ecm.eventGroupHwiNum[1] = 8;

Ecm.eventGroupHwiNum[2] = 9;

Ecm.eventGroupHwiNum[3] = 10;

*/

/*Exception*/

var Exc = xdc.useModule('ti.sysbios.family.c64p.Exception');

var Main = xdc.useModule('xdc.runtime.Main');

Exc.common$.logger = Main.common$.logger;

Exc.enablePrint = true

/* Load and configure the IPC packages */

var Notify = xdc.module('ti.sdo.ipc.Notify');

var Ipc = xdc.useModule('ti.sdo.ipc.Ipc');

var HeapBufMP = xdc.useModule('ti.sdo.ipc.heaps.HeapBufMP');

var MultiProc = xdc.useModule('ti.sdo.utils.MultiProc');

var MessageQ = xdc.useModule('ti.sdo.ipc.MessageQ');

MultiProc.setConfig(null, ["CORE0", "CORE1", "CORE2", "CORE3", "CORE4", "CORE5", "CORE6", "CORE7"]);

/* Synchronize all processors (this will be done in Ipc_start) */

Ipc.procSync = Ipc.ProcSync_ALL;

/* Shared Memory base address and length */

var SHAREDMEM = 0x0c200000;

var SHAREDMEMSIZE = 0x00200000;

/*

* Need to define the shared region. The IPC modules use this

* to make portable pointers. All processors need to add this

* call with their base address of the shared memory region.

* If the processor cannot access the memory, do not add it.

*/

var SharedRegion = xdc.useModule('ti.sdo.ipc.SharedRegion');

SharedRegion.setEntryMeta(0,

{ base: SHAREDMEM,

len: SHAREDMEMSIZE,

ownerProcId: 0,

isValid: true,

name: "MSMCSRAM_IPC",

});几个地方注意下

1)

Program.stack = 0x10000;

Program.heap = 0x200000;

栈和堆大小

2)

MultiProc.setConfig(null, ["CORE0", "CORE1", "CORE2", "CORE3", "CORE4", "CORE5", "CORE6", "CORE7"]);

Ipc.procSync = Ipc.ProcSync_ALL;

配置8核,代码通过Ipc_start()多核同步

3)

var SHAREDMEM = 0x0c200000;

var SHAREDMEMSIZE = 0x00200000;

var SharedRegion = xdc.useModule('ti.sdo.ipc.SharedRegion');

SharedRegion.setEntryMeta(0,

{ base: SHAREDMEM,

len: SHAREDMEMSIZE,

ownerProcId: 0,

isValid: true,

name: "MSMCSRAM_IPC",

});

核间通信共享内存,platform有特意将这块划分出来,避免被使用

7、cmd

可以不改,platform会生成cmd。笔者的platform配置数据段和程序段都分配在DDR。

根据自己需要新建一个cmd

SECTIONS

{

.vecs > BOOT_L2

.text:_c_int00 > ISRAM_L2

.knl: {*.*(.text:*ti_sysbios_knl*)} > ISRAM_L2

.hwi: {*.*(.text:*ti_sysbios*_Hwi_*)} > ISRAM_L2

}8、仿真调试

修改ccxml文件,选择软仿真或者对应的仿真器,笔者demo板仿真器是XDS100v1

Advanced选择gel文件,gel文件在CCS安装目录:ccs_base\emulation\boards\evmc6678l\gel

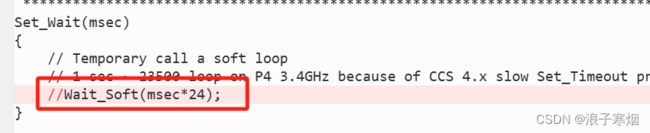

笔者用CCS安装目录的gel文件竟然加载失败,简单改了下

这个东西报错,具体为啥没管,简单看了下运行流程也不会执行

gel文件是啥,大概是个程序加载前运行,对外设初始化的脚本,比如时钟,DDR

笔者程序段都映射在DDR地址空间,所以仿真需要gel文件做初始化

9、hello world

mark:核间通信,edma 多核配置,8核处理算法,优化,雷达信号处理,8核boot