【TC3xx芯片】TC3xx DMA模块详解

目录

前言

正文

1.功能简介

2. DMA使用的时钟

3. DMA资源

4. DMA中断

5. DMA资源分区

6. DMA通道

6.1 DMA通道请求控制

6.2 DMA软件请求

6.3 DMA硬件请求

6.4 DMA软件和硬件组合请求

6.5 DMA菊花链请求

6.6 DMA通道传输请求丢失中断服务请求

6.7 DMA服务请求

6.8 DMA请求仲裁

6.9 DMA通道复位

6.10 DMA通道Halt

7. DMA随机访问内存

7.1 DMA通道操作

7.2 DMA通道更新

7.3 DMA通道重新配置

7.4 Move操作

7.4.1 地址计算

7.4.2 地址计算示例

7.4.3 循环Buffer

7.4.4 地址对齐

7.4.5 地址计数器

7.4.6 DMA地址Checksum

7.4.7 DMA通道中断服务请求

7.4.8 DMA传输中断服务请求

7.8. 阴影操作Shadow Operation

7.9. DMA时间戳

7.10. Pattern检测

7.11. 双Buffering操作

7.12. Linked List操作

8. Move Engine

9. DMA配置

9.1 DMA General Config

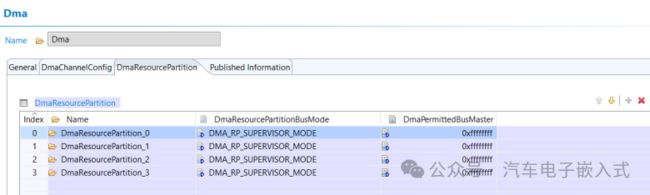

9.2 Dma Resource Partition Config

9.3 Dma Channel Config

10. DMA代码使用分析

11.总结

前言

AUTOSAR架构下的MCAL模块没有关于DMA的描述,但是在实际的使用过程中,MCAL的SPI模块一般都有是否使用DMA的配置,那么DMA到底是什么了?本文就来详细介绍TC3xx芯片的DMA模块。

注意:很多人都不喜欢理论介绍,都喜欢上来就是实战配置和应用,但是如果没有理论基础能根据实际需求配置好吗?除非是照猫画虎抄其他人的配置,但是实际还是没有深入理解的。只有理论都搞明白了,再去实践配置就如砍瓜切菜一样简单了,当然分析问题也更清晰明了。

缩略词

| 简写 |

全称 |

| DMA |

Direct Memory Access |

| Move |

Move Engine |

| PATDET |

Pattern Detection |

| RAMER |

RAM Error |

| RDCRC |

Read Data Cyclic Redundancy Check |

| RP |

Resource Partition |

| RROAT |

Reset Request Only After Transaction |

| SAFLL |

Safe Linked List |

| SDCRC |

Source Destination Cyclic Redundancy Check |

| SER |

Source Error |

| SLLER |

Safe Linked List Error |

| TCS |

Transaction Control Set |

| TRL |

Transaction/Transfer Request Lost |

| TS |

Trigger Set |

注:本文章引用了一些第三方工具和文档,若有侵权,请联系作者删除!

正文

1.功能简介

DMA 将数据从源位置移动到目标位置,而无需 CPU 或其他芯片设备的干预。数据搬移由 ME 执行, 数据的移动由DMA 通道的 TCS 控制。DMA 通道由 DMA 请求激活。

2. DMA使用的时钟

如果DMA数据搬移是从SRI-source到SRI-destination,则使用的是fSRI时钟(如下图所示的时钟配置,fSRI = 300MHz),且每次DMA数据搬移最大为8 Mbytes.

如果DMA数据搬移是从SPB-source到SPB-destination,则使用的是fSPB时钟(如下图所示的时钟配置,fSPB= 100MHz),且每次DMA数据搬移最大为1 Mbytes.

3. DMA资源

TC37x系列芯片最大支持4个RP (Resource Partition) ,最多支持128个 DMA Channels.

4. DMA中断

5. DMA资源分区

资源分区(Resource Partitions):

--运行一组定义的移动数据功能的应用程序应不受另一个运行另一组定义的移动数据功能的应用程序的干扰。

--每个 RP 都具有独立的访问启用(Access Enable)控制,方法是使各个主标签(Master TAG identifiers)标识符能够对 RP 和分配的 DMA 通道启用写入访问。

--在DMA移动期间,每个RP具有被驱动到片上总线上的唯一主标签标识符。

--每个RP在supervisor模式或用户(user)模式下执行片上总线访问。

在配置DMA的时候,每一路DMA通道应该分配给一个RP.

每个RP都有自己的访问启用(Access Enable)保护。从目的地控制对其总线外围接口和内核地址空间的访问。每个具有总线主控功能的片上资源都有一个唯一的主标签标识符,用于识别片上总线事务的源。基于主标签标识符的访问保护用于实现对单个从属地址范围的写访问。

每个RP生成一个错误中断服务请求,以覆盖分配给该RP的DMA信道的所有错误事件,包括ME对DMA请求的服务:

. DMA channel TRL interrupt service request.

. ME SER and DER error interrupt service request.

. ME DMARAM Integrity Error error interrupt service request.

. ME Linked List Operation TCS Load Error error interrupt service request.

. ME SAFLL DMA Address Checksum Error error interrupt service request

如果触发DMA RP错误中断服务请求,则软件RP应用程序应读取错误状态寄存器的内容,以识别错误的来源。

6. DMA通道

每个DMA通道都被分配给一个RP,并存储独立DMA操作的上下文。

6.1 DMA通道请求控制

每一路DMA通道都是单独可编程(配置)的,可以通过以下四种方式请求DMA通道传输:

. DMA软件请求,由CPU来触发(也就是用户通过软件来触发)。

. DMA硬件请求,由中断路由(IR)模块和中断控制单元(ICU)模块来触发。

. DMA 菊花链请求,由下一个更高优先级的DMA通道触发。

. DMA自动开始请求,在DMA Linked List加载下一个TCS (Transaction Control Set) 期间触发。

DMA 通道状态标志 TSR.CH 指示 DMA 请求是否挂起。在 DMA 传输开始或 DMA 事务结束时, TSR.CH 可能被清除。因此, DMA 请求可能触发单个 DMA 传输或一个完整的 DMA 事务。

每个DAM通道有下表的5种状态:

CHCFGR寄存器的RROAT配置位域用来配置DMA通道状态(TSR.CH)标志位是否在仅在DMA Transaction后才被清除。

如果CHCFGR.RROAT=0

--DMA 通道 TSR.CH 在每次 DMA transfer开始时被清除。

--单个DMA Transfer后开始一次DMA Request.

如果CHCFGR.RROAT=1

--DMA 通道 TSR.CH 在每次 DMA Transaction结束时被清除。

--一次完整的DMA Transaction后开始一次DMA Request.

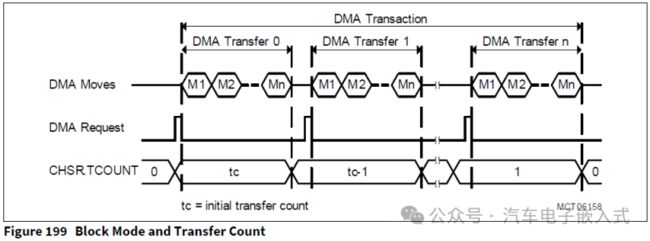

问题:DMA Transfer和DMA Transaction的区别?

6.2 DMA软件请求

一次DMA软件请求(DMA Software Request)可以开始一次完整的DMA事务(DMA Transaction)或开始一次DMA传输(DMA Transfer),却决于CHCFGR.RROAT的配置。

如果DMA通道仅仅想被软件触发,那么应该Disabled DMA Hardware Request(TSR.HTRE = 0B).

软件控制下的一次完整的DMA事务(DMA Transaction)需要完成以下的DMA 通道配置:

. DMA 通道CHCFGR.RROAT = 1

通过将 DMA 通道CHCSR.SCH 设置为 1B 启动 DMA 软件请求,结果将 TSR.CH 设置为 1B。 DMA 事务(Transaction)开始时, DMA 通道重新加载 CHFGR.TREL 的值加载到 ME CHSR.TCOUNT 中,并执行 DMA 传输。每次 DMA 传输后, ME CHSR.TCOUNT 都会递减,并计算下一个源地址和目标地址。当 TCOUNT 递减至 0D 时, DMA 通道状态标志 TSR.CH 将被重置(设置位0)。设置 DMA 通道 CHCSR.SCH = 1B 将再次启动 DMA 通道的新 DMA 事务,并使用存储的 TCS (Transaction Control Set)参数。

软件控制下的一次DMA传输(DMA Transfer)需要完成以下的DMA 通道配置:

. DMA 通道CHCFGR.RROAT = 0

必须通过将 DMA 通道 CHCSR.SCH 设置为 1B 来为每个 DMA 传输启动 DMA 软件请求。

问题:DMA Transfer和DMA Transaction的区别?

答:一次DMA Transaction可以包含一次或多次DMA Transfer, 如果配置CHCFGR.RROAT = 1,在设置CHCSR.SCH = 1开启一次DMA Transaction后会自动完成一次DMA Transaction中的所有DMA Transfer,在一次DMA Transaction后需要设置CHCSR.SCH = 1开启下一次DMA Transaction;如果配置 CHCFGR.RROAT = 0,则在每次的DMA Transfer后就需要配置CHCSR.SCH = 1开启下一次DMA Transfer. DMA Transfer将使得软件控制的粒度更小。

6.3 DMA硬件请求

DMA硬件请求enabled/disabled状态由DMA通道的TSR.HRTE(Hardware Transaction/Transfer Request Enable) 确定。HTRE 的功能如下所示:

. 软件设置 TSR.ECH = 1来Enable DMA硬件请求(通过设置TSR.ECH来控制TSR.HTRE状态=1),软件设置TSR.DCH = 1来Disable DMA硬件请求。

. 如果ME(Move Engine)上报一个DMA的通道错误,将会清除掉TSR.HTRE标志(TSR.HTRE = 0)。

. 如果DMA通道被配置为Single Mode, 则在CHCST.TCOUNT等于的0的时候会清除TSR.HTRE(在 DMA 事务的最后一次 DMA 传输开始时).

TSR.HTRE标志的Set/Reset情况如下表所示:

DMA通道模式

CHCFGR.CHMODE寄存器位域控制DMA通道模式:

Signal Mode (DMA channel CHCFGR.CHMODE = 0B)

nDMA 硬件请求在完成 DMA 事务时被硬件禁用。

Continuous Mode (DMA channel CHCFGR.CHMODE = 1B)

nDMA 硬件请求在完成 DMA 事务时未被硬件禁用。

Single Mode

Single模式下硬件控制的一次完整的DMA事务(DMA Transaction)需要完成以下的DMA 通道配置:

. DMA channel CHCFGR.CHMODE = 0B

. DMA channel CHCFGR.RROAT = 1B

. DMA channel CHCFGR.PRSEL = 0B

. DMA channel TSR.ECH = 1B

将 DMA 通道 TSR.ECH 设置为 1B 将启用 DMA 通道的 DMA 硬件请求 (TSR.HTRE = 1B)。当 ICU (Interrupt Control Unit)生成 DMA 硬件请求时, TSR.CH 设置为高。 如果 DMA 通道赢得通道仲裁,则 DMA 通道将过渡到激活状态(Active State)。 CHCFGR.TREL 的值加载到 ME CHSR.TCOUNT 中, DMA 事务(Transaction)通过执行第一个 DMA 传输(Transfer)来启动。 每次 DMA 传输后, ME CHSR.TCOUNT 都会递减,并计算下一个源地址和目标地址。当 TCOUNT 减至 0D 时, DMA Hardware Request (DMA 硬件请求) 被禁用,状态标志 TSR.CH 和 TSR.HTRE 被重置。为了启动新的硬件控制的 DMA 事务,必须通过软件写入 TSR.ECH = 1B 再次启用 DMA 硬件请求以设置TSR.HTRE。在下一个 DMA 硬件请求启动 DMA 事务之前,通常需要在单模式下使用硬件请求禁用功能对 DMRAM 信道 TCS 进行重新编程。

Single模式下软件控制的一次DMA传输(DMA Transfer)需要完成以下的DMA 通道配置:

. DMA channel TSR.ECH = 0B

在此 DMA 通道配置中,在每次 DMA 传输开始时都清除了 TSR.CH ,必须生成新的 DMA 硬件请求才能启动下一次 DMA 传输。

Continuous Mode

如果 DMA 通道配置为连续模式 (HCFGR.CHMODE = 1B) ,则 TSR.HTRE 不会在 DMA 事务结束时重置。在完成当前 DMA 事务 (ME CHSR.TCOUNT = 0D) 后,每个新的 DMA 硬件请求都将启动与存储的 DMA 通道 TCS 的新 DMA 事务。

6.4 DMA软件和硬件组合请求

DMA 通道可以在软件和硬件的组合控制下运行。如下示例 显示了组合控制:

•第一个 DMA 传输由 DMA 软件请求触发,该请求将 DMA 通道 CHCSR.SCH 设置为 1B。

• DMA 硬件请求仍被禁用,即 DMA 通道 TSR.HTRE =0B。

•软件通过设置 DMA 通道 TSR.ECH = 1B 来启用 DMA 硬件请求。

•随后的每次 DMA 传输都由 ICU 发出的 DMA 硬件请求触发。

在本例中, DMA 通道以单模式运行 (DMA 通道 CHCFGR.CHMODE = 0B)。在单模式下,当 ME CHSR.TCOUNT = 0D (DMA 事务结束时) 时, DMA 通道 TSR.HTRE 由硬件重置。

如果 DMA 软件请求和 DMA 硬件请求在同一时钟周期内发生冲突,则应标记 TRL 事件。

6.5 DMA菊花链请求

DMA 通道应通过设置 DMA 通道 CHCFGR.PRSEL 来配置 DMA 菊花链请求。

当高优先级 DMA 通道完成 DMA 事务时,它将通过设置访问挂起位 TSR.CH 位在下一个低优先级 DMA 通道中启动 DMA 事务。DMA 菊花链请求仅限于在下一个较低优先级 DMA 通道中发起 DMA 请求的较高优先级 DMA 通道。

启用菊花链会禁用下一个高优先级 DMA 通道中的 DMA 通道中断服务请求触发器。在典型的 DMA 菊花链应用程序中,只有最低优先级的 DMA 通道才能生成 DMA 通道中断服务请求。当从最高优先级到最低优先级 DMA 通道的 DMA 事务序列完成后,菊花链中的最低优先级 DMA 通道将生成 DMA 通道中断服务请求,以发出 DMA 操作结束的信号。

如果 DMA 通道是在菊花链中配置的,则 DMA 软件请求或 DMA 硬件请求将启动优先级最高的 DMA 通道中的 DMA 传输或 DMA 事务。低优先级 DMA 通道中的 DMA 事务由 DMA 菊花链请求触发,以提高 DMA 延迟。

6.6 DMA通道传输请求丢失中断服务请求

DMA通道TRL (Transaction Request Lost Interrupt) 事件在以下情况会发生:

如果检测到 DMA 请求并设置了 DMA 通道 TSR.CH ,则 DMA 通道应设置 DMA 通道 TRL 位 (TSR.TRL = 1B)。如果设置了 DMA 通道启用 TRL 位 (TSR.ETRL = 1B) , DMA 将触发 DMA RP 错误中断服务请求。

如果 DMA 通道的硬件请求被禁用,却检测到 DMA 硬件请求, DMA 应设置 DMA 通道 TRL 位 (TSR.TRL = 1B) 并触发 DMA RP 错误中断服务请求。

错误处理程序应查询 DMA 通道以确定错误的来源。软件可以通过设置 DMA 通道 TSR.CTL 或 TSR.RST 来清除 TSR.TRL。

6.7 DMA服务请求

中断请求由中断路由优先处理,并由其中一个服务提供者 (CPU 或 DMA) 处理。DMA 到中断控制单元 (ICU) 的接口在中断路由 (IR) 中实例化。

DMA 通道与服务请求控制 (SRC) 寄存器 SRC.SRPN 中编程的服务请求优先级编号 (SRPN) 位字段相关联。例如:

. DMA channel 000 equates to SRC.SRPN = 0D programmed in IR.

. DMA channel 001 equates to SRC.SRPN = 1D programmed in IR.

. DMA channel 002 equates to SRC.SPRN = 2D programmed in IR.

. DMA channel 003 equates to SRC.SRPN = 3D programmed in IR.

. DMA channel 004 equates to SRC.SPRN = 4D programmed in IR.

硬件服务请求到服务提供者目标的路由取决于 IR 服务类型 (TOS) 控制位字段 SRC.TOS。DMA 将确认所有服务请求。如果在 SRC.SRPN 中设定的值用于无效的 DMA 通道,则 DMA 将不会采取任何措施。用户必须为 DMA 编程有效的 SRC.SRPN 值。

6.8 DMA请求仲裁

当 DMA 通道未处于“halt ”状态 (TSR. HLTREQ = 1B) 和 / 或 “suspend” 状态 (SUSASS.SUSAC = 1B) 时, DMA 仲裁程序会持续监视所有 DMA 通道是否存在挂起的 DMA 请求。

所有挂起的DMA Request中最高数字的DMA Channel将会赢得DMA通道仲裁。挂起的DMA请求中最大通道数的请求被转发到可用ME。ME从DMARAM读取DMA通道TCS,并将TCS加载到ME活动通道寄存器组中,并执行DMA传输。在每次DMA传输完成时,DMA执行仲裁序列。

仲裁序列如下:

6.9 DMA通道复位

软件应通过设置 DMA 通道重置位 (TSR.RST = 1B) 来重置单个 DMA 通道。当 DMA 通道重置应用到 DMA 通道时,过渡到重置状态 (TSR.RST =0B) 如下:

处于Idle状态和Pending状态时:DMA通道将会立即切换到Reset状态。

处于Active状态时:完成当前的DMA传输后,DMA通道再切换到Reset状态。

Reset State

完成 DMA 通道重置后, DMA 通道将进入重置状态,定义为:

以下的DMA通道相关寄存器的bit将会Reset:

– DMA Transaction State Register: TSR.HLTREQ, TSR.HLTACK, TSR.HTRE, TSR.CH and TSR.TRL.

– DMARAM TCS: CHCFGR.PRSEL, CHCSR.ICH, CHCSR.IPM, CHCSR.WRPD, CHCSR.WRPS, CHCSR.FROZEN,

CHCSR.BUFFER, CHCSR.LXO and CHCHSR.TCOUNT.

如果为 DMA 通道启用了循环缓冲器 ADICR.SCBE 和 / 或 ADICR.DCBE ,则源和 / 或目标地址寄存器将设置为环绕边界,否则地址寄存器将被清除。

DMA 通道阴影地址寄存器 (SHADR) 应被清除。

Resetting a DMA Channel

用户程序需要执行以下步骤来复位DMA Channel:

1.如果使能了DMA Hardware Request则需要Disable hardware requestes(TSR.DCH = 1B).

2.软件请求 DMA通道复位(TSR.RST = 1B)。

3. 软件应监控 DMA 通道重置以及 DMA 通道 SADR , DADR 和 SHADR 寄存器。

4. DMA 清除 DMA 通道重置 (TSR.RST = 0B) 且 DMA 已重置 DMA 通道 SADR , DADR 和 SHADR 寄存器后, DMA 通道重置就已完成。

在DMA通道重置期间,一定不要设置DMA软件请求(CHCSR.SCH = 1B)。

Restarting a DMA Channel

用户程序需要执行以下步骤来重新启动DMA Channel:

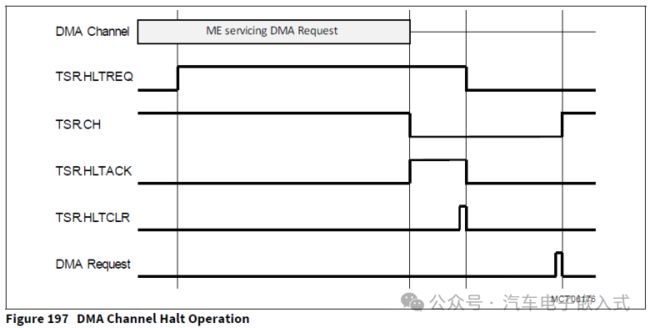

6.10 DMA通道Halt

DMA 通道可能在 DMA 事务期间停止,状态为 “冻结-frozen”,以便在目标内存上运行后台 RAM 测试,以检测卡住的位并区分静态错误和瞬态错误。完成 RAM 测试后, DMA 通道可能会重新启动并完成 DMA 事务。

DMA 通道中断逻辑 利用一个设置 / 清除机制,在完成当前 DMA 传输时请求 DMA 通道与停止状态之间的转换。只有写入逻辑 ‘1 ’以设置或清除 DMA 通道的暂停请求 才会生效。其他 DMA 通道的状态应被忽略。

Halt State

配置DMA 通道 TSR. HLTCK = 1B 时,DMA通道将处于暂停状态。

Entering DMA Channel Halt

通过写入 DMA 通道halt请求位 (TSR. HLTREQ = 1B) 来配置DMA 通道进入halt状态。 DMA 通道按如下所示进入暂停状态:

处于Idle状态,Reset状态和Pending状态时:DMA通道将会立即切换到Halt状态。

处于Active状态时:完成当前的DMA传输后,DMA通道再切换到Halt状态。

Exiting DMA Channel Halt

DMA 通道通过写入 DMA 通道 halt清除 位 (TSR. HTCLR = 1B) 是的DMA通道从 HALT 状态释放。DMA 操作将会恢复。如果在确认停止请求之前清除了该请求,则不会对 DMA 操作产生影响。

DMA Channel Hardware Request during DMA Channel Halt

如果 DMA 通道处于暂停状态且硬件事务请求已启用 (TSR. HTRE = 1B) ,则 DMA 通道将响应 DMA 硬件请求,如下所示:

•无 DMA 请求挂起 (TSR.CH = 0B) :DMA 通道应设置访问挂起位 (TSR.CH = 1B)。DMA 通道退出 “HALT” 状态时,应处理 DMA 硬件请求。

• DMA 请求挂起 (TSR.CH = 1B) :DMA 通道应记录 TRL 事件。如果设置了 DMA 通道 TRL 启用位 (TSR.ETRL = 1B) ,则 DMA 将触发 DMA RP 错误中断服务请求。

7. DMA随机访问内存

软件在 DMRAM 中存储 DMA 通道 TCS ,以定义每个 DMA 通道的Move功能。

对于TCS(Transaction Control Set)的理解:WORD0: RDCRCR[0], WORD1: SDCRCR[0], WORD2: SADR[0], WORD3: DADR[0], WORD4: ADICR[0], WORD5: CHCFGR[0], WORD6: SHADR[0], WORD7: CHCSR[0]这七个寄存器就是一个TCS[0], 总共可以配置32组这样的7个寄存器合集就是TCS.

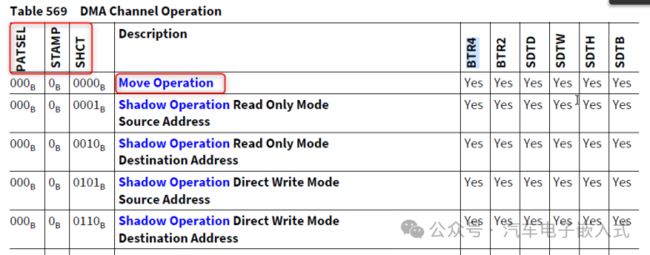

7.1 DMA通道操作

DMALRAM TCS 定义了 DMA 通道操作的类型以及芯片总线访问支持的大小。

CHCFGR. PATSEL

ADICR.STAMP

ADICR.SHCT

以上三个寄存器位域的组合能确定一个DMA Channel Operation.

7.2 DMA通道更新

只有当 DMA 通道处于Idle状态 (DMA 通道 HCSR.TCOUNT=0D) 或Reset状态时,软件才应配置 DMRAM 通道 TCS. 如果 DMA 通道处于Idle状态 (DMA 通道CHCSR.TCOUNT!=0D) ,Pending状态或Active状态,软件将不会更新 DMARAM 通道 TCS. Shadow Operations和Double Buffering Operations下的通道更新比较特殊,具体可参考手册。

7.3 DMA通道重新配置

如果要配置 DMA 通道,软件应该通过 DMA 通道重置(DMA Channel Reset)来初始化 DMA 通道。

DMA 通道进入重置状态后,软件应配置 DMA 通道以执行 DMA 操作。

7.4 Move操作

DMA moves的数目通过以下方式计算得出:

. Block Mode (CHCFGR.BLKM) 定义了一次DMA Transfer中包含的DMA moves数目。

. Transfer Reload (CHCFGR.TREL) 定义了一次DMA transaction中包含的DMA transfer数目。

一次DMA move后,将计算下一个源地址和目标地址。 源地址和目标地址是相互独立计算的。 可以选择以下地址计算参数:

. 地址偏移量,是所选数据宽度的倍数。

. 便宜方向:addition, subtraction, or none (unchanged address).

7.4.1 地址计算

地址控制位 (在 DMA 通道 的ADICR寄存器 中) 决定地址的递增或递减方式。数据宽度在 CHCFGR.CHDW 中定义,地址计算会参考该配置项。如下表所示,地址偏移计算表显示了每次 DMA 移动后添加或减去源地址 (SMF 和 INC S参数) 和目标地址 (DMF 和 INCD 参数) 的偏移值。

注意:

CHCFGR.CHDW = 000B,也就是每次move数据宽度是8bit,也就是1个字节,那么source/destinaion地址增加/减少的最小数据长度为1个字节(8bit)。

CHCFGR.CHDW = 001B,也就是每次move数据宽度是16bit,也就是2个字节,那么source/destinaion地址增加/减少的最小数据长度为2个字节(16bit)。

以此类推……

7.4.2 地址计算示例

以下示例演示了 16 位数据宽度的地址生成 (CHCFGR.CHDW = 001B) :

Programmable Address Generation - Example 1

16 位半字数据从源内存 (源地址偏移量增加为 10H) 移动到目标内存 (目标地址偏移量减少为 08H) 。

CHCFGR.CHDW = 001B

CHCFGR.CHDW = 001B :也就是数据宽度最大是16bit,也就是半字(一个字word,为4个字节),也就是2个字节。

ADICR.SMF = 011B :也就是每次源数据发生move后,源地址增加/减小16个字节。

ADICR.INCS = 1B :也就是也就是每次源数据发生move后,源地址往地址数大的方向加。

ADICR.DMF = 010B :也就是每次目的数据发生move后,目的地址增加/减小8个字节。

ADICR.INCD = 0B :也就是也就是每次目的数据发生move后,源地址往地址数小的方向加。

上图,第一次是Source Memory:D0 -》 move到 Destination Memory : D0 -》 Source Memory:D0 + 16个字节到D1, Destination Memory : D0 + 8个字节到D1 -》 第二次Source Memory:D1 à move到 Destination Memory : D1.

按照我们常规的思路:每次数据拷贝2字节,原地址和目的地址都往地址增加的方向增加,且源地址和目的地址都紧挨着偏移,那么应该配置:

CHCFGR.CHDW = 001B

ADICR.SMF = 000B

ADICR.INCS = 1B

ADICR.DMF = 000B

ADICR.INCD = 1B

Programmable Address Generation - Example 2

16 位半字将从源内存 (增量源地址偏移为 02H) 移动到目标内存 (增量目标地址偏移为 04H) 。

7.4.3 循环Buffer

源循环缓冲区和目标循环缓冲区通过分别设置 DMA 通道循环缓冲区启用位 ADICR.SCBE 和 ADICR.DCBE 来启用。可以将源地址和目标地址配置为单独为源数据和目标数据构建循环缓冲区。在循环缓冲区内,地址将在循环缓冲区环绕限制内更新。圆形缓冲区长度由位字段 ADICR.CBLS (用于源缓冲区) 和 ADICR.CBLD (用于目标缓冲区) 决定。这些 4 位宽位字段决定了 32 位地址中哪些位在地址更新期间保持不变。循环缓冲区的可能缓冲区大小可以是 2CBLS 或 2 CBLD 字节 (= 1 , 2 , 4 , 8 , 16 , … 最多 64k 字节)。源地址和目标地址在 DMA 移动过程中递增或递减,源地址的所有上位 [31:CBLS] 和目标地址的 [31:CBLD] 都被冻结,并且保持不变,即使发生了来自下位地址位 [CBLS-1 :0] 或 [CBLD-1 :0] 的换行。此地址冻结机制始终会使循环缓冲区与大小的多个整数值对齐。如果循环缓冲区大小小于或等于所选地址偏移,则将始终访问相同的循环缓冲区地址。

7.4.4 地址对齐

DMA 应符合 SRI 总线协议。所有源地址和目标地址都应与通道数据宽度 (CHCFGR.CHDW ) 定义的正确地址边界对齐,如下所示:

. Single transfers: 源地址和目标地址边界应与信道数据宽度 (字节,半字,字或双字) 一致。

. Block transfers: 源地址和目标地址边界应与双字边界对齐。 SRI 总线协议定义了块传输的环绕寻址方案(wrap around addressing scheme),该方案不是以块传输大小的起始地址开始的。 BTR2 (图 202) 和 BTR4 (图 203) 的不同情形表明了对 DMA 事务的影响。

TREL

BLKM

CHDW

1次Transactions包含1个Transfers(TREL== 0001H), 每个Transfer包含4个moves(BLKM == 002H),每个move的数据宽度是128bit(CHDW = 100B)。

1次Transactions包含1个Transfers(TREL== 0001H), 每个Transfer包含2个moves(BLKM == 001H),每个move的数据宽度是256bit(CHDW = 101B)。

7.4.5 地址计数器

如果未启用源 / 目标循环缓冲器 (ADICR.SCBE/DCBE =0B) ,则源 / 目标地址将在整个 32 位地址字段中递增或递减。地址偏移由 DMA 通道 CHCFGR.CHDW 决定。该地址将在 32 位地址边界上环绕(wrap around):

•如果地址递增,则将从 FFFFFFFFH 换为 00000000.

•如果地址正在递减,则将从 00000000 行话换为 FFFFFFFFH.

7.4.6 DMA地址Checksum

DMA 应根据 IEEE 802.3 标准计算 SDCRC 校验和,并将提供给芯片总线上的源地址和目标地址作为输入数据。软件应将计算出的 DMA 地址校验和 (SDCRC) 与存储在内存中的预期 DMA 地址校验和进行比较,以在 DMA 事务期间验证地址生成。要检查 DMA 通道地址生成,请执行以下步骤:

7.4.7 DMA通道中断服务请求

每个DMA通道能产生以下三个中断服务请求:

. DMA Channel Transfer Interrupt Service Request

. DMA Channel Pattern Match Interrupt Service Request

. DMA Channel Wrap Buffer Interrupt Service Request

7.4.8 DMA传输中断服务请求

如果 DMA 通道处于“Active”状态,则 DMA 通道传输中断服务请求可能在完成 DMA 传输时被激活,或者当 ME CHSR.TCOUNT 与位字段 ADICR.IRDV 的值匹配 (在 DMA 传输后减小) 时被激活。设置状态标志 CSR.ICH 时,将指示来自 DMA 通道的中断服务请求。状态标志应通过软件设置 DMA 通道CHCSR.CICH = 1B (或 TSR.RST = 1B) 来重置。设置 DMA 通道 ADICR.INTCT[1] 后, DMA 通道中断服务请求将被启用。

位 ADICR.INTCN[0] 选择两种类型的中断源之一。对于比较操作,位字段 ADICR.IRDV (4 位) 为零扩展到 14 位,然后与 14 位 TCOUNT 值进行比较。这意味着,在 DMA 事务的最后 16 次 DMA 传输之一之后,可能会生成 TCOUNT 匹配中断。请注意,在 IRDV = 0000B 的情况下,匹配中断在 DMA 事务结束时 (在上次 DMA 传输后) 生成。

DMA Channel Pattern Match Interrupt Service Request

DMA Channel Wrap Buffer Interrupt Service Request

这两个中断服务请求用的不多,需要的时候参考芯片手册。

7.8. 阴影操作Shadow Operation

如果为阴影操作配置了 DMA 通道, DMA 缓冲可变源地址或目标地址。

在典型应用中,接收数据 (固定 DMA 通道源地址) 的 ASC 模块必须使用 DMA 事务 (可变 DMA 通道目标地址) 将数据传送到内存缓冲区。传输一定数量的数据后,应启动新的 DMA 事务,以将更多的 ASC 数据传输到另一个内存缓冲区。当目标地址寄存器在实际目标地址的 DMA 事务期间更新时,影子机制允许对新目标地址进行编程,而不会干扰目标地址寄存器的内容。在这种情况下,新的目标地址将被写入并缓冲到影子地址寄存器中。在下一个 DMA 事务开始时,目标地址寄存器应使用新地址,而无需 CPU 干预。阴影操作避免了 CPU 在重新编程地址寄存器之前必须检查 DMA 事务的结束。

注意:Shadow Operation使用不多,了解下其使用场景即可,需要时再深入学习。

7.9. DMA时间戳

最后一个 DMA 传输完成后,可能会附加一个 32 位 DMA 时间戳以记录 DMA 操作的发生。DMA 时间戳是 DMA 记录事件的时间,而不是实时。DMA 事务在 DMA 时间戳写入后完成。

Appendage of DMA Timestamp - Example

16 位半字将从源内存 (增量源地址偏移为 02h) 移动到目标内存 (递减目标地址偏移为 04h)

注意:DMA时间戳也基本不用,了解即可,需要时再深入学习。

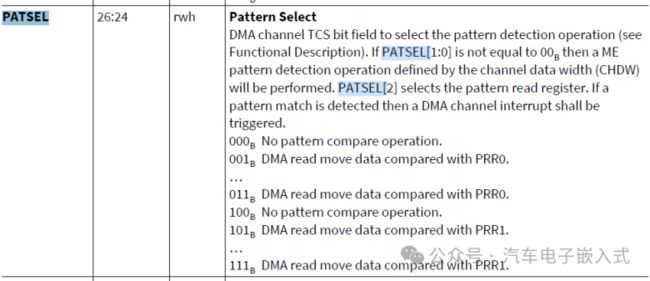

7.10. Pattern检测

如果为DMA 通道配置了PATDET,则在每次 DMA 读取移动后, ME 会将移动数据与存储在模式读取寄存器 (PRR) 中的值进行比较。PATDET 操作取决于信道数据宽度 (CHCFGR.CHDW) 。 控制字段 CHCFGR.PATSEL 为 CHDW 的特定值选择不同的 PATDET 操作。

模式比较逻辑将存储在 ME 读取寄存器中的移动数据与选定的 PRR 进行比较。如果要比较的移动数据字节分布在移动数据的不同字中, ME 可能会将当前 DMA 移动的模式匹配结果与上一 DMA 移动的模式匹配结果 (存储在 ME CHSR.LXO 中) 结合起来。

注意:Pattern检测也基本不用,了解即可,需要时再深入学习。

7.11. 双Buffering操作

DMA 支持双缓冲。例如,双目标缓冲区 (图 213) 如下所示:

• DMA 读取将连续数据流从外围设备传输到 DMA。

• DMA 写入将读取数据从 DMA 传输到存储在内存中的两个目标缓冲区之一。

休眠缓冲区(dormant buffer)已冻结(frozen),可用于循环软件任务,而另一个缓冲区仍在填充。

如果为其中一个双缓冲操作配置了 DMA 通道,且该通道由 DMA 硬件请求触发,则软件应将 DMA 通道配置为连续模式 (DMA 通道 HCFGR.CHMODE = 1B)。

注意:双缓冲也基本不用,了解即可,需要时再深入学习。

7.12. Linked List操作

链表操作是 DMA 通道功能的扩展,可支持 DMA 更灵活的使用。链表操作应包含由同一 DMA 通道执行的一系列 DMA 事务。每个 DMA 事务都应具有唯一的 TCS。源和目标区域不必存在于内存的连续区域中。

如果为链表操作配置了 DMA 通道,则在 ME 完成当前 DMA 事务后, ME 将从内存中读取下一个 TCS ,并覆盖 DMRAM 中 DMA 通道位置的当前 TCS。当前 DMA 事务使用 32 字节对齐地址指针指向存储在内部或外部内存中的下一个 TCS。DMA 应从 0 开始读取下一个 TCS。链表操作中的 DMA 事务数没有限制。链表操作中的第一个 DMA 事务应由 DMA 硬件请求或 DMA 软件请求启动。随后的 DMA 事务也可能由 DMA 自动启动请求启动。

每个 DMA 通道都支持以下类型的链接列表操作:

. DMA Linked List (DMALL)

. Accumulated Linked List (ACCLL)

. Safe Linked List (SAFLL)

. Conditional Linked List (CONLL)

注意:链表操作也基本不用,了解即可,需要时再深入学习。

8. Move Engine

任何ME都应该为来自任何 DMA 通道的 DMA 请求提供服务。一旦 DMA 通道赢得仲裁, TCS 就会从 DMALRAM 复制到 ME 活动通道寄存器,并处理 DMA 请求。ME 请求所需的总线,并根据活动 DMA 通道的 TCS 参数加载或存储数据。如果源或目标不可用, ME 可以等待。

ME 对 DMA 传输 (由多个 DMA 移动组成) 的处理不能中断,并且始终完成。只有在当前 DMA 传输完成后, DMA 通道中断,重置,停止请求或调试挂起才会激活。报告了错误情况。完成 DMA 事务或 DMA 通道失去信道仲裁时,ME应将 TCS 写回 DMRAM。

9. DMA配置

如果理解了上文所述的所有内容,则配置DMA就会比较容易,也就是按照项目的需求来配置芯片的特性。

9.1 DMA General Config

Dma General里面定义的基本都是一些API和功能是否使能,其中需要注意的是DmaMaxTransactionSetPerChannel这个参数,定义了每个Dma Channel最多可以配置多少个TCS,按照个人理解,常规的DMA应用只需要配置一个TCS就行,不需要运行时切换TCS.

9.2 Dma Resource Partition Config

每个TC3xx芯片支持的RP数量不一样,对于TC37x芯片,做多支持4个RP.

每个RP有自己的Access Enable Protection. ACCEN寄存器的32个bit每一位都代表一个Bus Master (CPU0, CPU1…) 是否对该RP有访问权限,如果32个Bus Master对齐都具有访问权限,则配置为0xFFFF FFFF.

9.3 Dma Channel Config

DmaChannelId : 指定使用DMA的哪一路Channel(TC37x系列工128路Channel)。值得注意的是,在IR(Interrupt Router)模块的SRC寄存器中的SRPN的值在中断功能中是中断优先级的配置,在DMA功能中是DM Channel Number的值。在AUTOSAR OS的ISR配置中选用了DMA,则中断优先级(ISR interrupt priority)的值必须等于使用的DMA Channel的Number号。

DmaChannelAssignedPartition: 指定分配到哪一个RP.

DmaChannelNumTransactionSet: 指定改Channel有多少的Transaction Control Set (TCS).

其他配置都容易理解。

DmaChannelTransactionSet的配置基本就是对第七章中寄存器值的配置了,这里仅举例说明几个。

DmaTcsMoveLength: 配置CHCFGR.CHDW, 也就是一次move的数据长度。

DmaTcsTransferLength: 配置CHCFGR.BLKM, 也就是一个Transfer包好几个moves.

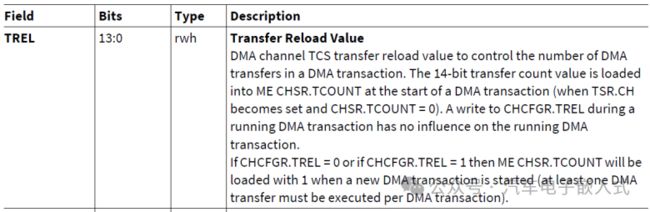

DmaTcsTransactionLength: 配置CHCFGR.TREL, 也就是一个Transaction包含几个Transfer.

10. DMA代码使用分析

如果我们要使用一个DMA Channel:

1)软件触发

2)结束后产生中断

第1步:Dma初始化

extern void Dma_Init(const Dma_ConfigType* const ConfigPtr);

第2步:配置源地址和目的地址

extern void Dma_ChUpdate(const uint8 Channel,const Dma_ConfigUpdateType* const Config,const uint32* const NodeAddress);

第3步:使能DMA中断

extern void Dma_ChInterruptEnable(const uint8 Channel,const Dma_EventsType Event);

第4步:软件请求DMA传输

extern void Dma_ChStartTransfer(const uint8 Channel);

注意:

因为使用了DMA中断,则在OS的ISR中需要配置DMA中断,且如果OS没有实现DMA的二类中断,则还需要我们实现DMA的二类中断,在DMA中断中调用:

extern void Dma_ChInterruptHandler(const uint8 Channel);ISR(SRC_DMAChannel99){Dma_ChInterruptHandler(99u);}

11.总结

直接内存访问也就是DMA(Direct memory access)能够不使用CPU完成数据从一个内存地址到另一个内存地址的搬运 ,从而降低CPU的负载,将有限的CPU资源用于更重要紧急的事务。但具体到一块芯片的DMA使用时,我们首先要考虑DMA通用的知识,如DMA使用的时钟,DAM中断,具体完成一次DMA传输时,具体芯片如何完成DMA的目的地址、源地址的设置,DMA的软件和硬件触发等。然后就是具体芯片如TC3xx芯片中DMA Transaction, DMA Transfers, DMA moves, DMA数据宽度配置,DMA传输控制集等概念的具体含义,然后由这些基本概念来完成具体芯片的一次DMA数据传输。