STM32 GPIO

GPIO(General Purpose Input Output)通用输入输出口

·可配置为8种输入输出模式

·引脚电平:0V~3.3V,部分引脚可容忍5V(FT)

·输出模式下可控制端口输出高低电平,用以驱动LED、控制蜂鸣器、模拟通信协议输出时序等

·输入模式下可读取端口的高低电平或电压,用于读取按键输入、外接模块电平信号输入、ADC电压采集、模拟通信协议接收数据等

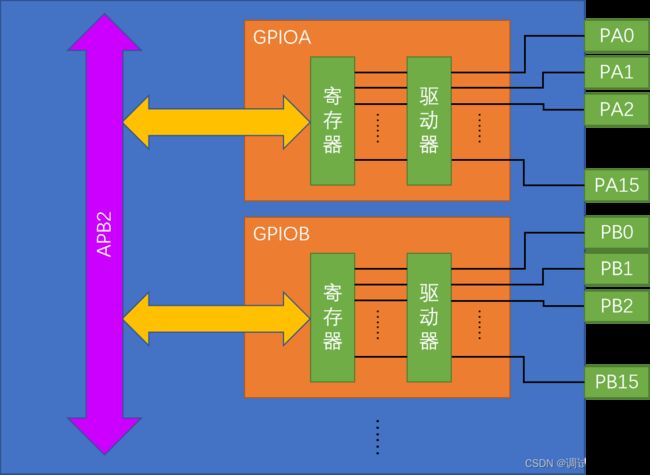

GPIO基本结构

由上图1.1,我们可以清晰地知道,GPIO若干个端口GPIOX(X=A|B|C.......)均连接在APB2总线上。 对应的引脚 从 0~15

寄存器32位,而引脚只有16个,所以寄存器只有低16位的对应有端口

GPIO位结构(寄存器+驱动器+端口)

图2.1

保护二极管

若输入电压A>VDD+Vf(二极管导通电压),上方二极管导通,电流会流向VDD而不流入内部电路。B点电压稳定在VDD+Vf(B后面相当于和上面的电路并联)

若输入电压A<-Vf,电流会从VSS流出,而不会从内部汲取

我们介绍一下二极管的钳位作用:

图2.2

可以发现无论电路中串联的阻值怎么变化,二极管总把电压钳制在0.7V按照中学学过的欧姆定律,我们可以知道,两个并联的100欧的电阻均分5V电压,但是将另一个100欧姆电阻和二极管并联起来呢?是0.7V还是2.5V?

图2.3

实验检测是0.7V左右。

理解:

1.二极管正向导通电阻较小,并联后的等效电阻会无限接近于小的电阻,于是,分压接近0.7V

2.二极管电阻小,电流倾向于通过电阻小的地方,大电阻被“短路”,电压降近似为0.7V

3.从二极管的伏安特性曲线入手:

图2.4

0.7V附近是拐点,小于这个值二极管截止,大于这个值,导通。

钳位电压不是固定在0.7 是在0~1之间浮动

而二极管想获得更大的分压,电流也要足够大,上面的图2.2,似乎二极管分压可以大于0.7V但是电流计算下来很小也就不行了

输入

我们继续看图2.1输入的部分 信号输入后有上下拉电阻,作用是提供默认、稳定的输入电平:上拉(高电平)输入、下拉(低电平)输入、浮空输入(易受外界干扰,不稳定)

| 优点 | 缺点 | |

| 阻值大 | 漏电流小 | 驱动能力弱 |

| 阻值小 | 驱动能力强 | 漏电流大 |

TTL肖特基触发器(理解为用肖特基管构成的施密特触发器??) ??滞回比较器 模电

作用:对输入电压进行整形,0|1的逻辑

红线为假设输入波形,绿线为上下阈值,蓝线为输出波形

这样一来,输出信号实现了二值化

模拟输入接到TTL前面,因为接受模拟量(随时间不断变化)

数字输入接到后面(二值逻辑)

输出

选择输出数据寄存器(只用低16位)--->普通IO口输出 位操作就可以操作对应的端口了

位设置/清除寄存器--->单独操作输出数据寄存器的某一位而不影响其他位 因为这个寄存器能同时控制16个端口,并且只能整体读写。

如果想控制某一个端口而不影响其他端口

第一个方法是先读出这个寄存器,然后用按位与和按位或的方式更改某一位,最后再将更 的数据写回去。但是这个方法效率不高

(*)第二个方法是设置位设置和位清除寄存器(高16位位清除,低16位位设置) 若对某一位置一操作,在位设置寄存器对应位置写1,其他位置写0。 若想对某一位清零,就在位清除寄存器的对应位写1即可。

PS:位清除寄存器(低16位清除)和上面的高16位效果一样。

这个寄存器的作用:方便,搭配上面的寄存器只使用低16位数据就可以完成设置清除工作

而要对多个端口同时位设置位清除,只使用上面的寄存器,保证信息同步性

第三个方法是读写“位带”区域

输出模式

| Q1 | Q2 | OUTPUT | |

| 1 | 导通 | 不导通 | 高电平 |

| 2 | 不导通 | 导通 | 低电平 |

| 3 | 不导通 | 不导通 | 浮空/高阻态 |

| 4 | 导通 | 导通 | MOS管烧毁 |

1&2:推挽输出

-->高电平时“推”电流出去,给MOS管充电;低电平时“挽”电流进来,MOS管放电

?? 数据寄存器为1时,上管导通,下管断开,输出直接接到VDD,也就是输出高电平

数据寄存器为0时,上管断开,下导通,输出直接接到VSS,也就是输出低电平

无论高低电平均有较强驱动能力,所以推挽输出模式又叫强推输出模式

2&3:开漏输出(多机通信时,避免各个设备的相互干扰)

-->上面的MOS管永远关闭,下面的MOS管的漏极相当于开路。

当数据寄存器为1,下管断开,高阻模式

当数据寄存器为0,下管道导通,有“漏”电流

只有低电平才有驱动能力

输入模式下输出无效,输出模式下输入有效:一个端口只能一个输出可以多个输入