第16章 嵌入式系统架构设计理论与实践

16.1 嵌入式系统概述

16.1.1 嵌入式系统发展历程

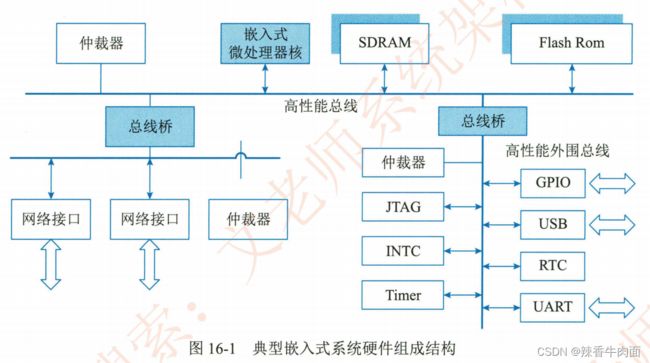

16.1.2 嵌入式系统硬件体系结构

嵌入式系统毕竟也是操作系统的一种,有其特殊性也有操作系统的通用性,所以可结合操作系统基础知识学习。

1.嵌入式微处理器

微处理器主要用于处理相关任务。根据使用环境的不同选用不用级别的芯片,比如温度、湿度、震动、抗磁、加速度等等。主要是温度,民用级0~70℃,工业级-40~85℃,军用级-55~150℃。

嵌入式微处理分类:

1.根据嵌入式微处理器的字长宽度,可分为4位、8位、16位、32位和64位。一般把16位及以下的称为嵌入式微控制器(Embedded Micro Controller),32位及以上的称为嵌入式微处理器。

2.如果按系统集成度划分,可分为两类:

- 一种是微处理器内部仅包含单纯的中央处理器单元,称为一般用途型微处理器。

- 另一种则是将CPU、ROM、RAM及I/O等部件集成到同一个芯片上,称为单芯片微控制器(Single Chip Microcontroller)。

3.通常根据使用场景不同选择不同类型的处理器,分类:

1).微处理器(MPU)

将微处理器装配在专门设计的电路板上,只保留与嵌入式应用有关的母版功能。

优点:与工业计算机相比,体积小,重量轻,成本低及可靠性高

缺点:因为电路板上必须包括ROM、RAM、总线接口、各种外设等器件,降低了系统的可靠性,技术保密性差。

目前代表有:Am186/88、386EX、SC-400、PowerPC、68000、 MIPS、ARM系列等。

2).微控制器(MCU)

每种衍生产品的处理器内核都是一样的,不同的是存储器和外设的配置和封装。MCU又叫单片机,是以微处理内核为核心的。它其实是把微处理内核和一些存储器、外设等等都集成在一块硅片上,所以叫单片机。

它是由通用计算机演变而来。

特征:是具有32位以上的处理器,具有较高的性能,当然其价格也相应较高。

比较:

- 但与计算机处理器不同的是,在实际嵌入式应用中,只保留和嵌入式应用紧密相关的功能硬件,去除其他的冗余功能部分,这样就以最低的功耗和资源实现嵌入式应用的特殊要求。

- 与工业控制计算机相比,嵌入式微处理器具有体积小、重量轻、成本低、可靠性高的优点。

优点:与MPU相比,MCU的最大优点在于单片化,体积大大减小,从而使功耗和成本下降,可靠性提高。

目前代表有:

3).信号处理器(DSP)

嵌入式数字信号处理器DSP是专门用于信号处理方面的处理器,其在系统结构和指令算法方面进行了特殊设计,具有很高的编译效率和指令的执行速度。采用哈佛结构,流水线处理,其处理速度比最快的CPU还快10-50倍。在数字滤波、FFT、谱分析等各种仪器上DSP获得了大规模的应用。

DSP特点:

多总线结构,允许CPU同时进行指令和数据的访问,因而可以实现流水线操作。哈佛体系结构,程序和数据空间分开,可以同时访问指令和数据。数字信号处理的运算特点:乘/加,及反复相乘求和(乘积累加)。DSP设置了硬件乘法/累加器,能在单个指令周期内完成乘法/加法运算。

DSP主要应用:信号处理、图像处理,仪器、语言处理、控制、军事、通讯、医疗、家用电器等领域。

4).图形处理器(GPU)

5).片上系统(SoC)

嵌入式片上系统SOC,是追求产品系统最大包容的集成器件。

SoC最大的特点是成功实现了软硬件无缝结合,直接在处理器片内嵌入操作系统的代码模块。

是一个有专用目标的集成电路,其中包含完整系统并有嵌入软件的全部内容。

6).多核处理器、多CPU处理器

(1)基础概念

处理器/CPU是计算机的大脑,它负责计算机的所有功能。CPU 的执行单元称为核心。核心的主要功能是读取和执行指令。这些指令可以有多种形式,包括计算、数据传输、分支等。

多核指多个微处理器内核,是将两个或更多的微处理器封装在一起,集成在一个电路中。

多核处理器是单枚芯片,能够直接插入单一的处理器插槽中。

多核与多CPU相比,很好的降低了计算机系统的功耗和体积。在多核技术中,由操作系统软件进行调度,多进程,多线程并发都可以。

双核处理器:基于单个半导体的一个处理器上拥有2个处理器核心。

由于将2个或多个运算核封装在一个芯片上,节省大量晶体管、封装成本;显著提高处理器性能;兼容性好;系统升级方便。

具有单核的处理器称为Unicore处理器。但具有两个或更多核心的处理器称为多核处理器。多核处理器的核心可以同时单独读取和执行程序指令。这提高了程序的执行速度并支持并行计算

多处理器系统有两个或更多处理器。多处理器系统的处理器共享相同的内存、系统总线(连接计算机系统主要组件以传输数据和信息的路径)和I/O 设备。多处理器可以同时执行多条指令。一个处理器的故障不会影响其他处理器的功能。因此,多处理器更加可靠。

简单理解:多核处理器是,一个CPU,但是CPU里有很多各核心,多处理器是,多个CPU,每个CPU下可能是单个核心也可能是多个核心。

(2) 2个或多个内核(多处理器)工作协调实现方式:

对称多处理技术:将2颗完全一样的处理器封装在一个芯片内,达到双倍或接近双倍的处理性能,节省运算资源。

非对称处理技术:2个处理内核彼此不同,各自处理和执行特定的功能,在软件的协调下分担不同的计算任务。

从目前已经发布或透露的多核处理器原型来看,对称式的处理方式将成为未来多核处理器的主要体系体系结构,同时,多核间将共享大容量的缓存作为处理器之间及处理器与系统内存之间交换数据的“桥梁”。

为了提高交换速度,这些缓存往往集成在片内,其数据传输速度是惊人的。

(3)多核CPU的调度

多核CPU环境下进程的调度算法一般有全局队列调度和局部队列调度两种.

全局队列调度是指操作系统维护一个全局的任务等待队列,当系统中有一个CPU空闲时,操作系统就从全局任务等待队列中选取就绪任务开始执行,CPU核心利用率高。

局部队列调度是操作系统为每个CPU内核维护一个局部的任务等待队列,当系统中有一个CPU内核空闲时,就从该核心的任务等待队列中选取适当的任务执行,优点是无需在多个CPU之间切换。

(4)优缺点:

多核处理器的优点是:

- 与单核处理器相比,多核处理器可以完成更多的工作。

- 多核处理器的核心位于单个集成芯片上。结果,系统的时钟速度增加。

- 与单核处理器相比,多核处理器可以更大程度地容忍故障。

- 这些程序被分配了不同的核心,但它们仍然能够相互交互。

- 多核处理器以更低的能耗提供更高的性能,因此它们是节能的。

- 多核处理器的流量较少。

多核处理器的缺点是:

- 尽管多核处理器中存在多个核心,但与简单处理器相比,速度并没有显着提高。

- 增加核心数量会增加由于资源共享而导致的软件干扰。

- 处理器在执行多任务时会产生大量热量。

- 多核处理器的功耗较高。

多处理器系统的优点是:

- 由于多个处理器同时工作,系统的吞吐量增加。

- 多处理器系统更加可靠,因为一个处理器的故障不会影响其他处理器。

- 由于多个进程在不同的处理器上并行执行,因此实现了并行处理。

多处理器系统的缺点是:

- 多处理器系统的处理器之间的协调是相当复杂的。

- 所有处理器都使用公共 I/O 设备。因此,如果一个进程正在使用 I/O,那么其他进程必须等待轮到它。结果,系统的吞吐量可能会降低。

- 由于所有处理器都使用相同的内存,因此需要大量主内存来进行高效计算。

- 与多核系统相比,多处理器系统昂贵。

7).多核与多CPU处理器区别与联系

| 多核 | 多处理器 |

|---|---|

| 多核处理器具有一个具有多个读取和执行指令的核心的处理器。 | 多处理器具有两个或多个允许同时处理程序的处理器。 |

| 多核可以更快地执行单个程序。 | 多处理器可以更快地执行多个程序。 |

| 多核处理器不如多处理器可靠。 | 多处理器更加可靠,因为有多个处理器可用,并且一个处理器的故障不会影响其他处理器。 |

| 多核配置简单。 | 多处理器需要复杂的配置。 |

| 多核的流量较少。 | 多处理器具有更多流量。 |

| 多核很便宜,因为只有一个处理器。 | 与多核相比,多处理器价格昂贵。 |

2.存储器

1)RAM(Random Access Memory,随机存取存储器)

(1).RAM(Dynamic RAM,动态随机存取存储器)。

(2).SRAM(Static RAM,静态随机存取存储器)。

静态,指的是内存里面的数据可以长驻其中而不需要随时进行存取。每6个电子管组成一

(3).VRAM(Video RAM,视频内存)。

(4).FPM DRAM(Fast Page Mode DRAM,快速页切换模式动态随机存取存储器)。

(5).EDO DRAM(Extended Data Out DRAM,延伸数据输出动态随机存取存储器)。

(6).BEDO DRAM(Burst Extended Data Out DRAM,爆发式延伸数据输出动态随机存取存储器)。

(7).MDRAM(Multi-Bank DRAM,多插槽动态随机存取存储器)。

(8).WRAM(Window RAM,窗口随机存取存储器)。

(9).RDRAM(Rambus DRAM,高频动态随机存取存储器)。

(10).SDRAM(Synchronous DRAM,同步动态随机存取存储器)。

(11).SGRAM(Synchronous Graphics RAM,同步绘图随机存取存储器)。

(12).SB SRAM(Synchronous Burst SRAM,同步爆发式静态随机存取存储器)。

(13).PB SRAM(Pipeline Burst SRAM,管线爆发式静态随机存取存储器)。

(14).DDR SDRAM(Double Data Rate SDRAM,二倍速率同步动态随机存取存储器)。

(15).SLDRAM(Synchronize LinkDRAM,同步链环动态随机存取存储器)。

(16).CDRAM(Cached DRAM,同步缓存动态随机存取存储器)。

(17).DDRII(Double Data Rate Synchronous DRAM,第二代同步双倍速率动态随机存取存储器)。

(18).DRDRAM(Direct Rambus DRAM)。

2)ROM(Read Only Memory,只读存储器)

3.内(外)总线逻辑

- 片内总线:CPU芯片内部总线,用于连接芯片内部各个元件(如ALU、寄存器、指令部件)。

- 系统总线:计算机内部总线,它是连接计算机系统的主要组件。如用于连接CPU、主存和I/O接口的总结。系统总线又称板级总线或内部总线。

- 局部总线:计算机内部总线,通常是指在少数组件之间交换数据的总线,如CPU到北桥的总线,内存到北桥的总线,局部总线的协议一般由设备制造商定义。在体系结构较简单的计算机系统中,局部总线和系统总线为同一