DE2上SRAM测试(一)

SDRAM我是没搞定,SRAM应该没问题。。。

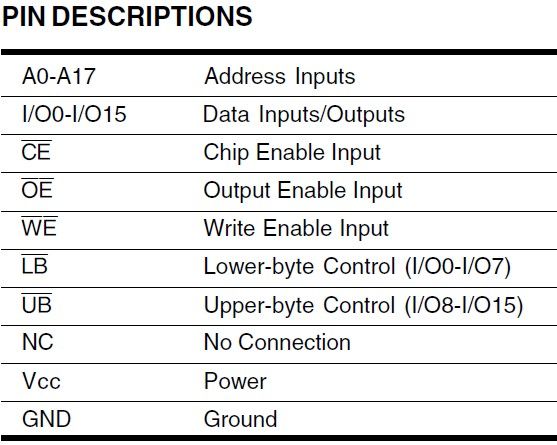

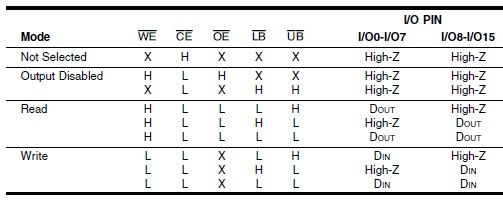

SRAM的控制很简单,DE2板子上面的是512KB的SRAM—IS61LV25616.先简单的看一下其引脚和时序图:

可以看到在一般情况下起到最重要的是WE,其他给一个默认的值就好,CE让它有效,OE让它有效,LB和UB现在也让它都有效就好。这样就少了很多事。

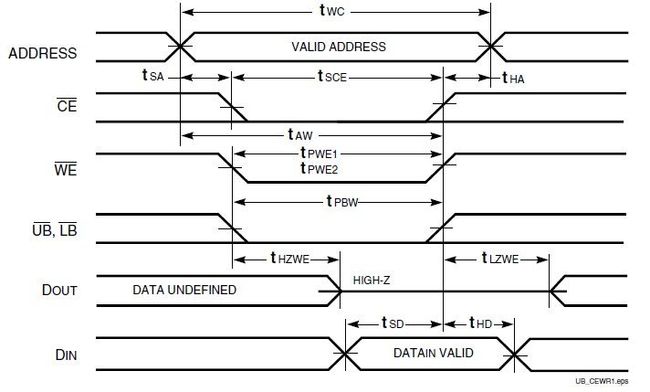

这是一个写的时序图,在前面已经省去了很多引脚,这里就简单了,先给地址,过Tsa拉低WE,同时送数据,完事后将WE拉高,数据就会被写入。在要求不太严格的情况下,三者同时进行也是可以的。这里需要注意的是数据口是双向的,要做一个三态门才行,在写的时候它选通,在读SRAM的时候它要为高阻态Z才行。读状态就更简单了,直接读就好。

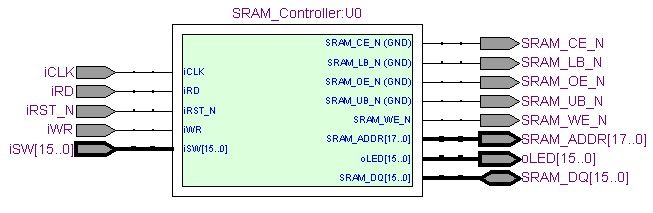

我先尝试的固定地址,就是我固定一个读写的地址为SRAM_ADDR = 18'h0_0000;用16个拨码开关作为数据输入,用两个按键一个KEY[2]表示写入数据,一个KEY[1]表示读出写入的数据,并在16个LED灯上显示,以检测其正确性。代码如下:

1 `timescale 1 ns / 1 ns

2

3 module SRAM_Controller(

4 iCLK,iRST_N,

5 iWR,iRD,iSW,

6 SRAM_DQ,SRAM_ADDR,

7 SRAM_CE_N,SRAM_OE_N,SRAM_WE_N,SRAM_UB_N,SRAM_LB_N,

8 oLED

9 );

10

11 input iCLK,iRST_N;

12 input iWR,iRD; // Write or Read resquest:KEY[2] is Write,KEY[1] is Read.

13 input [ 15 : 0 ] iSW; // The data will be written:SW[0~15]

14 output SRAM_CE_N,SRAM_OE_N,SRAM_WE_N,SRAM_UB_N,SRAM_LB_N; // SRAM control Singal

15 output [ 17 : 0 ] SRAM_ADDR; //

16 inout [ 15 : 0 ] SRAM_DQ; //

17 output [ 15 : 0 ] oLED; // Output display

18 reg [ 15 : 0 ] oLED;

19

20 // reg SRAM_WE_N;

21

22 assign SRAM_CE_N = 1 ' b0; //SRAM Chip Select always enable

23 assign SRAM_OE_N = 1 ' b0; //SRAM Output always enable

24 assign SRAM_UB_N = 1 ' b0; //Upper byte always available

25 assign SRAM_LB_N = 1 ' b0; //Lower byte always available

26 assign SRAM_ADDR = 18 ' h0_0000; //Fixed address

27

28 /* *********************************************** */

29 // Write the data to SRAM

30 reg [ 3 : 0 ] cstate,nstate;

31 reg [ 15 : 0 ] rSRAM_DQ;

32 reg SRAM_tri;

33

34 parameter IDLE = 4 ' d0,

35 WRITE0 = 4 ' d1,

36 WRITE1 = 4 ' d2,

37 READ0 = 4 ' d3,

38 READ1 = 4 ' d4;

39

40 /* ************************************************** */

41 reg [ 3 : 0 ] delay;

42

43 always @( posedge iCLK or negedge iRST_N)

44 if ( ! iRST_N) delay <= 4 ' d0;

45 else if (delay == 4 ' d3)

46 delay <= 4 ' d0;

47 else delay <= delay + 1 ' b1;

48

49 /* ---------- FSM ----------------------------------- */

50 always @( posedge iCLK or negedge iRST_N)

51 if ( ! iRST_N) cstate <= IDLE;

52 else cstate <= nstate;

53

54 always @(cstate or iWR or iRD )

55 case (cstate)

56 IDLE: if ( ! iWR) nstate <= WRITE0;

57 else if ( ! iRD) nstate <= READ0;

58 else nstate <= IDLE;

59

60 WRITE0: if (delay == 4 ' d3) nstate <= WRITE1;

61 else nstate <= WRITE0;

62

63 WRITE1: nstate <= IDLE;

64 READ0: if (delay == 4 ' d3) nstate <= READ1;

65 else nstate <= READ0;

66

67 READ1: nstate <= IDLE;

68 default :nstate <= IDLE;

69 endcase

70

71 always @( posedge iCLK or negedge iRST_N)

72 if ( ! iRST_N) SRAM_tri <= 1 ' b0;

73 else

74 case (cstate)

75 IDLE: if ( ! iWR) SRAM_tri <= 1 ' b1;

76 else if ( ! iRD) SRAM_tri <= 1 ' b0;

77 else SRAM_tri <= 1 ' b0;

78 WRITE0: begin

79 SRAM_tri <= 1 ' b1;

80 rSRAM_DQ <= iSW;

81 end

82 READ1 : oLED <= SRAM_DQ;

83 default : SRAM_tri = 1 ' b0;

84 endcase

85

86 assign SRAM_DQ = SRAM_tri ? rSRAM_DQ : 16 ' hzzzz ;

87 assign SRAM_WE_N = ( ~ SRAM_tri);

88

89 endmodule

90

经验证,可以用。。。按键没做消抖,多按几次,呵呵。

来个RTL视图

OK,下一步。。。