处理器体系结构 第五周10.11~1.18

四、处理器体系结构

我们看到的计算机系统只限于机器语言程序级。我们知道处理器必须执行一系列的指令。设计处理器的第一步:给出一个基于顺序操作、功能正确有点不实用的Y86处理器。

4.1Y86指令集体系结构

4.1.1程序员可见状态

Y86程序中每条指令都会读取或者修改处理器状态的某些部分的状态。

4.1.2 Y86指令

存储器:Y86程序用虚拟地址来引用存储器位置,硬件和操作系统软件联合起来将虚拟地址翻译成实际或物理地址。

状态码:表明程序执行的总体状态,会指示是正常运行还是出现了某种异常。

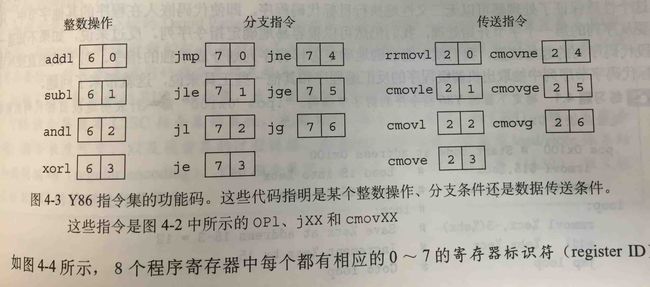

4.1.3指令编码

4字节的常数字

1.irmovl中的立即数数据

2.mmovl,mrmovl中存储器m地址指示符的偏移量

3.绝对地址:分支指令jXX的目的地址

4.绝对地址:调用指令call的目的地址

注意:字节编码和指令序列是相对应的

4.1.4Y86异常

1 AOK 正常操作

2 HLT 处理器执行halt指令

3 ADR 遇到非法地址

4 INS 遇到非法指令

当遇到这些异常的时候,我们就简单地让处理器停止执行指令。在更完整的设计中,处理器通常会调用一个异常处理程序,这个过程被指定用来处理遇到的某种类型的异常。

4.2逻辑设计和硬件控制语言HCL

电子电路中,用1.0V左右的高电压表示逻辑1,用0.0V左右的低电压表示逻辑0.

4.2.1逻辑门

AND &&

OR ||

NOT !

4.2.2组合电路和HCL布尔表达式

字级相等测试电路:一些位级信号代表一个整数或一些控制模式。执行字级计算的组合电路根据输入字的各个位,用逻辑门来计算输出字的各个位。

算数/逻辑单元(ALU)是很重要的组合电路,有三个输入,标号为A、B的两个数据输入和一个控制输入,根据控制输入的设置,电路会对数据输入执行不同的算数或逻辑操作。

4.2.3字级的组合电路和HCL整数表达式

多路复用函数具体格式:

[

select_1 : expr_1

select_2 : expr_2

……

select_k : expr_k

]从逻辑上讲,这些选择表达式是顺序求值的且不同选择表达式之间允许不互斥。

4.2.4集合关系

通用格式:

iexpr in {iexpr1,iexpr2,...,iexprk}(整数表达式)

4.3Y86的顺序实现

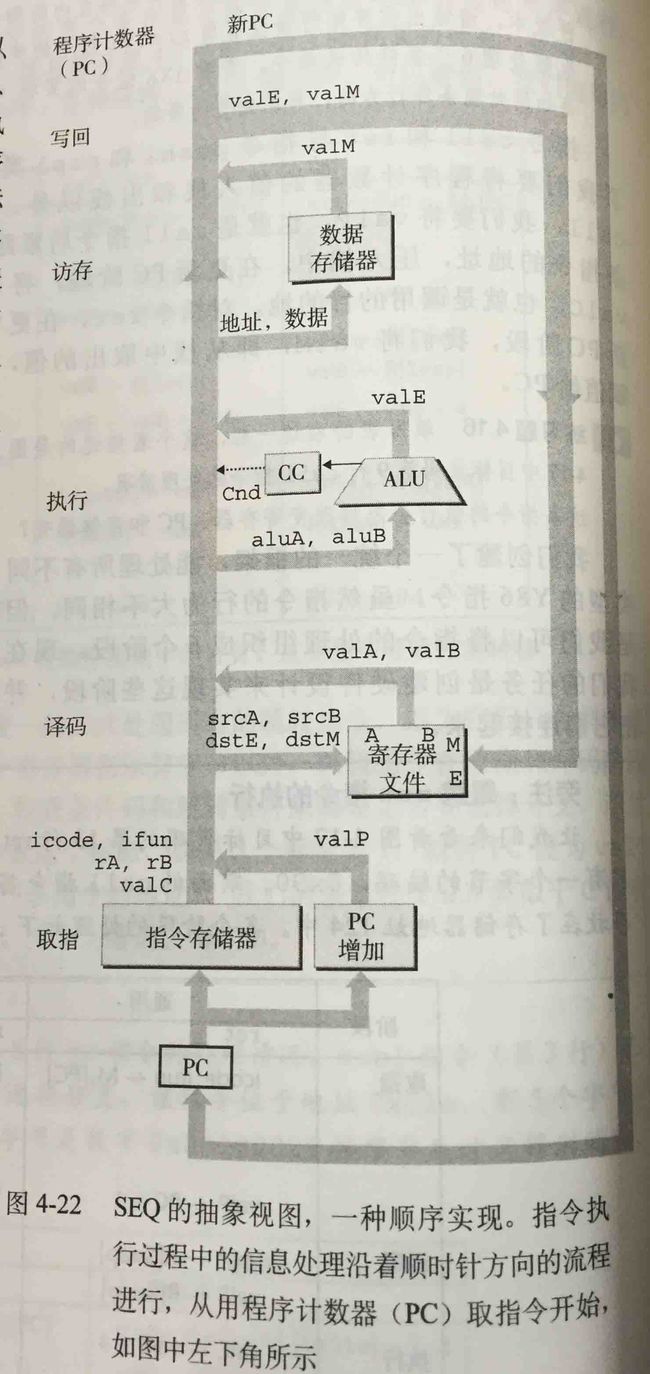

4.3.1将处理组织成阶段

取指 译码 执行 访存 写回 更新PC

4.3.2SEQ硬件结构

4.3.3SEQ的时序

1.取指阶段:取指阶段包括指令存储器硬件单元。以PC作为第一个字节(字节0)的地址,这个单元一次从存储器读出6个字节,第一个字节被解释称指令字节,分为两个4位数。

2.译码和写回阶段:寄存器文件有四个端口,支持同时进行两个读(端口A、B)和两个写(E、M),每个端口都有一个地址连接和一个数据连接。

3.执行阶段:执行阶段包括算术/逻辑单元(ALU)第一步每条指令的ALU计算,执行阶段还包括条件码寄存器。

4.访存阶段:访存阶段的任务是读或者写程序数据,两个控制块产生存储器地址和存储器输入数据的值,另外两个块产生控制信号表明应该执行读操作还是写操作。

5.更新PC阶段:SEQ中最后一个阶段会产生程序计数器的新值,依据指令的类型和是否要选择分支,新的PC可能是valC、valM、valP。

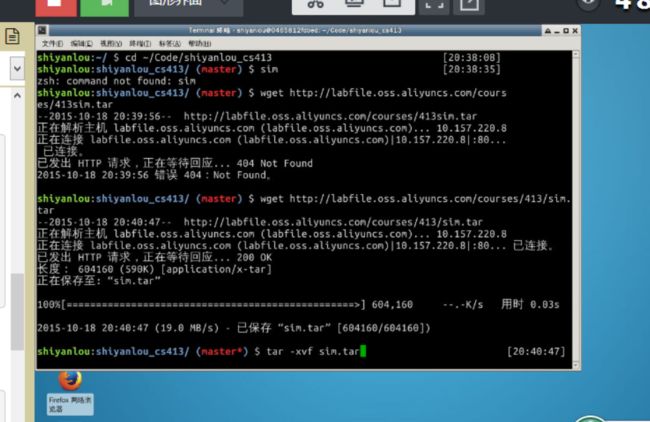

实验测试:

建立环境:

测试代码:

参考资料:

1.《深入理解计算机系统》

2.实验楼学习资料https://www.shiyanlou.com/courses/running/1366

感想:

1.本次学习内容与上学期所学习EDA有相似之处,可以联想学习。

2.对于重点题型加强理解,重点内容弄懂、弄透彻,不留债。