Linux设备驱动程序架构分析之I2C Spec摘要

作者:刘昊昱

博客:http://blog.csdn.net/liuhaoyutz

1、I2C总线介绍

I2C(Inter-Integrated Circuit,内置集成电路)总线是由PHILIPS公司提出的一种串行总线,用于连接处理器及其外围设备,它具有如下特点:

l 只有两条总线线路:一条串行数据线(SDA),一条串行时钟线(SCL)。

l 每个连接到总线的器件都可以使用软件根据它的惟一的地址来识别。

l 传输数据的设备间是简单的主/从关系。

l 主机可以用作主机发送器或主机接收器。

l 它是一个真正的多主机总线,两个或多个主机同时发起数据传输时,可以通过冲突检测和仲裁来防止数据被破坏。

l 串行的8位双向数据传输,位速率在标准模式下可以达到100kbit/s,在快速模式下可达400kbit/s,在高速模式下可达3.4Mbit/s。

l I2C总线上可挂接的设备数量受总线的最大电容400pF限制,如果所挂接的是相同型号的器件,则还受器件地址位的限制。

基于微控制器的电路设计通常需要满足如下设计标准:

1. 一个完整的系统通常至少包括一个微控制器和其它一些外围设备,如内存,I/O扩展等。

2. 连接各种外围设备到系统所需的开销必须达到最小。

3. 执行控制功能的系统不需要很高的数据传输速率。

4. 系统整体性能取决于选择的外围设备和用于连接设备的总线的特性。

要设计一个满足以上要求的系统,一个串行总线结构是必须的。虽然串行总线的数据吞吐量不如并行总线,但是串行总线需要更少的线路并且占用更少的处理器引脚。然而,一个总线并不仅仅是连接线路,它包括与系统通信所需的所有的数据格式和协议。

串行总线上的设备进行通信必须遵守某些协议以避免出现数据混淆、丢失和阻塞。快速设备必须能够与慢速设备通信。整个系统必须不依赖于某个设备,否则就可能无法进行改动和升级。协议还应该能够决定哪个设备对总线进行控制和控制的时间。而且,如果具有不同时钟频率的设备连接到总线上,总线必须提供统一的时钟源。所有这些标准都包含在I2C总线规范中。

2、I2C总线的概念

I2C总线支持任意IC设计工艺的设备(NMOS、CMOS、bipolar)。使用两条线路在设备间传递信息,一条串行数据线(SDA),一条串行时钟线(SCL)。每个设备由一个唯一的地址标识,不管它是微控制器、LCD控制器、存储器还是键盘接口。根据设备的功能,每个设备即可以是数据的发送者,也可以是数据的接收者。显然LCD控制器只能是数据的接收者,而存储器则即可以数据的接收者,也可以是数据的发送者。除了数据的发送者和接收者,设备可以也区分为主设备和从设备。主设备发起数据传输。接收主设备发送的数据的设备是从设备。

表一:I2C总线术语

术语 |

描述 |

Transmitter 发送者 |

向I2C总线上发送数据的设备 |

Receiver 接收者 |

从I2C总线上接收数据的设备 |

Master 主设备 |

发起传输,产生时钟信号,结束传输的设备。 |

Slave 从设备 |

接收主设备发送的数据的设备 |

Multi-master 多主设备 |

多个主设备可以同时尝试取得总线控制权 |

Arbitration 仲裁器 |

当多个主设备同时要求传输数据时,用来仲裁哪个主设备获得总线控制权的过程。 |

Synchronization 同步 |

同步多个设备的时钟信号的过程 |

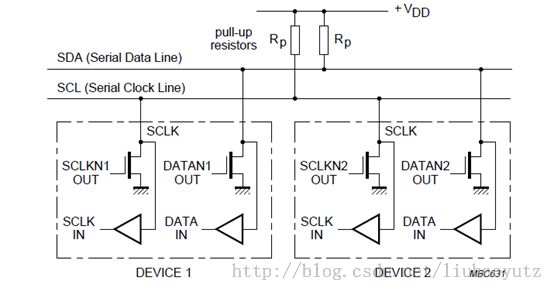

I2C总线是多主设备总线,因为主设备通常是微控制器,所以我们来考虑连接两个微控制器的I2C总线数据传输的例子,如下图所示:

这个例子强调I2C总线上的主设备/从设备和发送者/接收者关系,需要注意的是这种关系并不是固定不变的,而是依赖于某一时刻数据传输的方向。传输数据的流程如下:

1)如果微控制器A想要发送数据给微控制器B:

微控制器A(master),探测(addresses)微控制器B(slave)

微控制器A(master-transmitter),发送数据到微控制器B(slave-receiver)

微控制器A结束数据传输。

2)如果微控制器A想要从微控制器B接收数据:

微控制器A(master),探测(addresses)微控制器B(slave)

微控制器A(master-receiver)从微控制器B(slave-transmitter)接收数据

微控制器A结束数据传输。

在这个例子中,master(即微控制器A)产生时钟信号,并结束传输。

因为I2C总线可以连接多个微控制器,所以可能出现多个master同时请求发起数据传输。为了避免可能由此引起的混乱,一种仲裁程序已经被开发出来。

I2C总线上的时钟信号总是由master设备产生。当在总线上传输数据时,每个master属于它自己的时钟信号。

3、I2C总线特征

SDA和SCL都是双向线,通过一个电源或上拉电阻连到到正电压上。如下图所示:

当总线空闲时,SDA和SCL都是高电平。

I2C总线在标准模式下传输速度可以达到100kbit/s,在快速模式下,可以达到400kbit/s,在高速模式下,可以达到3.4Mbit/s。

连接到I2C总线上的设备的数目仅仅依赖于总线最大电容为400pF的限制。

4、位传输

因为I2C总线可以连接不同类型的设备(CMOS、NMOS、bipolar),所以逻辑0和逻辑1对应的电平是不固定的,依赖于相应的VDD。

每个时钟脉冲对应一个数据位的传输。

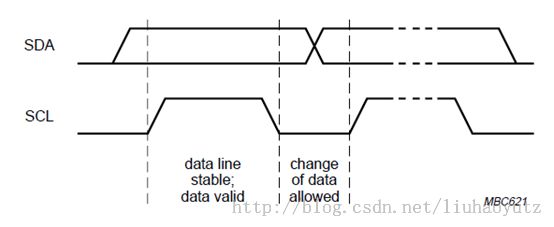

4.1数据有效性

SDA上的电平在SCL为HIGH电平时必须保持稳定,此时SDA上的数据有效。SDA上的HIGH和LOW电平转换只能发生在SCL为LOW电平的情况下。如下图所示:

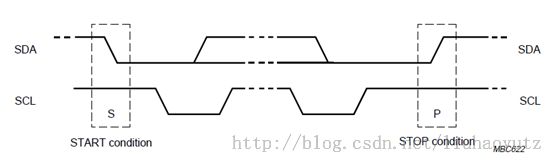

4.2 启动和停止状态

SCL为HIGH电平时,SDA上一个HIGH电平到LOW电平的转换代表启动状态。

SCL为HIGH电平时,SDA上一个LOW电平到HIGH电平的转换代表停止状态。

如下图所示:

启动和停止状态通常由master发出。

启动状态之后,I2C总线被认为进入busy状态。当停止状态后,I2C总线被认为进入空闲状态。

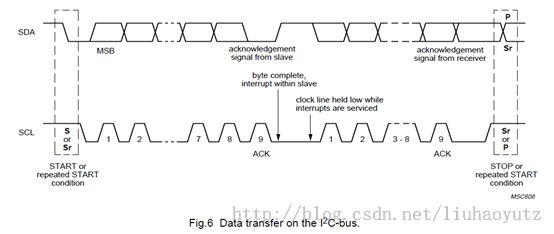

5、传输数据

5.1 字节格式

SDA上传输的字节必须是8位,每次传输可以传送的字节数没有限制。每个字节被传输后,要有一个应答位(ACK)。数据传输时,每个字节的最高有效位(MSB)先发。如果slave因为要完成其它工作(比如处理中断)而无法接收或发送一个完整的字节,它可以将SCL拉低强制master进入等待状态。当slave准备好接收或发送下一个字节时,释放SCL进入高电平,数据传输就可以继续进行了。如下图所示:

5.2 应答

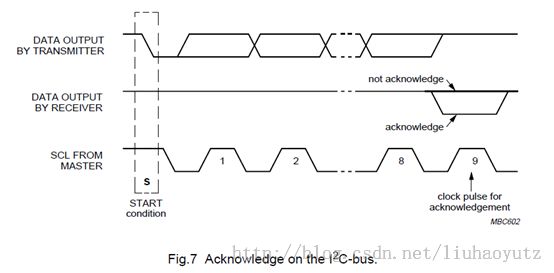

每个字节传输结束后,接收者必须发出一个应答(ACK)信号。数据发送端在发送完一个字节的数据后,释放SDA(进入高电平状态)。数据接收端必须在应答时钟周期内拉低SDA,如下图所示:

当slave不能应答master对slave的寻址时,slave必须拉高SDA,此时,master可以发送一个停止信号中止这次传输,也可以再发送START信号重启传输。

如果一个slave-receiver应答了slave寻址,但是一段时间之后该slave不能继续接收数据,此时slave必须拉高SDA,master发出STOP信号中止传输或发出START信号重启传输。

如果数据接收者是master,当不再接收数据时,master不发出应答信号,通知slave发送端停止发送数据。slave必须释放SDA以允许master产生STOP信号中止传输或START信号重启传输。

6、仲裁和时钟产生

6.1 同步

在I2C总线传输数据时,master在SCL上产生它们自己的时钟。数据仅在SCL为HIGH电平时有效,因此,需要一个确定的时钟用来进行按位的仲裁。

时钟同步是通过线“与”连接I2C接口和SCL来执行的。也就是说,

7、7位地址格式

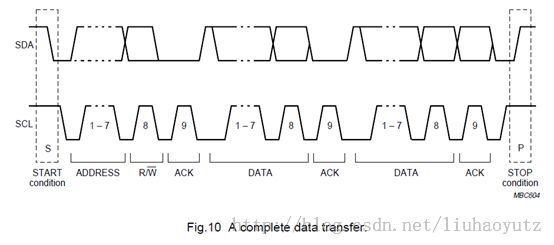

数据传输格式如下图所示:

在START状态之后,发送的是slave地址,这个地址是7位的。第8位表示数据传输方向,为0表示写,为1表示读。

数据传输通过master发出的STOP状态表示结束。但是,如果master还想继续与另外一个slave通信,则可以再发出START状态和另一个slave地址,而不用先发出STOP状态。这样,数据传输中就可能出现多种读写格式的组合,可能的数据传输格式有:

l master发送数据到slave,数据传送方向不会发生改变。如下图所示:

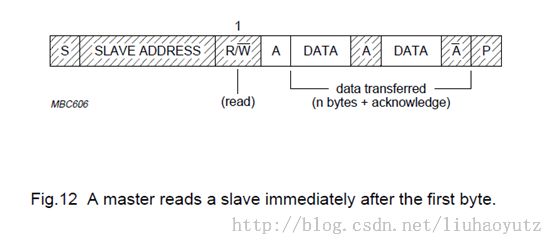

l master在发送完第一个字节寻址后从slave读数据。如下图所示:

当收到第一个应答信号后,master从发送者变为接收者,slave从接收者变为发送者。第一个应答信号仍然由slave发出。STOP状态由master发出,而且之前还要发送一个非应答信号。

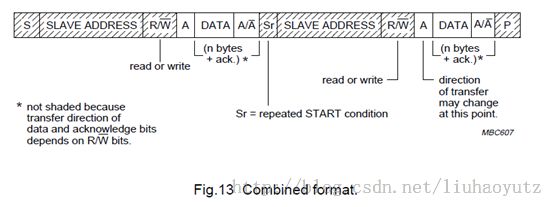

l 复合格式如下图所示:

当传输方向改变时,必须重新发送START状态和slave地址,但是读/写位相反。如果一个master接收者要再发送START状态,它必须首先发送一个非应答信号。

8、7位寻址

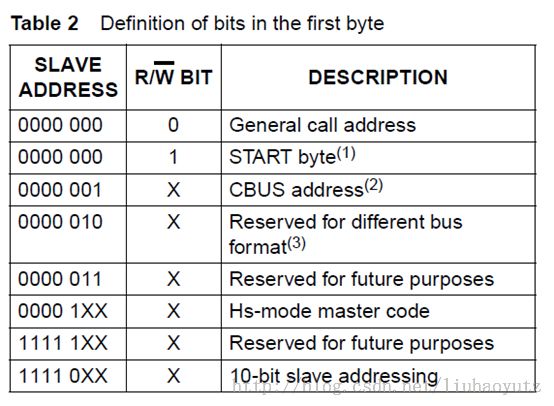

I2C总线的寻址过程是:START状态后的第一个字节代表被master选中的slave的地址。但是“广播地址”是一个例外,它可以寻址所有的设备。理论上,当发出“广播地址”后,所有的设备都要进行应答,但是,设备可以被设置为忽略广播地址。广播地址的第二个字节定义了要执行的动作。

8.1 第一个字节的位定义

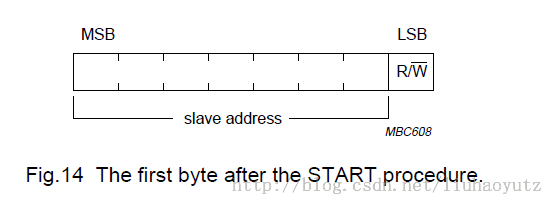

第一个字节的开始7位组成了slave的地址,如下图所示:

第8位是最低有效位(LSB),它决定了数据传输的方向。0代表master将向指定的slave写数据。1代表master将从选定的slave读数据。

当一个地址被发送后,连接到I2C总线上的所有设备都比较是否与自己的地址相匹配。如果匹配,设备认为自己被master选中,根据读/写位,作为发送者或接收者。

slave地址由两部分组成:固定位和可编程位。因为很可能有多个相同的设备连接到同一个I2C总线上,可编程位允许尽可能多的相同设备连接到同一个I2C总线上。设备地址的可编程位取决于设备的引脚数。例如,一个设备地址有4位固定位和3个可编程位,则最多有8个这种设备连接到同一I2C总线上。

I2C总线委员会协调I2C地址的分配。2组共8个地址(0000XXX和1111XXX)被保留,其用途如下表: