Window XP驱动开发(十一) USB2.0 芯片CY7C68013A+FPGA实现的高速传输系统设计(软件及硬件)

转载请标明是引用于 http://blog.csdn.net/chenyujing1234

欢迎大家拍砖!

一、 CY7C68013A芯片介绍

1、 特点

* USB 2.0 高速(TID # 40460272)

* 单片的集成USB2.0收发器, Smart SIE 且有加强的8051 微处理器.

* 可编程的64Byte 端点。

* 8 bit 或 16 bit 外部数据接口

* Smart Media 标准 ECC Generation

* 为控制传输的配置和数据端口的分开数据Buffers

* GPIF(General Programmable Interface)

使能直接连接到并行串口

可编程的波形描述符并配置寄存器来定义波形.

支持RDY输入和CTL输出。

2、 应用

* 便携的视频记录器

* MPEG/TV 转化器

* DSL 模块

* ATA 接口

* 内存读卡器

* 摄像头

* Home PNA

* 无线的LAN

* MP3播放器

3、 功能概况

3、1 USB 速度

* 全速,12Mbps

* 高速,480Mbps

(不支持低速的传输,1.5 Mbps)

3、2 8051 微处理器

EZ-USB FX2中内嵌的增强型8051微处理器带有256B的数据存储器、扩展的中断系统、3个定时/计数器和2个串口UART。

FX2需外接24MHz的晶振,并匹配20pF的电容接地,经过内部倍频电路,产生48MHz的增强型8051默认工作频率。

FX2还需产生480MHz的时钟脉冲以供USB2.0串行收发使用。

3、2、1 数据存储器

数据存储器分为3个部分:地址范围为00h-7Fh的直接寻址区、地址范围为80h-FFh的特殊功能寄存器区(SFR)和地址范围为80h-ffh的间接寻址区。

3、2、2 中断系统

3、2、3 挂起和复位

在接收到USB总线发出的挂起信号后,增加型8051通过设置其寄存器PCON.0为1,可使EZ-USB FX2进入省电状态,这时FX2的振荡电路将停止工作。

唤醒方法有3种:USB总线的恢复信号、外部信号触发WAKEUP管脚和外部信号解发WU2(WAKEUP)管脚。

EZ-USB FX2 8051的复位信号由主机通过一个寄存器位CPUCS.0控制。在FX2芯片上电时,9051处于各复位状态;待软固件代码下载至芯片的RAM中后,主机

将清除CPUCS.0,使8051脱离复位状态,并开始它的固件程序。

3、3 I2C 总线

3、4 总线

3、5 USB Boot 方法

在上电阶段,查找内部的I2C端口,如果第一byte是0xC0或0xC2,那么它用EEPROM中的VID/PID/DID值;

如果没有EEPROM被找到,那么FX2LP会枚举内部存储的描述符。

默认的ID值是VID/PID/DID(00x4B4, 0x8613,0xAxxx where xxx = 芯片的版本)

3、6 枚举

当第刚插入USB时,FX2LP会自动枚举并下载软硬件和USB描述符表。

接下来,FX2LP会再枚举。

3、7 Bus-Powered 应用

3、8 中断系统

3、8、1 INT2中断请求和全能寄存器

FX2LP执行INT2和INT4的自动vector。 总共有27个INT2(USB)vector,和14个INT4 (FIFO/GPIF)vector.

3、8、2 USB中断 Autovcetors

主USB中断被27个中断源共享。FX2LP提供第二层的中断vectoring, 叫Autovectoring.

3、9 存储空间

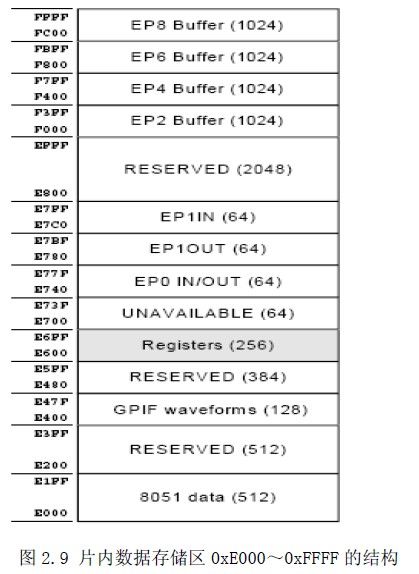

EZ-USB FX2的片内存储由3部分组成:主RAM(0x000-0xfFFF)、临时RAM(0xE000-0xE1FF)和寄存器/缓冲器(0xE222-0xFFFF)。如下图。

其中8k字节的RAM被程序存储器和数据存储器所共享;

0.5k字节的临时RAM仅用作为数据存储器;

7.5K字节的寄存器/缓冲器包含FX2控制/状态寄存器和各端点的数据传输缓冲区。

3、9、1 片内存储区

在上图中,地址范围为0x0000-0x1FFF的8K字节用于存储8051的程序代码和数据,称为“主RAM“。

3、9、2 片内0xE000-0xFFFF存储区

其中,512字节的临时RAM(0xE000-0xE1FF)仅作为数据存储器,8051固件代码不能在该空间运行;

128字节的0xE400-0xE47F空间用于存储GPIF的4个波形描述符;

0xE600-0xE6FF空间用于保存FX2的控制和状态寄存器;

0xE740-0XE7FF和0xF000-0xFFFF空间作为FX2端点的数据缓冲区,用户可通过寻址RAM方式或FIFO方式来访问。(重点)

2、9、2、1 FX2端点缓冲区

EZ-USB FX2 芯片内部包含3个固定的64字节端点缓冲区(0xE740-0xE7FF)和4KB的可配置端点缓冲区空间(0xF000-0xFFFF),如上图。

3个64字节的缓冲区分别用于EP0、EP1IN和EP1OUT,

4KB的可配置缓冲区用于EP2、EP4、EP6和EP8

(1)其中,端点1支持传输、中断和同步传输,其OUT数据占用缓冲区0xE780-0xE7BF,IN数据占用缓冲区0xE7C0-0xE7FF。

(2)端点0和端点1仅能由FX2的固件程序访问。

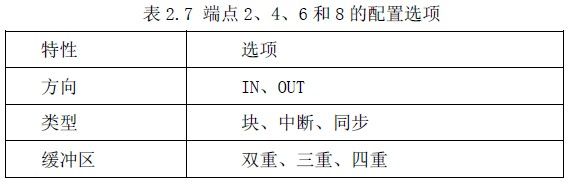

(3)端点2、端点4、端点6和端点8是大容量高宽带的数据传输端点,其无需8051固件干涉就可同外围电路完成高速数据传输。

这4个端点的配置方式非常灵活,以适应不同场合下的带宽要求。见下表。

其中,双重缓冲意味着USB读写一个缓冲区的同时,另一个缓冲区可与外围电路进行数据通信;

三重缓冲增加了第三个数据缓冲区,可供USB端或外围电路使用;

四重缓冲增加了第四个数据缓冲区。

注意:这里的缓冲区按我的理解:如FPGA给的数据太快时会而MCU还没来取数据,那么会先放到缓冲区中,让值不会被覆盖。

3、10 I/O系统

EZ-USB FX2提供了两种类型的I/O系统:可编程I/O口和I2C控制器。

I/O口由PA、PB、PC、PD、PE组成,共40个脚。注意:如果是100脚和128脚封装的FX2包含全部5个I/O口,而56脚的仅包含FA、FB和FD。

I2C总线使用SCL和SDA两个管脚。

3、10、1 I/O口

与EZ-USB不同,FX2的增强型8051使用特殊功能寄存器0Ex(0EA、0EC、0ED、0EE)和IOx(IOA、IOB、IOC、IOD)来控制其I/O管脚。结构如下图:

3、10、2 从属FIFO接口模式

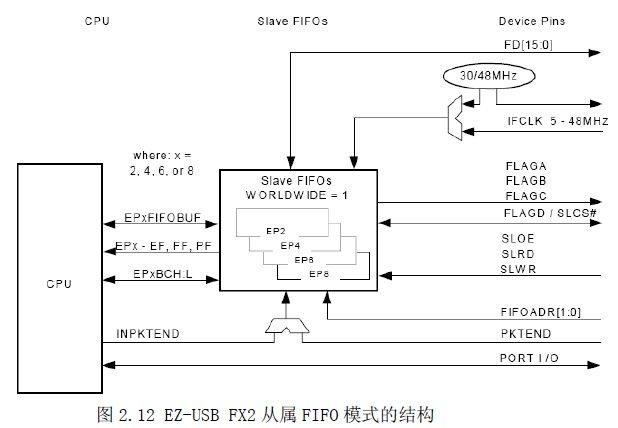

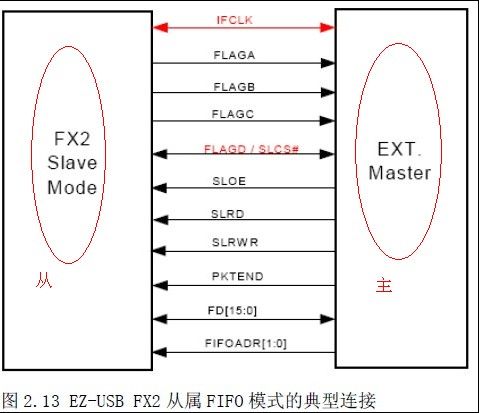

为便于端点2、端点4、端点6和端占8的数据缓冲区能更好地和外围电路进行通信,FX2还提供了2种接口模式:

从属FIFO和GPIF。其由寄存器IFCFG控制。

(1)从属FIFO模式。

以下是它的模式结构和外围电路的典型连接图:

其中IFCLK为接口时钟,可由芯片内部产生(30MHz/48MHz),也可由外部输入(5MHz-48MHz);

FLAGA-FLAGD为FIFO标志管脚,用于映射FIFO的当前状态;

SLCS#为从属FIFO的片选信号,低电平有效;

FD[15:0]为16位双向数据总线;

FIFOADR[1:0]用于选择和FD连接的端点缓冲区(00代表端点2,01代表端点4,10代表端点6,11代表端点8)

SLOE用于使能数据总线FD的输出;

SLRD和SLWR可分别作为FIFO的读写选通信号;

外围电路可通过使能PKTEND管脚向USB发送一个IN数据包,而不用考虑该包的长度。

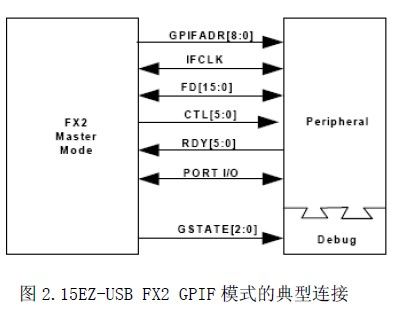

(2) GPIF接口模式

在GPIF模式下,EZ-USB FX2可由软件来编程输出读写控制波形。这时,它几乎可对任何通用总线接口进行访问,如ASIC、DSP等。

下图展示了GPIF模式结构和这种模式下FX2和外围电路的典型连接。

其中,GPIFADR[8:0]用于输出9位地址;

IFCLK为接口时钟;

FD[15:0]为16位双向数据总线;(因为是16根数据线过来,所以得把接收FPGA数据的端点的WORDWIDE属性设置为1,不然会数据出错)

CTL[5:0]用于输出可编程的控制信号,如读写选通等;

RDY[5:0]为输入的状态信号。

GSTATE[2:0]用于输出当前GPIF状态码,通常仅在调试时使用。

3、11 列举和重列举

与EZ-USB类似,FX2在上电时,首先由“缺省USB设备”进行“列举”,并把8051固件下载到芯片的RAM内;之后8051会脱离复位并开始执行这些代码,

并照固件的内容再一次对设备进行“重列举”。再重列举完成后,对控制端点0的设备请求可FX2缺省USB设备处理(USBCS中的RENUM位为0),

也可由增强型8051的固件代码处理(RENUM为1)。

3、11、1 缺省USB设备

当EZ-USB FX2列举完成后,它将以“缺省USB设备”展现给用户,这时其只含有1个USB配置,该配置中包含1个接口,这个接口具有4种可替换设置

0、1、2 和3,见下表(全速模式)和(高速模式)。

3、11、2 端点0对设备请求的响应

在RENUM == 0时,EZ-USB FX2内核可自动对端点0的控制请求做出响应。除支持USB标准设备请求外,其还可以支持一些供应商自定义的请求。

3、11、3 无EEPROM列举模式

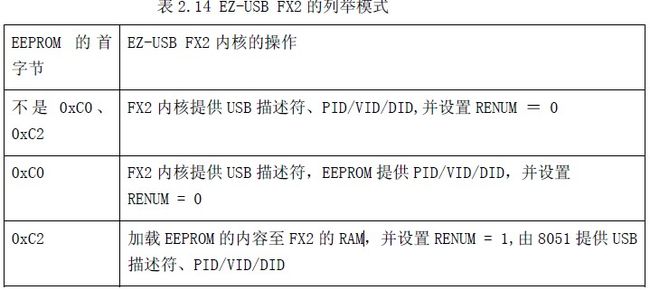

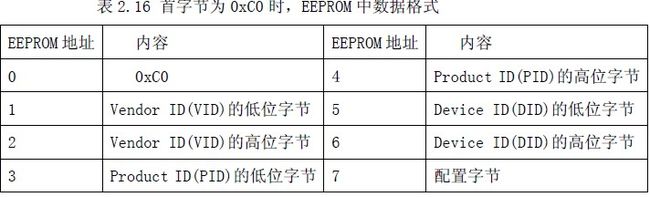

当EZ-USB FX2上电并脱离复位状态后,其就会检查芯片的I2C总线上是否连接有串行EEPROM,如果存在,它将读取一个字节以决定其列举模式。

根据是否存在EEPROM及其首字节内容,FX2共有3种列举模式:无串行EEPROM、EEPROM的首字节为0XC0、EEPROM的首字节为0XC2.

(1) EEPROM首字节为0XC0的列举模式

它将从EEPROM中读取VID、PID和DID的值,而各种USB描述符仍由FX2芯片内部提供。

下表是这种模式下EEPROM中数据模式,其中地址7为配置字节,用于设置I2C总线的传输速率和USB断开极性(缺省是FX2脱离复位后和USB连接)。

(2) EEPROM首字节为0xC2列表模式

此时VID、PID、DID、各种USB描述符,及其8051代码都由该EEPROM提供。

二、 系统设计

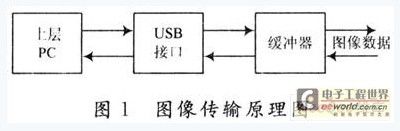

将CY7C68013A芯片的Slave FIFO块传输接口模式和FPGA技术相结合,实现了计算机与外设之间高速的数据传输。

1、硬件及外设控制设计

CY7C68013A与外设有三种接口方式:端口模式、可编程接口GPIF和Slave FIFO。

Slave FIFO方式是从机工作方式,在具有外部数据处理逻辑的设备中,USB数据在主机和外部逻辑设备中传输,通常不需要FX2LP的CPU参与,而是经过FX2LP内部端点FIFO来传输。外部控制器可对多个端点的FIFO选择读写。FX2LP的Slave FIFO工作方式可设为同步或异步;工作时钟均可由内部产生或外部输入。基于该系统处理的是高速传输,需要外部控制器直接对FIFO进行控制,故采用从机,即Slave FIFO方式(也就是EX-USB FX2的从属FIFO模式)。高速传输的原理框图如图1所示.

首先图像可由计算机上层应用软件发送或者接收,再通过USB接口芯片连接高速缓存。

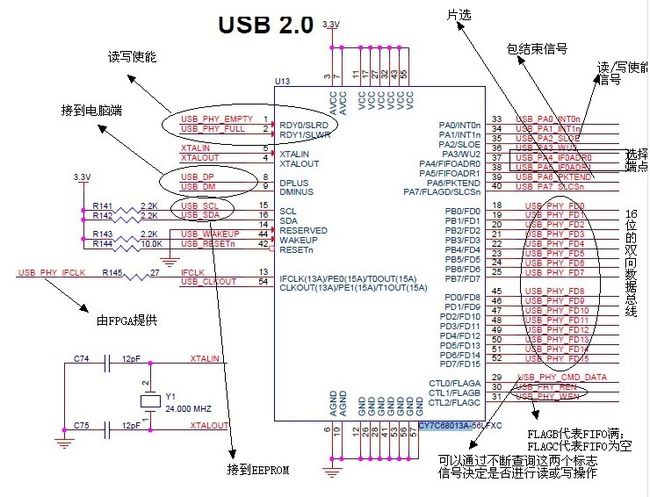

如图2所示,CY7C68013A的主要功能信号及与FPGA之间的握手信号如:

IFCLK为时钟信号,可以选择由外部输入或者内部输出;

FIFOADR[1:0]引脚选择4个FIFO(2,4,6或8)中的一个与USB数据总线FD连接。

定义该系统中上行数据传输为FIFOADR[1:0]=10,即为EP6端口;

下行数据传输为FIFOADR[1:0]=01,即为EP2端口。

FLAGB,FLAGC为所选择FIFO的标志信号,FLAGB代表FIFO为满;FLAGC代表FIFO为空;默认低电平有效。(具体是哪个端点的满空要看FIFOADR[1:0]指向哪个端点)

FPGA可以通过不断查询这两个标志信号决定是否进行读或写操作。

SLOE(Slave FIFO Output Enable)为读/写使能信号,它使能被选择的宽度的数据;

SLWR,SLRD分别为读写控制信号,在同步和异步模式下,控制信号不一;

FD[15:0]为16位的双向数据总线。PA0,PA1为输出信号,作为硬件系统工作状态的控制信号。

原理图(有标的都是FPGA的控制有关的引脚):

注: USB_WAKEUP、USB_PA3_WU2要接高,不然会使CY7C68一直在唤醒中,导致VID、PID读取不到因为WU2是一个USB唤醒源,通过WU2EN bit (WAKEUP.1)使能,并通过WU2POL(WAKEUP.1)设置。WU2EN bit时, 通过判断此脚电平唤醒芯片。

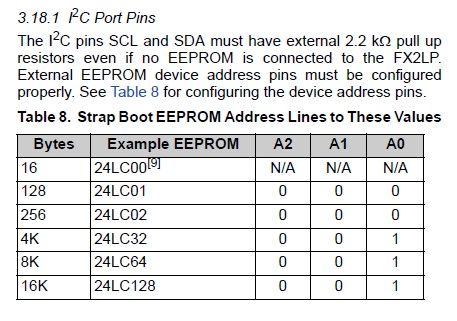

项目总结:一开始我们是24LC128,根据下表的匹配,我们把A0接高; 后来发现EERPROM中的数据一直无效。

项目因此耽误了一周。后来发现我们的芯片不是24LC128,而是24C 16。芯片上的铭牌上标有:

ATM 128

24C 16。

真是硬件工程师的马虎,一查资料,这块容量只有2014K Byte。而我的软硬件是3K啊,怪不得每次EEPROM数据无效。(8051从EEPROM中读数据后有做校验)。

没办法,只能换一块了。后来改为AT24C32,有4KByte容量。

2、 软件设计

图像传输系统的软件设计主要包括三个部分:固件程序设计、驱动程序设计和计算机上层应用软件。

2、1 固件程序设计

固件程序是硬件中的软件部分,通过执行该软件可实现特定的硬件功能,主要包括初始化、处理标准的USB设备请求以及USB挂起时的电源管理等。

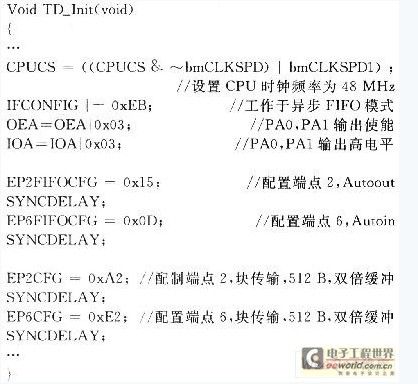

步一:固件首先初始化内部的状态变量,然后调用用户初始化函数TD_Init()。

TD_Init函数负责CY7C68013A进行初始化,首先设置时钟为48 MHz,然后设置芯片工作于从属FIFO块传输模式,并配置端点6工作于自动块传输IN,端点2自动块传输OUT模式。

步二:从该函数返回后,固件初始化USB接口到未配置状态并使能中断。然后每间隔1 s进行一次设备重枚举(请看本文的 3、11 列举和重列举 ),直到端点0接收到一个SETUP包。

步三:任务分发。一旦检测到SETUP包,固件函数将开始交互下述任务调度(即一个while循环):

调用用户函数TD_Poll()轮询所有的设备,判断是否有标准设备请求等待处理,如果有,分析该请求并响应SetupCommand();

判断USB内核是否收到USB挂起信号(即判断Sleep事件)。如果有,则调用用户函TD_Suspend()。从该函数成功返回TRUE值后, 再检测是否发生USB唤醒事件。

如果未检测到唤醒事件,则处理器进入挂起方式EZUSB_Susp(); ;

如果有唤醒事件,则调用用户函数TD_Resume(),程序继续运行。如果从TD_Suspend函数返回FALSE,则程序继续进行。

// Task dispatcher

void main(void)

{

DWORD i;

WORD offset;

DWORD DevDescrLen;

DWORD j=0;

WORD IntDescrAddr;

WORD ExtDescrAddr;

// Initialize Global States

Sleep = FALSE; // Disable sleep mode

Rwuen = FALSE; // Disable remote wakeup

Selfpwr = FALSE; // Disable self powered

GotSUD = FALSE; // Clear "Got setup data" flag

// 步一:初始化用户设备

TD_Init();

// 步二:从该函数返回后,固件初始化USB接口到未配置状态并使能中断。

// 然后每间隔1 s进行一次设备重枚举,直到端点0接收到一个SETUP包。

// The following section of code is used to relocate the descriptor table.

// The frameworks uses SUDPTRH and SUDPTRL to automate the SETUP requests

// for descriptors. These registers only work with memory locations

// in the EZ-USB internal RAM. Therefore, if the descriptors are located

// in external RAM, they must be copied to in internal RAM.

// The descriptor table is relocated by the frameworks ONLY if it is found

// to be located in external memory.

pDeviceDscr = (WORD)&DeviceDscr;

pDeviceQualDscr = (WORD)&DeviceQualDscr;

pHighSpeedConfigDscr = (WORD)&HighSpeedConfigDscr;

pFullSpeedConfigDscr = (WORD)&FullSpeedConfigDscr;

pStringDscr = (WORD)&StringDscr;

// Is the descriptor table in external RAM (> 16Kbytes)? If yes,

// then relocate.

// Note that this code only checks if the descriptors START in

// external RAM. It will not work if the descriptor table spans

// internal and external RAM.

if ((WORD)&DeviceDscr & 0xC000)

{

// first, relocate the descriptors

IntDescrAddr = INTERNAL_DSCR_ADDR;

ExtDescrAddr = (WORD)&DeviceDscr;

DevDescrLen = (WORD)&UserDscr - (WORD)&DeviceDscr + 2;

for (i = 0; i < DevDescrLen; i++)

*((BYTE xdata *)IntDescrAddr+i) = *((BYTE xdata *)ExtDescrAddr+i);

// update all of the descriptor pointers

pDeviceDscr = IntDescrAddr;

offset = (WORD)&DeviceDscr - INTERNAL_DSCR_ADDR;

pDeviceQualDscr -= offset;

pConfigDscr -= offset;

pOtherConfigDscr -= offset;

pHighSpeedConfigDscr -= offset;

pFullSpeedConfigDscr -= offset;

pStringDscr -= offset;

}

EZUSB_IRQ_ENABLE(); // Enable USB interrupt (INT2)

EZUSB_ENABLE_RSMIRQ(); // Wake-up interrupt

INTSETUP |= (bmAV2EN | bmAV4EN); // Enable INT 2 & 4 autovectoring

USBIE |= bmSUDAV | bmSUTOK | bmSUSP | bmURES | bmHSGRANT; // Enable selected interrupts

EA = 1; // Enable 8051 interrupts

#ifndef NO_RENUM

// Renumerate if necessary. Do this by checking the renum bit. If it

// is already set, there is no need to renumerate. The renum bit will

// already be set if this firmware was loaded from an eeprom.

if(!(USBCS & bmRENUM))

{

EZUSB_Discon(TRUE); // renumerate

}

#endif

// unconditionally re-connect. If we loaded from eeprom we are

// disconnected and need to connect. If we just renumerated this

// is not necessary but doesn't hurt anything

USBCS &=~bmDISCON;

CKCON = (CKCON&(~bmSTRETCH)) | FW_STRETCH_VALUE; // Set stretch

// clear the Sleep flag.

Sleep = FALSE;

// 步三:任务分发。一旦检测到SETUP包,固件函数将开始交互下述任务调度

while(TRUE) // Main Loop

{

// 轮询所有的设

TD_Poll();

// 判断是否有标准设备请求等待处理,如果有,分析该请求并响应SetupCommand();

if(GotSUD)

{

SetupCommand(); // Implement setup command

GotSUD = FALSE; // Clear SETUP flag

}

// check for and handle suspend.

// NOTE: Idle mode stops the processor clock. There are only two

// ways out of idle mode, the WAKEUP pin, and detection of the USB

// resume state on the USB bus. The timers will stop and the

// processor will not wake up on any other interrupts.

// 判断USB内核是否收到USB挂起信号(即判断Sleep事件)。如果有,则调用用户函TD_Suspend

if (Sleep)

{

if(TD_Suspend())

{

Sleep = FALSE; // Clear the "go to sleep" flag. Do it here to prevent any race condition between wakeup and the next sleep.

// 如果未检测到唤醒事件,则处理器进入挂起方式EZUSB_Susp();

do

{

EZUSB_Susp(); // Place processor in idle mode.

}

while(!Rwuen && EZUSB_EXTWAKEUP());

// above. Must continue to go back into suspend if the host has disabled remote wakeup

// *and* the wakeup was caused by the external wakeup pin.

// 8051 activity will resume here due to USB bus or Wakeup# pin activity.

EZUSB_Resume(); // If source is the Wakeup# pin, signal the host to Resume.

// 如果有唤醒事件,则调用用户函数TD_Resume(),程序继续运行

TD_Resume();

}

}

}

}

固件hex二进制代码下载到CY7C68的的方式有两种:

(1)开机自动将固件程序下载至芯片RAM中,以由增强性8051执行。结合CYPRESS开发包EZ-Loader Drivers以及HEX2C和Windows DDK即可生成所需要固件自动下载程序.sys文件。

(2)还有另一种方式就是将确定正确的hex固件写到EEPROM中,断电开机时每次都从EEPROM中读取。

我们有16K的EEPROM芯片24LC128,这里我们选择第二种方式。

2、2 驱动程序设计

具体代码请参考我的下一篇文章: <<Window XP驱动开发(十三) 芯片功能驱动端 (代码实现,针对USB2.0 芯片CY7C68013A)>>

USB设备驱动程序负责建立起主机端和设备端的联系。

驱动程序主要有两个:

一、如果是需要自动下载固件hex文件的,那么得自行开发带下载功能的.sys驱动文件。

是开机自动将固件程序下载至芯片RAM中,以由增强性8051执行。结合CYPRESS开发包EZ-Loader Drivers以及HEX2C和Windows DDK即可生成所需要固件自动下载程序.sys文件。

二、如果硬件中带有EEPROM,那么只需要完成上位机应用程序和硬件设备之间的数据传输。其主要包括驱动程序入口例程、即插即用例程、分发例程、电源管理例程和卸载例程。本系统根据通用驱动结合自身需要,在DDK环境下修改编译,生成自己需要的驱动程序。USB上层应用程序都通过I/O控制来访问设备驱动程序。

上层应用程序首先通过调用Win32函数CreaFile()来取得访问设备驱动程序的句柄;然后应用程序使用Win32函数Devi-ceIoControl()来提交I/O控制码,并且为CreatFile()函数返回的设备句柄设置I/O缓冲区。该系统中,设置USB端口缓冲区FIFO为1 024 B,端口非空即读取。保持了传输的连续性,并且每次以帧结构包形式传输,每包的大小为512 B。以实验中为例。每传输大小为245 KB的一幅图像,需要490个包进行传输。