TI DSP的EMIF接口的地址总线问题(实际测试)

题目:TI DSP的EMIF接口的地址总线问题(实际测试)

去年,曾写过如下博文:有关TI DSP的两个问题:地址总线不从零开始问题及寻址范围问题 (链接:http://blog.csdn.net/jbb0523/article/details/7058057)

在此博文中,具体谈到了当DSP内部访问EMIF内的某一地址时,地址总线的的数值问题,当时的结果只是从理论上得到的,也没有验证,今天验证了一下,分享出来……

平台:DSP(TMS320C6416T)+FPGA

其中6416的EMIFA与FPGA相连。

试验中,使用EMIFA CE1空间,并将其设置为16位异步接口。在DSP中给某一CE1空间中的地址赋值,即执行写操作;FPGA这边,直接用ChipScope观察地址总线的值。

共试验了几个值:

写地址(16进制) 地址总线值(16进制)

0x9000 0000+2*0x1 0x1

0x9000 0000+2*0x2 0x2

0x9000 0000+2*0x2+1 0x2

0x9010 0000+2*0x2 0x80002

0x9000 0000+2*0xFFFFF 0xFFFFF

0x9000 0000+2*0xFFFFF+2 0x0

由以上的值基本可以得出访问的地址与地址总线值之间的关系:

设访问的地址为ADDR,则址值总线上的值为floor[(ADDR-0x90000000)/2],floor为向下取整。由于此时为异步接口,对于20位的址址总线来说,地址变化最大为1M的范围,即从0~0xFFFFF,因此实际值为floor[(ADDR-0x90000000)/2]%0x100000,%表示取模,0x100000即为1M地址空间。

那么当把接口设置为32位异步接口呢?64位异步接口呢?

针对这个问题,我也试了一下,基本结论是这样的:

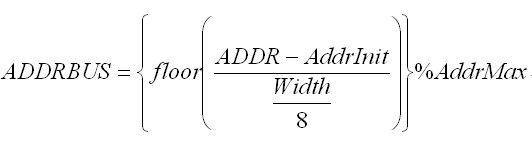

设接口位宽为Width,CE空间起始地址为AddrInit,地址最大范围为0~AddrMax-1,访问的地址为ADDR,地址总线上的值为ADDRBUS,则有如下关系:

ADDRBUS=floor[(ADDR-AddrInit)/(Width/8)]%AddrMax

再贴一个清楚一点的公式,呵呵,和上面的完全一样,这样是不是看起来更直接:

例如:

接口位宽Width=16

CE空间起始地址AddrInit=0x9000 0000

地址最大范围为AddrMax=1M=2^20=0x100000

访问地址ADDR=0x9000 0005(即0x9000 0000+2*0x2+1 )

ADDRBUS=floor[(0x9000 0005-0x9000 0000)/(16/8)]%0x100000=2

这与前面的结果是一致的!

补充一个时序问题:

1)DSP写,即FPGA读,在FPGA中检测AWE下降沿且CE为低时,读数据总线即可;

2)DSP读,即FPGA写,在FPGA中当AOE和CE均为低时,写数据总线即可。

到此,搞定DSP与FPGA通过EMIF接口通信问题!