TMS320C55x的硬件结构

1.TMS320C55x DSP的基本结构

1.1C55x的CPU体系

C55x有1条32位的程序数据总线(PB),5条16位数据总线(BB、CB、DB、EB、FB)和1条24位的程序地址总线及5条23位的数据地址总线,这些总线分别与CPU相连。总线通过存储器接口单元(M)与外部程序总线和数据总线相连,实现CPU对外部存储器的访问。这种并行的多总线结构,使CPU能在一个CPU周期内完成1次32位程序代码读、3次16位数据读和两次16位数据写。C55x根据功能的不同将CPU分为4个单元,即指令缓冲单元(I)、程序流程单元(P)、地址流程单元(A)和数据计算单元(D)。

1.3 程序流单元(P unit)

其中PF1表示向存储器提供的程序地址,PF2表示等待存储器的响应,F表示从存储器取一个指令包并放入指令缓冲队列中,PD表示对指令缓冲队列中的指令预解码(确定指令的起始和结束位置;确定并行指令)。

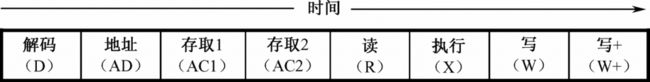

第二阶段是指执行流水线,这部分的功能是对指令进行解码,完成数据的存取和计算。

流水线的第二阶段(执行流水线)

为了解决流水冲突的问题,增加额外周期做流水保护处理。

3 TMS320C55x 存储空间结构

C55x DSP的存储空间包括统一的数据/程序空间和I/O空间。数据空间用于访问存储器和内存映射寄存器,程序空间用于CPU从存储器中读取指令,而I/O空间用于CPU与外设之间的双向通信。

3.1 存储器映射

C55x的寻址空间为16MB,当CPU从程序空间读取程序代码时,使用24位地址,当访问数据空间时,使用23位的地址。但是在访问数据空间时,将23位地址左移一位,并将地址总线上的最低有效位(LSB)置0,使得在对数据空间或程序空间寻址时,地址总线都传送24位地址。

数据空间被分成128个主数据页(第0页到第127页),每个主数据页的大小为64K字,指令通过7位的主数据页值和16位的偏移值共同来确定数据空间的任何一个地址。

在第0主数据页中,前96个地址(00 0000h~00 005Fh)为存储映射寄存器(MMR)保留,相对应在程序空间有192个地址(00 0000h~00 00BFh),这段存储区为系统保留区,用户不能使用该区。

3.2 程序空间

当CPU读取指令时,程序空间才被访问。CPU采用字节寻址来读取变长的指令,指令的读取要和32位的偶地址对齐(地址的低两位为零)。

1.字节寻址(24位)

当CPU从程序空间读取指令时,采用字节寻址,即按字节分配地址,且地址为24位。一个行宽为32位存储器的地址分配由下图说明,每个字节分配一个地址,例如字节0的地址是00 0100h,字节2的地址是00 0102h。

字节地址 00 0100h~00 0103h

字节0 字节1 字节2

2. 程序空间的指令结构

DSP支持8位、16位、24位、32位和48位长度的指令。表2-5和图2-9说明了指令在程序空间如何存放。在32位宽的存储器中存放了5条指令,每一条指令的地址是指操作码最高有效字节的地址,阴影部分表示没有代码。

表2-5 指令长度及地址分配

| 指 令 |

长度(位) |

地 址 |

| A |

24 |

00 0101h |

| B |

16 |

00 0104h |

| C |

32 |

00 0106h |

| D |

8 |

00 010Ah |

| E |

24 |

00 010Bh |

图2-9 存储器中的指令

| 字节地址 |

字节0 |

字节1 |

字节2 |

字节3 |

| 00 0100h~000103h |

|

A(23~16) |

A(15~8) |

A(7~0) |

| 00 0104h~000107h |

B(15~8) |

B(7~0) |

C(31~24) |

C(23~16) |

| 00 0108h~00010Bh |

C(15~8) |

C(7~0) |

D(7~0) |

E(23~16) |

| 00 010Ch~00010Fh |

E(15~8) |

E(7~0) |

|

|

3. 程序空间的边界对齐

在程序空间存放指令时不需要边界对齐,当读取指令时要和32位的偶地址对齐。也就是说,在读取一条指令时,CPU要从最低两位是0的地址读取32位的代码,这样的地址其最低位应是0h,4h,8h和Ch。

不过,也会遇到写入到程序计数器PC中的地址值和程序空间的读取地址不一致的情况,例如,执行一个子程序B:

CALL B

假设子程序的第一条指令C的地址是00 0106h,PC的值是000106h,但是读程序地址总线(PAB)上的值是32位边界地址000104h,CPU在00 0104h地址开始读取4字节的代码,而第一个被执行的指令是C。

3.2 数据空间

C55x DSP 采用字寻址来读 / 写数据空间的 8 位、 16 位或 32 位数据。

1.字寻址(23位)

当CPU访问数据空间时,采用字寻址,即为每个16位的字分配一个23位宽的地址,下面说明了一行32位宽的存储器的地址分配,字0的地址为00 0100h,字1的地址为00 0101h。

字地址

100~001h 字0 字1

由于地址总线是24位宽,所以,当CPU读/写数据空间时,23位的地址左移一位,最低位补0。例如,一条指令在23位地址00 0102h上读一个字,读数据地址总线上传送的值是00 0204h,如下所示。

字地址:000 0000 0000 0001 0000 0010

读数据地址总线:0000 0000 0000 0010 0000 0100

2.数据类型

C55x DSP指令处理的数据类型有8位、16位和32位。

数据空间是采用字寻址,但C55x有专门的指令可以选择字的高字节或低字节,进行8位数据的处理。字节装载指令将从数据空间读取的字节进行0扩展或符号扩展,然后装入寄存器中;字节存储指令可将寄存器中的低8位数据存储到数据空间指定的地方。

字节装载和字节存储指令

| 指 令 |

存取的字节 |

操 作 |

| MOV high_byte(Smem) , dst MOV low_byte(Smem) , dst MOV high_byte(Smem)<<#SHIFTW , ACx MOV low_byte(Smem) <<#SHIFTW , ACx |

Smem(15~8) Smem(7~0) Smem(15~8) Smem(7~0) |

字节装载 |

| MOV src , high_byte(Smem) MOV src , low_byte(Smem) |

Smem(15~8) Smem(7~0) |

字节存储 |

当CPU存取长字时,存取地址是指32位数据的高16位(MSW)的地址,而低16位(LSW)的地址取决于MSW的地址。具体说明如下所示。

如果MSW的地址是偶地址,则LSW的地址加1。

字地址

100~001h MSW LSW

如果MSW的地址是奇地址,则LSW的地址减1。

字地址

100~001h LSW MSW

对于已确定地址的MSW(LSW),将其地址的最低有效位取反,可得到LSW(MSW)的地址。

3.数据空间的数据结构

下面通过实例来说明数据在数据空间是如何存储的。有7种变长的数据存储在32位宽的存储器中。

根据表2-7和图2-10可以看出,为了存取一个长字必须参考它的MSW,C的存取地址是00 0102h,D的存取地址是00 0105h;字地址也可以存取字节,如在地址00 0107h上,同时存放了数据F(高字节)和数据G(低字节)。利用表2-6中的专用指令可以进行字节的存取。

表2-7 数据长度及地址分配

| 数 据 |

数据类型 |

地 址 |

| A |

字节 |

00 0100h(低字节) |

| B |

字 |

00 0101h |

| C |

长字 |

00 0102h |

| D |

长字 |

00 0105h |

| E |

字 |

00 0106h |

| F |

字节 |

00 0107h(高字节) |

| G |

字节 |

00 0107h(低字节) |

图2-10 存储器中的指令

| 字 地 址 |

字 0 |

字 1 |

|

| 00 0100h~00 0101h |

A |

B |

|

| 00 0102h~00 0103h |

C(31~16) |

C(15~0) |

|

| 00 0104h~00 0105h |

D(15~0) |

D(31~16) |

|

| 00 0106h~00 0107h |

E |

F |

G |

3.3 I/O空间

C55x DSP的I/O空间与数据/程序空间是分开的,采用16位宽的字寻址,即为每个字分配一个16位地址,其寻址范围为64K字,如下所示:

|

地址

I/O

空间

|

|

|

0000h

~

FFFFh

|

64K

字

|

访问数据堆栈时,CPU将SPH和SP连接成XSP

XSP包含了一个最后推入数据堆栈的23位地址,其中SPH里是7位的主数据页,SP指向该页上的一个字。

CPU在每推入一个值入堆栈前,减小SP值;从堆栈弹出一个值以后,增加SP值。在堆栈操作中,SPH的值不变。

访问系统堆栈时CPU将SPH和SSP连接成XSSP。

XSSP包含了一个最后推入系统堆栈的值的地址

CPU在每推入一个值进堆栈前,减小SSP值;从堆栈弹出一个值以后,增加SSP值。在堆栈操作中,SPH的值不变

SSP可以与SP关联,也可以独立于SP

如果选择32位堆栈配置,则修改SSP与SP的方法一样

如果选择双16位堆栈配置,则SSP与SP独立,SSP只有在自动环境切换时才能被修改

一种配置使用快返回过程

另外两种使用慢返回过程

通过给32位复位向量的第29、28位填入适当值,可以选择一种堆栈配置方式

复位向量的低24位就是复位中断服务子程序(ISR)的起始地址

PC装的是I单元里1~6个字节代码的24位地址

一个8位的循环现场(loop context)寄存器存放激活循环记录

CPU执行中断或调用时,保存当前的循环现场,然后清零该寄存器,为新的子程序创建循环现场。当CPU从子程序返回时,再在该寄存器恢复原来的循环现场。

返回地址保存在寄存器RETA中

循环现场保存在寄存器CFCT中

用专门的32位装入和存储指令可同时读/写RETA 和CFCT

在慢返回过程里,返回地址和循环现场保存在堆栈里(在存储器里),当CPU从子程序返回时,这些数据的恢复速度取决于访问存储器的速度

5 中断和复位操作

5.1 中断概述

C55x支持32个ISR。有些ISR可以由软件或硬件触发,有些只能由软件触发。

当CPU同时收到多个硬件中断请求时,CPU会按照预先定义的优先级对它们做出响应和处理。

可屏蔽中断:可以通过软件来加以屏蔽

不可屏蔽中断:不能被屏蔽

所有的软件中断都是不可屏蔽中断

DSP处理中断的步骤

(2)响应中断请求。CPU必须响应中断。如果是可屏蔽中断,响应必须满足某些条件。如果是不可屏蔽中断,则CPU立即响应。

(3)准备进入中断服务子程序。

CPU要执行的主要任务有:

完成当前指令的执行,并冲掉流水线上还未解码的指令

自动将某些必要的寄存器的值保存到数据堆栈和系统堆栈

从用户实现设置好的向量地址获取中断向量,该中断向量指向中断服务子程序

CPU执行用户编写的ISR。ISR以一条中断返回指令结束,自动恢复步骤(3)中自动保存的寄存器值。

☼ 注意:

外部中断只能发生在CPU退出复位后的至少3个周期后,否则无效;

在硬件复位后,不论INTM位的设置和寄存器IER0、IER1的值如何,所有的中断都被禁止,直到通过软件初始化堆栈后才开放中断。

无论硬件何时请求一个可屏蔽中断,在一个中断标志寄存器里就有相应的中断标志置位。该标志一旦置位,相应的中断还必须使能,否则不会得到处理。

C55x的不可屏蔽中断有:

硬件中断/RESET。如果引脚/RESET为低电平,则触发了一个DSP硬件复位和一个中断(迫使执行复位ISR)。

硬件中断/NMI。如果引脚/NMI为低电平,则CPU必须执行相应的ISR。 /NMI提供了一种通用的无条件中断DSP的硬件方法。

软件中断。所有软件中断可用表2-37所示的指令初始化。

所有当前指令全部终止,指令流水清空,CPU寄存器复位

7 软件复位

不影响其它寄存器