S3C2440如何设置系统时钟

时钟控制逻辑给整个芯片提供3种时钟:FLCK用于CPU核;HCLK用于AHB总线上的设备(如:CPU核、存储控制器、中断控制器、LCD控制器、DMA等);PCLK用于APB总线上的设备(如:WATCHDOG、IIS、I2C、PWM定时器、MMC接口、ADC、UART、GPIO、RTC、SPI等)。

S3C2440 CPU主频可达400MHz,开发板上的外接晶振为12M,通过时钟控制逻辑的PLL(锁相环电路)来倍频这个系统时钟。

SC2440上有两个PLL,分别是MPLL,UPLL,UPLL专用于USB设备,常用频率为48MHz和96MHz;MPLL用于设置FCLK、HCLK、PLCK。

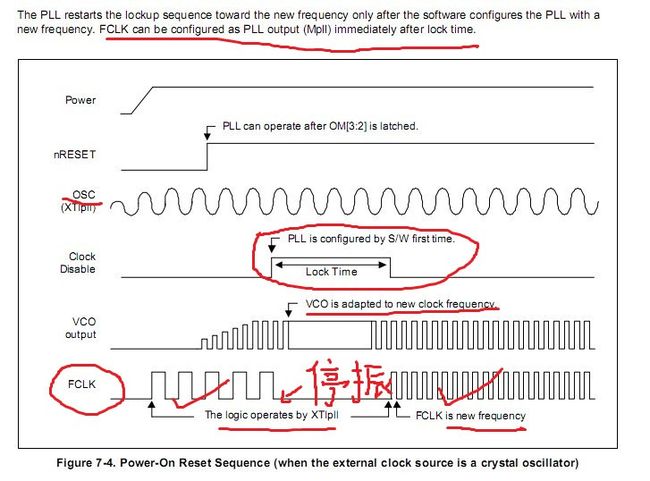

上电时,PLL并没有被启动,FCLK=Fin=12MHz,若要提高系统时钟,需要软件来启动PLL。下面我们介绍一下如何启动MPLL?

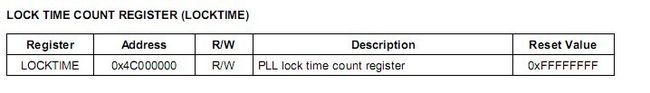

我们一般在程序的开头首先设置MPLL等几个寄存器,设置好之后需要等待一段时间(此时CPU停振),这段时间我们称为Lock Time(由我们自己设定,一般使用默认值),Lock Time过后,FCLK的输出才稳定,系统时钟就提高到你所先要的频率啦。下面是LOCKTIME的默认参数:

那么我们该怎么设置MPLL呢?有什么公式可以参考呢?

通过在片内集成的锁相环:MPLL可对输入的Fin=12MHz的晶振频率进行倍频。S3C2440使用了三个倍频因子MDIV、PDIV和SDIV来设置倍频,通过寄存器MPLLCON设置倍频因子。其中MPLLCON寄存器用于设置处理器内核时钟主频FCLK,其输入输出频率间的关系为 :

FCLK=MPLL=(2*m*Fin)/(p*2^s)

其中m=(MDIV+8), p=(PDIV+2), s=SDIV。

所以我们只要去设置PLLCON里面的MDIV、PDIV、SDIV就相当于设置好了MPLLCON。假如我们想让FCLK=400MHz,那么这三个参数该如何取值呢?

从上面这个图上我们可以发现,三星公司建议的一些经典的参数值,我们看到当Input Frequency取12MHz的时候,Output Frequency输出405MHz(接近400MHz),此时MDIV取0X7F,PDIV取0X02,SDIV取0x1。

从上面这个图我们可以发现,MDIV、PDIV、SDIV这三个倍频因子,分别位于MPLLCON寄存器的[19:12],[9:4],[1:0],配合上面的经典值。