七、mini2440裸机程序之定时器中断(1)时钟&电源管理介绍

一、简介

系统时钟&电源管理包含了3个部分 : 时钟控制 , USB控制 , 电源控制 .

1)时钟控制 : 时钟控制逻辑可以用来产生必要的时钟信号包括用于 CPU 的 FCLK .用于AHB总线设备的HCLK , 还有用于APB总线设备的PCLK , 还有专用于USB模块的时钟(48MHz) .

2)电源控制 : S3C2440A有多种电源管理方案来保证一个给定任务的最佳电源消耗 . 拥有以下4种模式:

①NORMAL 模式 : 这个模式下提供给CPU的时钟跟S3C2440A的外设时钟是一样的 , 当所有外设都被打开时 , 电源消耗会达到最大 . 电源控制块允许用户通过软件设置来控制这些外设的操作 . 比如 : 如果一个定时器不需要 , 用户可以禁止定时器时钟(CLKCON寄存器)来减少电源消耗 .

②SLOW模式 : Non-PLL模式 , 这个模式下使用的是外部时钟(XTlpll或者EXTCLK)直接作为FCLK而不通过PLL . 这个模式下电源消耗仅仅依赖于外部时钟频率 .

③IDLE模式 : 为所有外设提供时钟 , 但是不外CPU提供时钟(FCLK) . 任何对CPU的中断请求都能够从IDLE模式唤醒 .

④SLEEP模式 : 禁止内部电源 . 这样在这个模式下由于CPU和内部逻辑除了wake-up逻辑没有电源消耗了 . 不过在这个模式下要求两个独立的供电源 . 一个用于wake-up逻辑 . 另个用于其它内部逻辑包括CPU,和其它需要被控制电源开关. 从SLEEP模式下唤醒可以通过EINT[15:0]或者RTC报警中断来实现.

时钟

二、功能描述

1)时钟体系架构 :

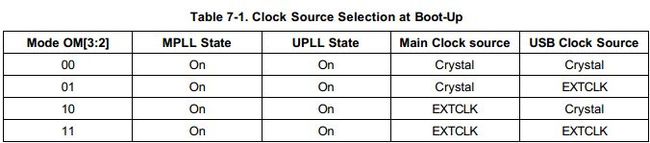

2)时钟源选择

注:

①尽管MPLL在复位之后开始 , 但是MPLL输出(Mpll)仍不会被作为系统时钟直到软件写有效设置到MPLLCON寄存器 . 在有效设置之前 , 外部晶振或者外部时钟源被直接用于系统时钟 .即使用户不想改变MPLLCON的默认值 , 用户仍需要写一个相同值到MPLLCON寄存器.

②当OM[1:0]为'11'时 , OM[3:2]被用于决定一个测试模式 .

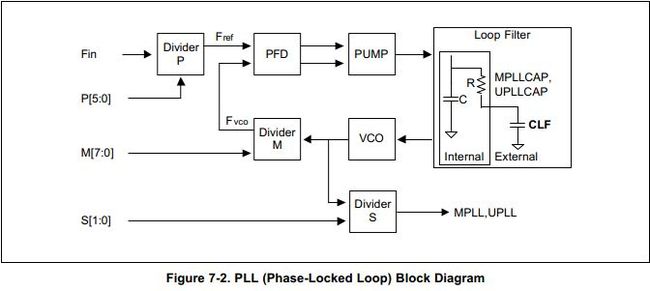

三、锁相环(PHASELOCKED LOOP : PLL)

在时钟产生器里的MPLL , 是一个电路 , 使一个输出信号和一个参考输入信号同步于频率和相位 . 在这些应用上 , 包括了以下基本模块:

注:

① VCO ( voltage controlled oscillator ) : 用于产生一个与输入DC电压频率成比例的输出频率 .

②DividerP : 倍频器P 用于提高输入频率(Fin)的频率

③DividerM : 倍频器M用于提高VCO输出频率输入到PFD.

④DividerS : 倍频器S用于提高VCO输出频率Mpll(从MPLL模块输出的频率) .

输出时钟频率Mpll与参考输入时钟频率Fin的关系如下 :

时钟产生器里的UPLL在各方面都与MPLL类似 .

下面描述以下几个模块:

①phase frequencydetector( 相位频率检测器PFD )

PFD监视Fref(参考频率)和Fvco(VCO输出频率)的相位差 , 并且一但有相位差被检测到则产生一个控制信号(跟踪信号) .

②charge pump(PUMP)

PUMP转换PFD控制信号改变通过外部滤波器(用于驱动VCO)的电平为一个比例变化.

③loop filter (环路滤波)

PFD产生给charge pump的控制信号 , 可能会产生大量的波纹每一次Fvco对比与Fref. 为例避免VCO过载 ,一个低通滤波器采样并从控制信号滤掉高频部分 . 滤波器是一个典型的单极性RC滤波器(一个电阻一个电容).

③voltagecontrolled oscillator(VCO)

从loop filter驱动VCO的输出电平, 导致它的晶振频率线性的增加或减少如平均的电压变化 . 当Fvco在频率和相位相匹配时 , PFD禁止发送控制信号给charge pump . 这样把电压稳定到loop filter .之后 VCO频率保存为一个常数 , PLL保持固定给系统时钟 .

四、时钟控制逻辑

时钟控制逻辑 决定哪个时钟源被使用 . 比如 , PLL时钟(Mpll)还是直接外部时钟(XTlpll或者EXTCLK). 当PLL被配置为一个新频率值 , 时钟控制逻辑禁止FCLK直到PLL输出稳定在使用PLL锁住时间 . 时钟控制逻辑在上电复位和从省电模式唤醒时被使用.

1)power-on reset(XTlpll)

以下图示演示了时钟在上电复位时的行为 . 晶体振荡器在几微秒内起振 . 当在OSC(XTlpll)时钟稳定之后nRESET被释放时 , PLL开始运行根据默认的PLL配置 . 然而PLL普遍认为在上电复位之后是不稳定 , 所以在软件重新配置PLLCON之前Fin直接被用于FCLK而不通过Mpll(PLLoutput) . 甚至在用户在复位之后不想改变PLLCON的默认值 , 也必须软件往PLLCON寄存器里写上一个相同值 .

PLL重新启动上锁序列方波向着新频率仅仅在软件配置PLL新频率之后 . FCLK可以在lock time之后立即被配置为PLL输出(Mpll).

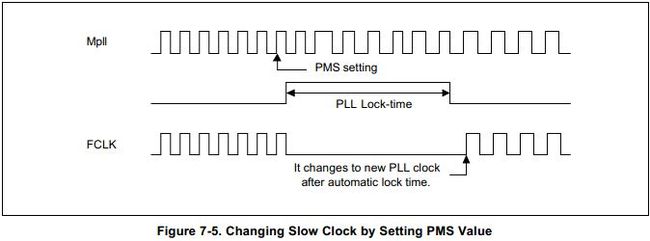

2)在Normal 运行模式改变PLL设置

在S3C2440A运行在normal模式下 , 用户可以改变方波序列通过写PMS值并且PLL锁住时间(PLL lock time)将被自动嵌入 . 在lock time期间 , 时钟不提供给S3C2440的内部模块 . 如下所示:

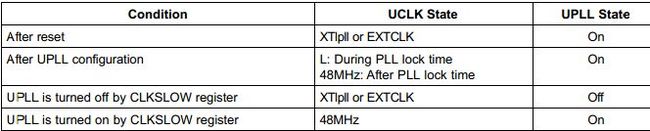

3)USB时钟控制

USB主设备接口和USB设备接口需要48Mhz时钟 . 在S3C2440A里 , USB专用PLL产生48Mhz用于USB . UCLK不被使用直到UPLL被配置.

4)FCLK , HCLK , PCLK

①FCLK用于ARM920T

②HCLK用于AHB总线相关控制器(ARM920T, memory controller , interrupt controller , LCD controller , DMA , USB host 模块).

③PCLK用于APB总线相关(WDT , IIS ,I2C , PWM timer , MMC接口 , ADC , UART , GPIO , RTC 和SPI ).

五、关于FCLK , HLCK和PCLK的比例选择.

S3C2440之处在FCLK,HCLK,PCLK之间使用不同的比例 . 这个比例由CLKDIVN控制寄存器的HDIVN和PDIVN域决定 . 具体如下所示:

在设置PMS值之后 , 需要设置CLKDIVN寄存器 . 设置CLKDIVN的值在PLL locktime之后有效 . 这个值在复位和改变电源管理模式下也是有效的 .

在设置这个值之后需要等待1.5个HCLK之后才有效 . 但是对于从默认的(1:1:1)到其它分频率(1:1:2, 1;2:2,1:2:4)的变化在1HCLK后也能有效 , 如下所示:

注意:

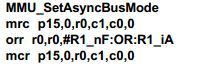

1.CLKDIVN需要小心设置,不能超过HCLK和PCLK的限制范围 .

2.假如HDIVN不是0 , CPU总线模式必须从高速总线模式改变为异步总线模式通过使用下面指令(S3C2440不支持同步总线模式) :

HDIVN不为0的时候并且CPU总线模式为快速总线模式 , CPU将运行使用HCLK . 这个特性可以被用于改变CPU序列方波为一半或者更多而不影响到HCLK和PCLK.

电源管理

电源管理模块通过软件来控制系统时钟来减少电源消耗 . 这些方案涉及到PLL , 时钟控制逻辑(FCLK,HCLK,PCLK)和唤醒信号.

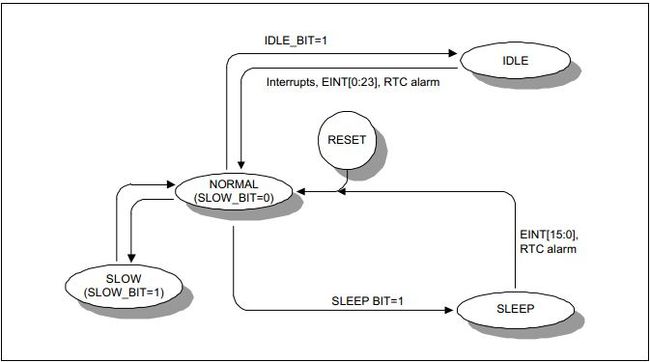

以下图示演示来S3C2440A的时钟分配:

电源管理状态转换表:

不同供电模式下的时钟和电源状态

注:

SEL : 可选( O , X ) , O : 使能 , X : 禁止 . OFF : 供电被关闭

1)S3C2440A有4种供电模式. 下面主要描述每种供电管理模式:

①normal模式

在normal模式下 , 所有的外设和基础模块(包含电源管理模块 , CPU核 , 总线控制器 , 内存管理器 , 中断控制器 , DMA, 和external master)都可以完全运行 . 但是 , 除了基础模块之外对于每一个外设的时钟 ,可以软件选择禁止来减少电源消耗.

②idle模式

在idle模式下 , 总线控制器 , 内存控制器 , 中断控制器,和电源管理模块的时钟使能 , 用于CPU核的时钟被禁止 . 如果要退出idle模式 ,EINT[23:0] , 或者 RTC报警中断 , 或者其它活动中的中断都可以使退出idle模式 . (如果GPIO模块没被打开 , 那么 EINT也是无效的)

③slow 模式(Non-PLL 模式)

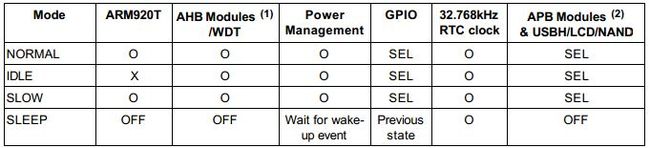

在slow模式下 , 通过使用一个慢速时钟和排除掉来自PLL的电源消耗 , 电源消耗可以被减少 . FCLK是输入时钟(XTlpll或者EXTCLK)的n分之一(不使用PLL) .分频比是由CLKSLOW控制寄存器的SLOW_VAL域和CLKDIVN控制寄存器决定的 . 如下图示:

在slow模式下 , PLL将被关闭来减少PLL的电源消耗 .当PLL在slow模式下被关闭着并且用户改变电源模式从slow模式到normal模式 , 那么PLL需要一段时钟稳点时间(PLLlock time) . 这个时钟稳定时间是自动被嵌入通过lock time count 寄存器的内部逻辑 . PLL稳定时间大概为300us左右 . 在PLL lock time期间 , FCLK来自慢速时钟 .

用户可以改变在PLL开启状态下的时钟频率通过使能CLKSLOW寄存器的SLOW模式位 . slow时钟在slow模式期间产生 ,如下图示:

如果用户从slow模式切换到normal模式通过禁止CLKSLOW寄存器的SLOW_BIT在PLL lock time之后 , 频率仅仅在slow模式被禁止之后才改变 . 如下图示:

如果用户从slow模式切换到normal模式通过禁止CLKSLOW寄存器的SLOW_BIT和MPLL_OFF位 , 频率仅仅在PLL lock time之后被改变 . 如下图示:

④sleep模式

模块不连接内部电源 , 所以 , 几乎没有电源消耗由于CPU和内部逻辑(除了wake-up逻辑) . 激化sleep模式要求两个独立的供电园 . 一个用于供给wake-up逻辑 . 一个用于供给其它内部逻辑包括CPU . 在sleep模式下 , 第二个电源(用于CPU和内部逻辑)需要被关闭 . sleep模式下的wakeup命令可以通过EINT[15:0]或者RTC闹钟中断下达 .

使能sleep模式的过程如下所示:

1)为sleep模式设置适当的GPIO配置 .

2)在INTMSK寄存器屏蔽所有中断

3)配置正确的唤醒源包括RTC警报 . (对应域wake-up源的EINTMASK寄存器的相应位不能被屏蔽)使SRCPND或者EINTPEND的相应位可以被设置 . 尽管wake-up源被下达但是EINTMASK的相应位被屏蔽 , wakeup可以发生但是SRCPND或者不被设置 .

4)设置USB pads位挂起模式(MISCCR[13:12]=11b)

5)保存所有有意义的值到GSTATUS[4:3]寄存器里 . 这些寄存器在sleep模式下被保藏着 .

6)配置MISCCR[1:0]位使在数据总线上D[31:0]加上拉电阻 . 如果有外部BUS握住 , 比如&$LVCH162245, 关闭pull-up resisters , 否则 , 开启pull-up resistors . 此外 , 内存相关管脚需要被设置后面两种类型: Hi-z 或者 Inactivestate.

7)禁止LCD通过清除LCDCON1.ENVID位.

8)读取rREFRESH和rCLKCON寄存器来填充TLB.

9)是SDRAM进入self-refresh模式通过设置REFRESH[22]=1b.

10)等待直到SDRAM self-refresh有效

11)设置MISCCR[19:17]=111b来使SDRAM信号(SCLK0,SCLK1和SCKE)在sleep模式期间被保护.

12)在CLKCON寄存器里设置sleep模式位

注意:当系统运行在nand启动模式下 ,在从sleep模式唤醒之后 , 硬件管脚配置(EINT[23:21])必须被设置为输入用于启动.

从sleep模式下唤醒过程:

1)如果有唤醒源被下达 , 内部复位信号被启动 . 在复位持续时间由内部16-bit计数逻辑和复位断言时间(计数如下:tRST = (65535/XTAL_frequency))所决定 .

2)检测GSTATUS2[2]来知道从sleep模式唤醒是否导致power-up的出现.

3)释放SDRAM信号保护通过设置MISCCR[19:17]=000b

4)配置SDRAM内存控制器

5)等待直到SDRAM self-refresh被释放 .大部分SDRAM需要所有SDRAM行的一个刷新周期.

6)GSTATUS[3:4]的信息可以用于用户个人目的因为这个值在sleep模式期间一直被保存着.

7)对于EINT[3:0] , 检测SRCPND寄存器 , 对于EINT[15:4]检测EINTPEND代替SRCPND(尽管EINTPEND的一些位被设置了SRCPND也不会被设置.)

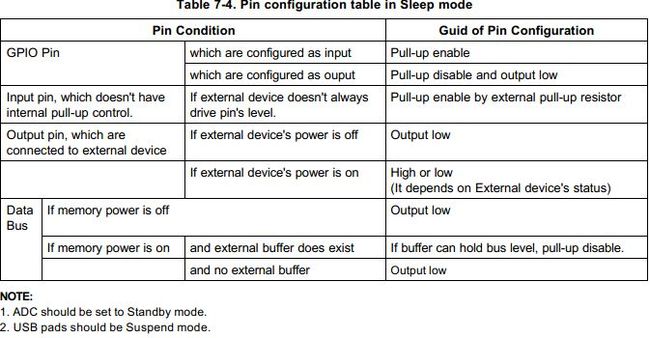

睡眠模式下的管脚配置表

唤醒信号EINT[15:0]

a)电平信号或沿跳变信号被发现在EINTn输入管脚.

b)EINTn管脚已经被配置为EINT在GPIO控制寄存器里

c)nBATT_FLT管脚必须为号电平 . 对于在GPIO控制寄存器里配置EINTn为外部中断管脚是很重要的.

一旦wake-up之后 , 相应EINTn管脚不再用于wakeup . 这就意味着管脚可以继续被用于外部中断请求管脚.

进入idle模式

假如CLKCON[2]被设为1 来进入idle模式 , S3C2440A将在一点延迟(直到电源控制逻辑从cpu接收到ACK信号)后进入idle模式.

PLL on/off

PLL只能在slow模式下关闭来减少电源消耗 , 如果在其它模式下关闭 , 那么MCU不能保证能正常运行.

当处理器处在slow模式并且尝试区改变它的状态到其它状态(开启PLL) , 那么SLOW_BIT必须在PLL稳定之后被清除来转换到其它状态.