APIC 中断属性详解

APIC:

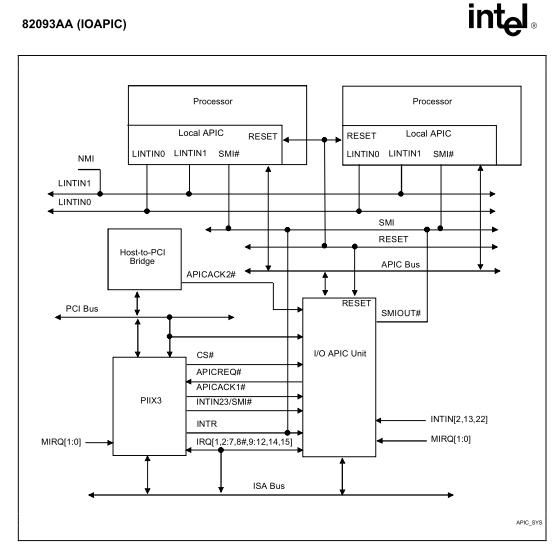

Intel APIC由一组中断输入信号,一个24*64bit的Programmable Redirection Table(PRT),一组register和用于从APIC BUS(FSB/QPI)上传送APIC MSG的部件组成,当南桥的IO device通过IOAPIC的interrupt lines产生interrupt,IOAPIC将根据内部的PRT table格式化成中断请求信息,并将该信息发送给目标CPU的LAPIC,再由LAPIC通知CPU进行处理。下图是一个基于Intel APIC的连接示意图,如下图所示IOAPIC上有24个interrupt pin,每一个pin都对应一个RTE,所以针对每一个interrupt pin都可以单独设定它的mask,触发方式(level,edge trigger),中断管脚的极性,传送方式,传送状态,目的地,中断向量等。

Programmable Redirection Table详细格式如下所示:

Bit Description:

[63:56] Destination Field—R/W. If the Destination Mode of this entry is Physical Mode (bit 11=0), bits

[59:56] contain an APIC ID. If Logical Mode is selected (bit 11=1), the Destination Field

potentially defines a set of processors. Bits [63:56] of the Destination Field specify the logical

destination address.

Destination Mode IOREDTBLx[11] Logical Destination Address

0, Physical Mode IOREDTBLx[59:56] = APIC ID

1, Logical Mode IOREDTBLx[63:56] = Set of processors

[55:17] Reserved.82093AA (IOAPIC)

[16] Interrupt Mask—R/W. When this bit is 1, the interrupt signal is masked. Edge-sensitive

interrupts signaled on a masked interrupt pin are ignored (i.e., not delivered or held pending).

Level-asserts or negates occurring on a masked level-sensitive pin are also ignored and have no

side effects. Changing the mask bit from unmasked to masked after the interrupt is accepted by

a local APIC has no effect on that interrupt. This behavior is identical to the case where the

device withdraws the interrupt before that interrupt is posted to the processor. It is software's

responsibility to handle the case where the mask bit is set after the interrupt message has been

accepted by a local APIC unit but before the interrupt is dispensed to the processor. When this

bit is 0, the interrupt is not masked. An edge or level on an interrupt pin that is not masked

results in the delivery of the interrupt to the destination.

[15] Trigger Mode—R/W. The trigger mode field indicates the type of signal on the interrupt pin that triggers an interrupt. 1=Level sensitive, 0=Edge sensitive.

[14] Remote IRR—RO. This bit is used for level triggered interrupts. Its meaning is undefined for edge triggered interrupts. For level triggered interrupts, this bit is set to 1 when local APIC(s) accept the level interrupt sent by the IOAPIC. The Remote IRR bit is set to 0 when an EOI message with a matching interrupt vector is received from a local APIC.

[13] Interrupt Input Pin Polarity (INTPOL)—R/W. This bit specifies the polarity of the interrupt

signal. 0=High active, 1=Low active.

[12] Delivery Status (DELIVS)—RO. The Delivery Status bit contains the current status of the

delivery of this interrupt. Delivery Status is read-only and writes to this bit (as part of a 32 bit

word) do not effect this bit. 0=IDLE (there is currently no activity for this interrupt). 1=Send

Pending (the interrupt has been injected but its delivery is temporarily held up due to the APIC

bus being busy or the inability of the receiving APIC unit to accept that interrupt at that time).

[11] Destination Mode (DESTMOD)—R/W. This field determines the interpretation of the

Destination field. When DESTMOD=0 (physical mode), a destination APIC is identified by its ID.

Bits 56 through 59 of the Destination field specify the 4 bit APIC ID. When DESTMOD=1 (logical mode), destinations are identified by matching on the logical destination under the control of theDestination Format Register and Logical Destination Register in each Local APIC.

Destination Mode IOREDTBLx[11] Logical Destination Address 0, Physical Mode IOREDTBLx[59:56] = APIC ID1, Logical Mode IOREDTBLx[63:56] = Set of processorsE 82093AA (IOAPIC)

[10:8]Delivery Mode (DELMOD)—R/W. The Delivery Mode is a 3 bit field that specifies how the APICs listed in the destination field should act upon reception of this signal. Note that certain

Delivery Modes only operate as intended when used in conjunction with a specific trigger Mode.

These restrictions are indicated in the following table for each Delivery Mode.

Mode Description

000 Fixed Deliver the signal on the INTR signal of all processor cores listed in the

destination. Trigger Mode for "fixed" Delivery Mode can be edge or level.

001 Lowest

Priority Deliver the signal on the INTR signal of the processor core that is

executing at the lowest priority among all the processors listed in the

specified destination. Trigger Mode for "lowest priority". Delivery Mode

can be edge or level.

010 SMI System Management Interrupt. A delivery mode equal to SMI requires an

edge trigger mode. The vector information is ignored but must be

programmed to all zeroes for future compatibility.

011 Reserved

100 NMI Deliver the signal on the NMI signal of all processor cores listed in the

destination. Vector information is ignored. NMI is treated as an edge

triggered interrupt, even if it is programmed as a level triggered interrupt.

For proper operation, this redirection table entry must be programmed to

“edge” triggered interrupt.

101 INIT Deliver the signal to all processor cores listed in the destination by

asserting the INIT signal. All addressed local APICs will assume their

INIT state. INIT is always treated as an edge triggered interrupt, even if

programmed otherwise. For proper operation, this redirection table entry

must be programmed to “edge” triggered interrupt.

110 Reserved

111 ExtINT Deliver the signal to the INTR signal of all processor cores listed in the

destination as an interrupt that originated in an externally connected

(8259A-compatible) interrupt controller. The INTA cycle that corresponds

to this ExtINT delivery is routed to the external controller that is expected

to supply the vector. A Delivery Mode of "ExtINT" requires an edge

trigger mode.

[7:0] Interrupt Vector (INTVEC)—R/W: The vector field is an 8 bit field containing the interrupt

vector for this interrupt. Vector values range from 10h to FEh.