Cortex M3 NVIC与中断控制

Cortex M3 NVIC与中断控制

宗旨:技术的学习是有限的,分享的精神的无限的。

一、NVIC概览 ——嵌套中断向量表控制器

NVIC 的寄存器以存储器映射的方式来访问,除了包含控制寄存器和中断处理的控制逻辑之外, NVIC 还包含了 MPU、 SysTick 定时器以及调试控制相关的寄存器。

NVIC 共支持 1 至 240 个外部中断输入(通常外部中断写作 IRQs)。具体的数值由芯片厂商在设计芯片时决定。此外, NVIC 还支持一个“永垂不朽”的不可屏蔽中断( NMI)输入。

NVIC 的访问地址是 0xE000_E000。所有 NVIC 的中断控制/状态寄存器都只能在特权级下访问。不过有一个例外——软件触发中断寄存器可以在用户级下访问以产生软件中断。所有的中断控制/状态寄存器均可按字/半字/字节的方式访问。

二、中断配置

| 寄存器 |

名称 |

类型 |

地址 |

复位值 |

| ICTR |

中断控制类型寄存器 |

只读 |

0xE000E004 |

由配置定义 |

| STIR |

软件触发中断寄存器 |

只写 |

0xE000EF00 |

— |

| NVIC_ISER0~NVIC_ISER15 |

中断置使能寄存器 |

可读可写 |

0xE000E100~0xE000E13C |

0x00000000 |

| NVIC_ICER0~NVIC_ICER15 |

中断清使能寄存器 |

可读可写 |

0xE000E180~0xE000E1BC |

0x00000000 |

| NVIC_ISPR0~NVIC_ISPR15 |

中断置请求寄存器 |

可读可写 |

0xE000E200~0xE000E23C |

0x00000000 |

| NVIC_ICPR0~NVIC_ICPR15 |

中断清请求寄存器 |

可读可写 |

0xE000E300~0xE000E2BC |

0x00000000 |

| NVIC_IABR0~NVIC_IABR15 |

中断活跃位寄存器 |

只读 |

0xE000E300~0xE000E33C |

0x00000000 |

| NVIC_IPR0~NVIC_IPR15 |

中断优先级寄存器 |

可读可写 |

0xE000E400~0xE000E7EC |

0x00000000 |

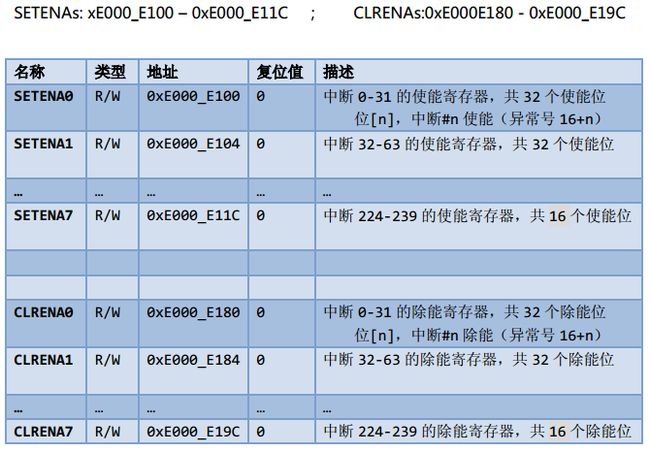

1、中断的使能与除能(SETENA/CLRENA)

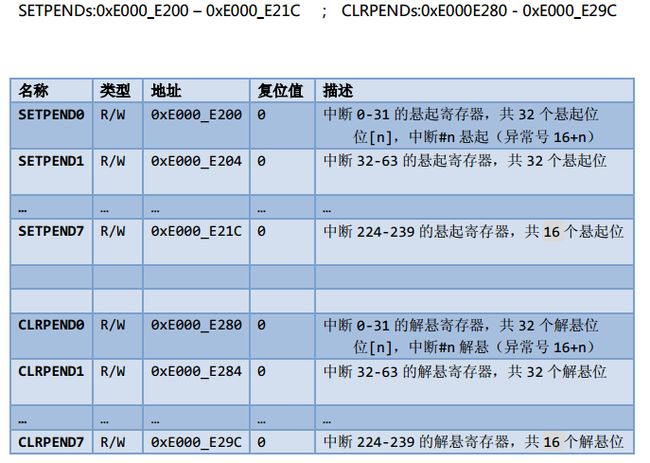

2、中断置请求与清请求(SETPEND/CLRPEND)

如果中断发生时,正在处理同级或高优先级异常,或者被掩蔽,则中断不能立即得到响应。此时中断被悬起。

3、中断活跃位寄存器

ACTIVE寄存器族 0xE000_E300_0xE000_E31C

三、软件中断

软件中断,包括手工产生的普通中断,能以多种方式产生。最简单的就是使用相应的SETPEND寄存器;而更专业更快捷的作法,则是通过使用软件触发中断寄存器STIR

软件触发中断寄存器STIR(地址:0xE000_EF00)

注意:系统异常( NMI,faults, PendSV等),不能用此法悬起。而且缺省时根本不允许用户程序改动NVIC寄存器的值。如果确实需要,必须先在NVIC的配置和控制寄存器(0xE000_ED14)中,把比特1(USERSETMPEND)置位,才能允许用户级下访问NVIC的STIR。

四、SysTick定时器

SysTick定时器被捆绑在NVIC中,用于产生SysTick异常(异常号: 15)。

Cortex-M3处理器内部包含了一个简单的定时器。因为所有的CM3芯片都带有这个定时器,软件在不同 CM3器件间的移植工作就得以化简。该定时器的时钟源可以是内部时钟( FCLK, CM3上的自由运行时钟),或者是外部时钟(CM3处理器上的STCLK信号)。不过, STCLK的具体来源则由芯片设计者决定,因此不同产品之间的时钟频率可能会大不相同。因此,需要检视芯片的器件手册来决定选择什么作为时钟源。

SysTick定时器能产生中断, CM3为它专门开出一个异常类型,并且在向量表中有它的一席之地。它使操作系统和其它系统软件在CM3器件间的移植变得简单多了,因为在所有CM3产品间,SysTick 的处理方式都是相同的。

SysTick控制及状态寄存器(地址:0xE000_E010)

SysTick重装载数值寄存器(地址:0xE000_E014)

SysTick当前数值寄存器(地址:0xE000_E018)

SysTick校准数值寄存器(地址:0xE000_E01C)

校准值寄存器提供了这样一个解决方案:它使系统即使在不同的CM3产品上运行,也能产生恒定的SysTick中断频率。最简单的作法就是:直接把TENMS的值写入重装载寄存器,这样一来,只要没突破系统的“弹性极限”,就能做到每10ms来一次 SysTick异常。如果需要其它的SysTick异常周期,则可以根据TENMS的值加以比例计算。只不过,在少数情况下, CM3芯片可能无法准确地提供TENMS的值(如, CM3的校准输入信号被拉低),所以为保险起见,最好在使用TENMS前检查器件的参考手册。