三种常用SoC片上总线的分析与比较

嵌入式系统是当今计算机工业发展的一个热点随着超大规模集成电路的迅速发展,半导体工业进入深亚微米时代,器件特征尺寸越来越小,芯片规模越来越大,可以在单芯片上集成上百万到数亿只晶体管

如此密集的集成度使我们现在能够在一小块芯片上把以前由CPU和若干I/O接口等数块芯片实现的功能集成起来,由单片集成电路构成功能强大的、完整的系统,这就是我们通常所说的片上系统SoC(System on Chip)由于功能完整,SoC逐渐成为嵌入式系统发展的主流

SoC相比板上系统,具有许多优点:

① 充分利用IP技术,减少产品设计复杂性和开发成本,缩短产品开发的时间;

② 单芯片集成电路可以有效地降低系统功耗;

③ 减少芯片对外引脚数,简化系统加工的复杂性;

④ 减少外围驱动接口单元及电路板之间的信号传递,加快了数据传输和处理的速度;

⑤ 内嵌的线路可以减少甚至避免电路板信号传送时所造成的系统信号串扰

SoC的设计过程中,最具特色的是IP复用技术即选择所需功能的IP(给出IP定义)核,集成到一个芯片中用由于IP核的设计千差万别,IP核的连接就成为构造SoC的关键片上总线(On-Chip Bus,OCB)是实现SoC中IP核连接最常见的技术手段,它以总线方式实现IP核之间数据通信与板上总线不同,片上总线不用驱动底板上的信号和连接器,使用更简单,速度更快一个片上总线规范一般需要定义各个模块之间初始化、仲裁、请求传输、响应、发送接收等过程中驱动、时序、策略等关系

由于片上总线与板上总线应用范围不同,存在着较大的差异,其主要特点如下:

① 片上总线要尽可能简单首先结构要简单,这样可以占用较少的逻辑单元;其次时序要简单,以利于提高总线的速度;第三接口要简单,如此可减少与IP核连接的复杂度

② 片上总线有较大的灵活性由于片上系统应用广泛,不同的应用对总线的要求各异,因此片上总线具有较大的灵活性其一,多数片上总线的数据和地址宽度都可变,如AMBA AHB支持32位~128位数据总线宽度;其二,部分片上总线的互连结构可变,如Wishbone总线支持点到点、数据流、共享总线和交叉开关四种互连方式;其三,部分片上总线的仲裁机制灵活可变,如Wishbone总线的仲裁机制可以完全由用户定制

③ 片上总线要尽可能降低功耗因此,在实际应用时,总线上各种信号尽量保持不变,并且多采用单向信号线,降低了功耗,同时也简化了时序上述三种片上总线输入数据线和输出数据线都是分开的,且都没有信号复用现象

片上总线有两种实现方案,一是选用国际上公开通用的总线结构;二是根据特定领域自主开发片上总线本文就目前SoC上使用较多的三种片上总线标准——ARM的AMBA、Silicore的Wishbone和Altera的Avalon进行讨论,对三者特性进行分析和比较

AMBA总线

AMBA(Advanced Microcontroller Bus Architecture)总线规范是ARM公司设计的一种用于高性能嵌入式系统的总线标准它独立于处理器和制造工艺技术,增强了各种应用中的外设和系统宏单元的可重用性AMBA总线规范是一个开放标准,可免费从ARM获得目前,AMBA 拥有众多第三方支持,被ARM公司90%以上的合作伙伴采用,在基于ARM处理器内核的SoC设计中,已经成为广泛支持的现有互联标准之一AMBA总线规范2.0于1999年发布,该规范引入的先进高性能总线(AHB)是现阶段AMBA实现的主要形式AHB的关键是对接口和互连均进行定义,目的是在任何工艺条件下实现接口和互连的最大带宽AHB接口已与互连功能分离,不再仅仅是一种总线,而是一种带有接口模块的互连体系

AMBA总线规范主要设计目的如下:

① 满足具有一个或多个CPU或DSP的嵌入式系统产品的快速开发要求;

② 增加设计技术上的独立性,确保可重用的多种IP核可以成功地移植到不同的系统中,适合全定制、标准单元和门阵列等技术;

③ 促进系统模块化设计,以增加处理器的独立性;

④ 减少对底层硅的需求,以使片外的操作和测试通信更加有效

AMBA总线是一个多总线系统规范定义了三种可以组合使用的不同类型的总线:AHB(Advanced High-performance Bus)、ASB(Advanced System Bus)和APB(Advanced Peripheral Bus)

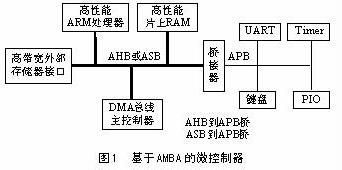

典型的基于AMBA的SoC核心部分如图1所示其中高性能系统总线(AHB或ASB)主要用以满足CPU和存储器之间的带宽要求CPU、片内存储器和DMA设备等高速设备连接在其上,而系统的大部分低速外部设备则连接在低带宽总线APB上系统总线和外设总线之间用一个桥接器(AHB/ASB-APB-Bridge)进行连接

AMBA的AHB适用于高性能和高时钟频率的系统模块它作为高性能系统的骨干总线,主要用于连接高性能和高吞吐量设备之间的连接,如CPU、片上存储器、DMA设备和DSP或其它协处理器等

其主要特性如下:

·支持多个总线主设备控制器;

·支持猝发、分裂、流水等数据传输方式;

·单周期总线主设备控制权转换;

·32~128位数据总线宽度;

·具有访问保护机制,以区分特权模式和非特权模式访问,指令和数据读取等;

· 数据猝发传输最大为16段;

·地址空间32位;

·支持字节、半字和字传输

AMBA的ASB适用于高性能的系统模块在不必要适用AHB的高速特性的场合,可选择ASB作为系统总线它同样支持处理器、片上存储器和片外处理器接口与低功耗外部宏单元之间的连接其主要特性与AHB类似,主要不同点是它读数据和写数据采用同一条双向数据总线

AMBA的APB适用于低功耗的外部设备,它已经过优化,以减少功耗和对外设接口的复杂度;它可连接在两种系统总线上

其主要特性如下:

·低速、低功耗外部总线;

·单个总线主设备控制器;

·非常简单,加上CLOCK和RESET,总共只有4个控制信号;

·32位地址空间;

·最大32位数据总线;

·读数据总线与写数据总线分开

·Wishbone总线

Wishbone最先是由Silicore公司提出的,现在已被移交给OpenCores组织维护由于其开放性,现在已有不少的用户群体,特别是一些免费的IP核,大多数都采用Wishbone标准

Wishbone总线规范是一种片上系统IP核互连体系结构它定义了一种IP核之间公共的逻辑接口,减轻了系统组件集成的难度,提高了系统组件的可重用性、可靠性和可移植性,加快了产品市场化的速度Wishbone总线规范可用于软核、固核和硬核,对开发工具和目标硬件没有特殊要求,并且几乎兼容已有所有的综合工具,可以用多种硬件描述语言来实现

Wishbone总线规范的目的是作为一种IP核之间的通用接口,因此它定义了一套标准的信号和总线周期,以连接不同的模块,而不是试图去规范IP核的功能和接口

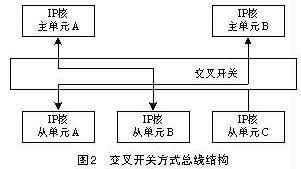

Wishbone总线结构十分简单,它仅仅定义了一条高速总线在一个复杂的系统中,可以采用两条Wishbone总线的多级总线结构:其一用于高性能系统部分,其二用于低速外设部分,两者之间需要一个接口这个接口虽然占用一些电路资源,但这比设计并连接两种不同的总线要简单多了用户可以按需要自定义Wishbone标准,如字节对齐方式和标志位(TAG)的含义等等,还可以加上一些其它的特性Wishbone的一种互连结构如图2所示

灵活性是Wishbone总线的另一个优点由于IP核种类多样,其间并没有一种统一的间接方式为满足不同系统的需要,Wishbone总线提供了四种不同的IP核互连方式:

·点到点(point-to-point),用于两IP核直接互连;

·数据流(data flow),用于多个串行IP核之间的数据并发传输;

·共享总线(shared bus),多个IP核共享一条总线;

·交叉开关(crossbar switch)(图2),同时连接多个主从部件,提高系统吞吐量

还有一种片外连接方式,可以连接到上面任何一种互连网络中例如说,两个有Wishbone接口的不同芯片之间就可以用点到点方式进行连接

Wishbone总线主要特征如下:

·所有应用适用于同一种总线体系结构;

·是一种简单、紧凑的逻辑IP核硬件接口,只需很少的逻辑单元即可实现;

·时序非常简单;

·主/从结构的总线,支持多个总线主设备;

·8~64位数据总线(可扩充);

·单周期读写;

·支持所有常用的总线数据传输协议,如单字节读写周期、块传输周期、控制操作及其它的总线事务等;

·支持多种IP核互连网络,如单向总线、双向总线、基于多路互用的互连网络、基于三态的互连网络等;

·支持总线周期的正常结束、重试结束和错误结束;

·使用用户自定义标记(TAG),确定数据传输类型、中断向量等;

·仲裁器机制由用户自定义;

·独立于硬件技术(FPGA、ASIC、bipolar、MOS等)、IP核类型(软核、固核或硬核)、综合工具、布局和布线技术等

Avalon总线

Avalon总线是Altera公司设计的用于SOPC(System On Programmable Chip,可编程片上系统)中,连接片上处理器和其它IP模块的一种简单的总线协议,规定了主部件和从部件之间进行连接的端口和通信的时序

Avalon总线的主要设计目的如下:

① 简单性,提供一种非常易于理解的协议;

② 优化总线逻辑的资源使用率,将逻辑单元保存在PLD(Programmable Logic Device,可编程逻辑器件)中;

③ 同步操作,将其它的逻辑单元很好地集成到同一PLD中,同时避免复杂的时序

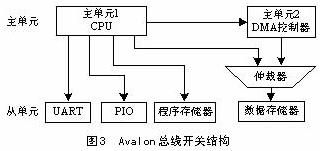

传统的总线结构中,一个中心仲裁器控制多个主设备和从设备之间的通信这种结构会产生一个瓶颈,因为任何时候只有一个主设备能访问系统总线Avalon总线的开关构造使用一种称之为从设备仲裁(Slave-side arbitration)的技术,允许多个主设备控制器真正地同步操作

当有多个主设备访问同一个从设备时,从设备仲裁器将决定哪个主设备获得访问权图3是一个多主设备同时访问存储器的例子在此系统中,高带宽外设,如100M以太网卡,可以不需暂停CPU而直接访问存储器通过允许存储访问独立于CPUAvalon开关结构优化了数据流,从而提高了系统的吞吐量

Avalon总线主要特性如下:

· 32位寻址空间;

·支持字节、半字和字传输;

·同步接口;

·独立的地址线、数据线和控制线;

·设备内嵌译码部件;

·支持多个总线主设备,Avalon自动生成仲裁机制;

·多个主设备可同时操作使用一条总线;

·可变的总线宽度,即可自动调整总线宽度,以适应尺寸不匹配的数据;

·提供了基于图形界面的总线配置向导,简单易用

三种片上总线比较

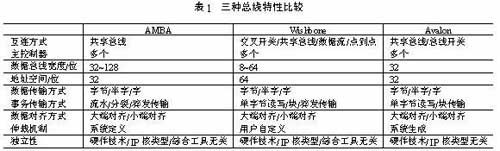

通过以上对三种总线特性的介绍,可以对三种总线作个比较,如表1所列

基于三种总线的特性,可以得出其应用的综合比较,如表2所列

三种总线各有特点,决定了其应用范围的不同AMBA总线规范拥有众多第三方支持,被ARM公司90%以上的合作伙伴采用,已成为广泛支持的现有互连标准之一Wishbone异军突起,其简单性和灵活性受到广大SoC设计者的青睐由于它是完全免费的,并有丰富的免费IP核资源,因此它有可能成为未来的片上系统总线互连标准Avalon主要用于Altera公司系列PLD中,最大的优点在于其配置的简单性,可由EDA工具快速生成,受PLD厂商巨头Altera极力推荐,其影响范围也不可忽视