jz2440SDRAM连接方式(七)

首先我们关心板子的sdram是怎么连接到这个上面去的,看一下原理图

两个片选信号同时连接到nGCS6

并且看出每个芯片的是16跟数据线X2 组成32位地址线。

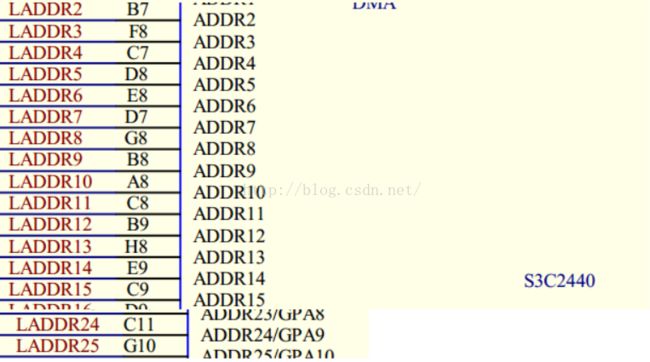

接着观察地址地址13根,练到LADDR2----LADDR14

BA0 BA1 接到ADDR24 ADDR25 【这个是片选择哪一个bank】

这里有一个疑问为什么不是接到三星2440 A0-A13 上呢?

这个跟CPU的寻址 以及内存芯片的寻址的单位有关。

1,先弄清楚第一个概念,对于CPU来说:

一个地址用32位来表示:0x30000000、0x40000000;

但是这个地址代表的地址空间是1个字节,也就是说CPU读取0x30000000这个地址得到的是一个字节的数据;

一个地址是多少位的地址跟这个地址代表的地址空间有多大是2码事。

CPU:

0x30000000 1字节

0x30000001 1字节

0x30000002 1字节

一个地址用32位来表示:0x30000000、0x40000000;

但是这个地址代表的地址空间是1个字节,也就是说CPU读取0x30000000这个地址得到的是一个字节的数据;

一个地址是多少位的地址跟这个地址代表的地址空间有多大是2码事。

CPU:

0x30000000 1字节

0x30000001 1字节

0x30000002 1字节

......

2,

① 对于JZ2440来说,SDRAM有2片,每一片的数据输出宽度是16bit,总共构成了具有32bit数据输出的内存,现在这块内存1次输出32bit的数据。

② 在这种情况下,读取SDRAM的一个地址得到的数据是4个字节

也就是说,CPU想得到一字节的数据的时候,要一次获取 sdram 中的四字节的数据,然后再在其中取出索要的数据。

SRAM地址

0x0000 0000 32bit

0x0000 0001 32bit

所以:

CPU发出0x30000000、0x30000001、0x30000002、0x30000003这4个地址的时候,访问的都必须是SDRAM的0地址

而CPU的地址线是直接连在SDRAM的地址线上的,中间又没有其他硬件或者软件做转换。

我们看0x30000001的最后一个字节,用2进制表示

0000 0000 地址0 ->sdram0

0000 0001 地址1

0000 0010 地址2

0000 0011 地址3

0000 0100 地址4 ->sdram1

CPU要想发出地址后得到正确数据

,

那么发出的地址的bit0、bit1是无效的,地址从bit2开始有效。

实际有效地址的最低位是从bit2开始的:

无论bit0、bit1的值是多少,bit2为0的时候访问的是SDRAM的0地址;

把CPU的ADDR3地址线接到SDRAM的AD1;

把CPU的ADDR4地址线接到SDRAM的AD2;

![]()

无论bit0、bit1的值是多少,bit2为0的时候访问的是SDRAM的0地址;

bit2为1的时候访问的是SDRAM的1地址;

bit3、bit2为10的时候访问的是SDRAM的2地址;

......

既然实际有效地址的最低位从bit2开始,那么把CPU的ADDR2地址线接到SDRAM的AD0;把CPU的ADDR3地址线接到SDRAM的AD1;

把CPU的ADDR4地址线接到SDRAM的AD2;

.......

CPU的ADDR0和ADDR1不用接。

然后我们从芯片手册也有指导我们如何连线:

这个只能数据位宽有关系:

其实这个也只跟位宽有关系

我们只需要统一单位就可以了!

总结一下:CPU一定是字节寻址(8bit)

内存芯片的寻址是看数据位宽

我们把统一单位的地址线连接起来就可以了。

比如A0是2的0次方字节 1字节

A1是2的1次方字节 2字节

A2是2的2次方字节 4字节

那么位宽8位 就是1字节 从A0开始连接

16位 就是2字节 从A1开始连接

以此类推

我们看一下SDRAM的原理 就是一个立方体, 行x列x几(bank)

寻址就非常简单,首先CPU发送第几个bank信号,对应ba0 ba1的值,

然后通过地址依次发 行 列 信号,怎么知道是行还是列就看

nSRAS nSCAS 行/列 有效管教是不是被置位了

还有一些其他管教的作用,翻译下。

| 外接管脚名 |

内接管脚名 |

全称 |

描述 |

| A2~A14 |

A0~A12 |

Address |

地址线 |

| D0 ~D31 |

DQ0~DQ31 |

Data Input/Output |

数据线 |

| A24,A25 |

BA0,BA1 |

Bank Address |

L-BANK片选信号 |

| DQM0~DQM3 |

LDQM, UDQM |

Data Input/Output Mask |

高,低字节数据掩码信号 |

| SCKE |

SCKE |

Clock Enable |

输入时钟有效信号 |

| SCLK |

SCLK |

Clock |

输入时钟 |

| nSCS0 |

nSCS |

General Chip Select |

片选信号(它与nGCS6是同一管脚的两个功能) |

| nSRAS |

nSRAS |

Row Address Strobe |

行地址选通信号 |

| nSCAS |

nSCAS |

Column Address Strobe |

列地址选通信号 |

| nWE |

newnWE |

Write Enable |

写入有效信号 |

当然之前调到了S3C2440有8个BANK,也就是8条线了,每条线的地址空间是128M,我们把内存芯片挂在第6根线上。

CPU每次访问只能访问一根线,

nSCS0就是所谓的片选信号,就是选这一片了。

这里还有一个问题bank信号为什么要连接在ADDR24 ADDR25

因为我们的芯片最后组成的大小是64M,我们发现不同大小的地址是不同的。

我们验证了CPU对于寻址这件事只有0-27条地址线发送地址的功能而已。

至于地址是多少是我们人工来干预的。

总共0-26 27地址线。

那么第25号线是 26根线组成最大寻址64M

高两位用来给bank寻址,这个线性空间64M 和128M就完全说通了。

CPU只负责给出地址,除了对于sdram的行列的信号 因为是分时复用做了一点支持。

看到了寄存器的某些位我们就大致比较清楚这个原因了。

硬件相关的内容说完了,我们就应该把我们这个芯片的一些参数信息告诉CPU,然后才能正常工作了。

所以我们参考芯片手册,将要配置到2440芯片寄存器的值:

- .long 0x22011110 //BWSCON (1)

- .long 0x00000700 //BANKCON0 (2)

- .long 0x00000700 //BANKCON1 (3)

- .long 0x00000700 //BANKCON2 (4)

- .long 0x00000700 //BANKCON3 (5)

- .long 0x00000700 //BANKCON4 (6)

- .long 0x00000700 //BANKCON5 (7)

- .long 0x00018005 //BANKCON6 (8)

- .long 0x00018005 //BANKCON7 (9)

- .long 0x008C04F4 //REFRESH (10)

- .long 0x000000B1 //BANKSIZE (11)

- .long 0x00000030 //MRSRB6 (12)

- .long 0x00000030 //MRSRB7 (13)

(1)

对 BANK7 不使用

UB/LB :

Bank 7 的WAIT 状态禁止:Bank7 数据总线宽度 32 位:

对 BANK6 不使用 UB/LB :Bank 6 的WAIT 状态禁止:Bank6 数据总线宽度 32 位:

对 BANK5 不使用 UB/LB :Bank 5 的WAIT 状态禁止:Bank5 数据总线宽度 8 位:

对 BANK4 不使用 UB/LB :Bank4 的WAIT 状态禁止:Bank4 数据总线宽度 16 位:

对 BANK3 不使用 UB/LB :Bank3 的WAIT 状态禁止:Bank3 数据总线宽度 16 位:

对 BANK2 不使用 UB/LB :Bank2 的WAIT 状态禁止:Bank2 数据总线宽度 16 位:

对 BANK1 不使用 UB/LB :Bank1 的WAIT 状态禁止:Bank1 数据总线宽度 16 位

(2)-(7) bankcon0-5 默认值

(8)(9)

BANK6,7 的

存储器类型是 同步DRAM;

nGCSn 前的地址建立时间 0 个周期;

nOE 前的片选建立时间 0 个时钟;

访问周期 1 个时钟;

nOE 后的片选保持时间 0 个时钟:

nGCSn 后的地址保持时间 0 个时钟:

Page 模式下的page 的访问周期 3 个时钟;

Page 模式配置 4个连续数据;

(10)

SDRAM 刷新使能;

SDRAM RAS 的充电时间是2个时钟:

SDRAM Semi Row cycle time (SDRAM 半行周期时间 )7个时钟:

刷新计数器是 0b100 1111 0100 = 1268 刷新周期 = (2^11 - 刷新计数 + 1) / HCLK = 781 / HCLK = 7.81us

(11) 使能突发模式,使能SDRAM 掉电模式,SCLK只在访问期间有效,Bank6/7 存储器映射 64MB/64MB

(12)(13) CAS等待时间是 3 个时钟周期,写突发长度固定,突发类型连续,突发长度 1.