S3C6410时钟初始化

个人原创,转载请注明出处: http://blog.csdn.net/hongkangwl/article/details/17070927

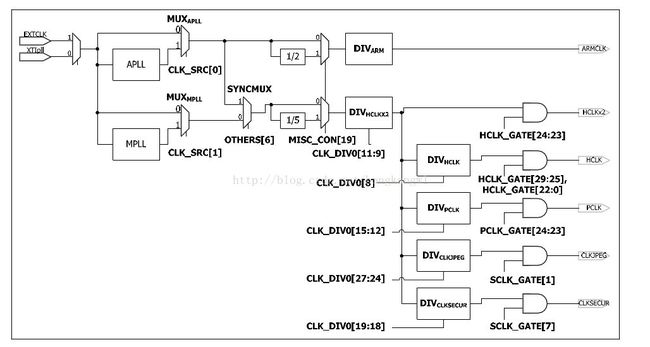

S3C6410有三个PLL,分别为APLL、MPLL和EPLL。

其中APLL产生ACLK,给arm core使用,

MPLL产生HCLKX2、HCLK和PCLK,

EPLL产生特殊的时钟,比如为USB提供48MHz时钟

可以看到,外部时钟(一般为12M)经过APLL后再经过设置分频系数DIVARM后产生供ARM核使用的ARMCLK;

外部时钟经过MPLL后经过分频系数DIV_HCLKX2后产生时钟HCLKX2;

时钟HCLKX2经过分频系数DIV_HCLK后产生时钟HCLK;

时钟HCLKX2经过分频系数DIV_PCLK后产生时钟PCLK;

一般在设置时钟时,三星官网有推荐的值,那么我们只需设置官方提供的几个系数就OK了。

S3C6410 系统时钟初始化步骤:

1.设置同步或异步模式;

2.设置时钟分频系数;

3.设置 PLL 控制器;

4.选择 PLL 输出时钟为系统时钟源。

时钟的设置涉及到如下几个寄存器的设置:

#define CLK_DIV0 0x7e00f020 #define OTHERS 0x7e00f900 #define MPLL_CON 0x7e00f010 #define APLL_CON 0x7e00f00c #define CLK_SRC 0x7e00f01c #define DIV_VAL ((0x0<<0)|(0x1<<9)|(0x1<<8)|(0x3<<12)) #define PLL_VAL ((1<<31)|(266<<16)|(3<<8)|(1<<0))

1,设置同步异步是通过others寄存器完成:

设置成同步模式通过如下代码完成:

ldr r0, =OTHERS ldr r1, [r0] bic r1,r1,#0xc0 str r1, [r0]2.设置时钟分频系数:

首先需要设置HCLKX2_RATIO,然后再设置ARM_RATIO、PCLK_RATIO、HCLK_RATIO,在这里我们设置ARM_RATIO=0、PCLK_RATIO=1、HCLK_RATIO=1、HCLKX2_RATIO=1,设置代码如下:

ldr r0, =CLK_DIV0 ldr r1, =DIV_VAL str r1, [r0]

3设置PLL控制器:

PLL控制寄存器有APLL_CON和MPLL_CON

在这里设置MDIV=266 PDIV=3 SDIV =1;

代码如下:

ldr r0, =MPLL_CON ldr r1, =PLL_VAL str r1, [r0]

经过设置后,根据上图中Fout的计算公式:FOUT= 266*12、(2*3) = 533M HZ;

APLL_CON的设置相似:

计算结果亦为533M HZ

4 时钟源设置

CLK_SRC

通过设置CLK_SRC的第0位和第一位,使后端的时钟分别为APLL 和MPLL,

设置如下:

ldr r0, =CLK_SRC mov r1, #0x3 str r1, [r0]

这样,设置完成后ARMCLK为533M HZ

HCLKX2= 533/(1+1) = 266M HZ

HCLK = HCLKX2 / (1+1 ) = 133MHZ

PCLK = HCLKX2 /(3+1) = 66M HZ