ARM GIC中断控制器介绍

Distributor–detecting, disabling, prioritizing, directing interrupts to CPU(s).CPU interfaces–asserting an interrupt indication to the CPUSupport max to 1020 interrupts

2 PPI,SPI and SGI

Peripheral interrupt

PPI : Private Peripheral Interrupt

specific to a single processor

SPI : Shared Peripheral Interrupt

Distributor can route to any of a specified combination of processors

Software-generated interrupt (SGI)

This is an interrupt generated by software writing to a GICD_SGIR register in the GIC. The system uses SGIs for interprocessor communication

ID0-ID15 are used for SGIs

ID16-ID31 are used for PPIs

3 Models for handling interrupts in MP core

1-N model

Only one processor handles this interrupt. The system must implement a mechanism to determine which processor handles an interrupt that is programmed to target more than one processor.

N-N model

All processors receive the interrupt independently. When a processor acknowledges the interrupt, the interrupt pending state is cleared only for that processor. The interrupt remains pending for the other processors.

According to GIC document(p3-33)

software generated interrupts (SGIs) using the GIC N-N model

peripheral (hardware) interrupts PPI and SPI using the GIC 1-N model.

4 GIC interrupt handling sequence1. The GIC determines the interrupts that are enabled.2. For each pending interrupt, the GIC determines the targeted processor or processors.3. For each CPU interface, the Distributor forwards the highest priority pending interrupt that targets that interface.4. Each CPU interface determines whether to signal an interrupt request to its processor, and if required, does so.5. The processor acknowledges the interrupt, and the GIC returns the interrupt ID and updates the interrupt state.6. After processing the interrupt, the processor signals End of Interrupt (EOI) to the GIC.

linux-arm中断系统之GIC

这几天长三角爆发禽流感,搞的连菜市场都不敢靠近了,颇有点SARS的架势,我真怀疑上帝是不是个程序猿,造人搞这么多bug,

H7N9的driver还没写好吧,害的我们只能不停的打patch,时不时来个oops。今天看了一个专家的解说:"H7N9基因有八节,其中H7的部分是来自浙江的野鸟,

N9的部分是来自韩国的野鸟,那么其余的六节相信是来自长江以北",好吧,又是你们韩国。

1.“站的高尿的远”

GIC为中断控制器,不要和ARM core的中断搞混了,这些中断都是连接到ARM core的IRQ或者FIQ上的。

要了解arm中断系统,GIC绝对不容错过,好先付上一张大家都能百度到的图片。

++和*可以先不用考虑,用于安全模式。

GIC可以用于单核多核系统,这时候要抛开单片机的简单中断了,从图上看有SGI(Software-generated interrupt)、PPI(Private peripheral interrupt )、SPI(Shared peripheral interrupt),顾名思义SGI为软件可以触发的中断,经常用于各个core之间的通信,PPI为每个core的私有外设中断,SPI为各个core公用的中断。

SGI:0~15

PPI:16-31

SPI:32~1019

2. follow me

通常把GIC分成两个部分,分发器(Distributor)和CPU接口。

分发器其实应该叫汇聚器,在IC的后端设计中,layout会把各个模块引过来的中断线混接到GIC上(就是上面说的三种中断),然后把混聚合的中断接到CPU的irq线上。

这样core就有触觉了。

3. 模型

既然是中断控制器,必不可少的是总的中断使能,各个子中断使能,优先级排序,在多核系统中对于SGI还可以指定中断发往哪个CPU core。

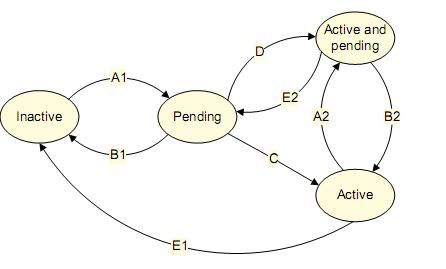

如何才能保证中断不丢失呢?啊对了就是pending,distributor会把收集来的中断,先缓存一下,依次交给CPU处理,cpu读取一个中断,其实

就是读取一个寄存器,只不过这个寄存器存放的是中断号,这时候中断的状态由pending转为active,cpu处理完了以后,将中断号写入GIC,告诉

GIC我处理完了,你可以歇歇了。