大小端模式

偶:注意:大小端的高低位数据是按地址来计算的。如0x1001,10是高位字节,01是低位字节。char *s="abcd",a是高位字节……

偶:记忆:小端是内存低地址放低位数据。大端反之。

所谓的大端模式,是指数据的低位(就是权值较小的后面那几位)保存在内存的高地址中,而数据的高位,保存在内存的低地址中,这样的存储模式有点儿类似于把数据当作字符串顺序处理:地址由小向大增加,而数据从高位往低位放;

所谓的小端模式,是指数据的低位保存在内存的低地址中,而数 据的高位保存在内存的高地址中,这种存储模式将地址的高低和数据位权有效地结合起来,高地址部分权值高,低地址部分权值低,和我们的逻辑方法一致。

为什么会有大小端模式之分呢?这是因为在计算机系统中,我们是以字节为单位的,每个地址单元都对应着一个字节,一个字节为 8bit。但是在C语言中除了8bit的char之外,还有16bit的short型,32bit的long型(要看具体的编译器),另外,对于位数大于 8位的处理器,例如16位或者32位的处理器,由于寄存器宽度大于一个字节,那么必然存在着一个如果将多个字节安排的问题。因此就导致了大端存储模式和小 端存储模式。例如一个16bit的short型x,在内存中的地址为0x0010,x的值为0x1122,那么0x11为高字节,0x22为低字节。对于 大端模式,就将0x11放在低地址中,即0x0010中,0x22放在高地址中,即0x0011中。小端模式,刚好相反。我们常用的X86结构是小端模 式,而KEIL C51则为大端模式。很多的ARM,DSP都为小端模式。有些ARM处理器还可以由硬件来选择是大端模式还是小端模式。

下面这段代码可以用来测试一下你的编译器是大端模式还是小端模式:short int x;

char x0,x1;

x=0x1122;

x0=((char*)&x)[0]; //低地址单元

x1=((char*)&x)[1]; //高地址单元

若x0=0x11,则是大端; 若x0=0x22,则是小端......

上面的程序还可以看出,数据寻址时,用的是低位字节的地址。

偶:另外:网络传输说的大小端是这样的:

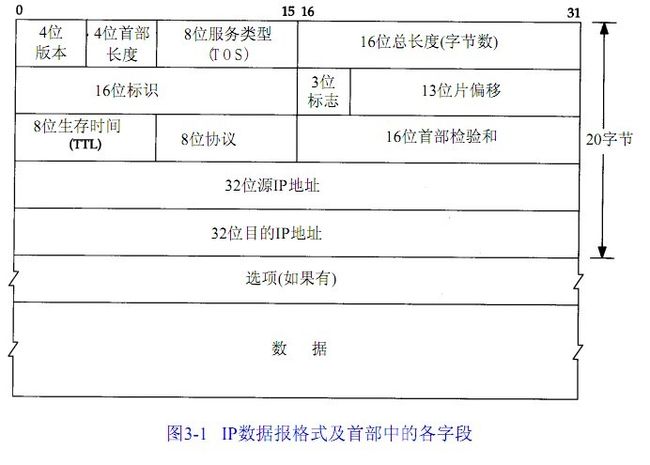

分析图3 - 1中的首部。最高位在左边,记为0 bit;最低位在右边,记为31 bit。

4个字节的32 bit值以下面的次序传输:首先是0~7 bit,其次8~15 bit,然后1 6~23 bit,

最后是24~31 bit。这种传输次序称作big endian字节序。由于T C P / I P首部中所有的二进制整数

在网络中传输时都要求以这种次序,因此它又称作网络字节序。以其他形式存储二进制整数

的机器,如little endian格式,则必须在传输数据之前把首部转换成网络字节序。