基于JESD204B的LMK04826时钟芯片开发笔记

第一章:LMK04826功能介绍

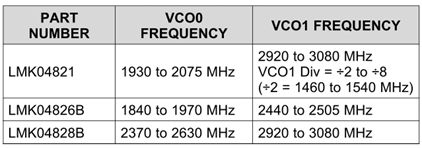

LMK0482X系列是德州仪器推出的号称业界最高性能的时钟调节器芯片系列,该系列有3款芯片,分别为LMK04821、LMK04826以及LMK04828,并且这3款芯片的输出时钟都支持目前最新的JESD204B协议。

其性能描述如下:

- 支持JESD204B

- 超低的时钟抖动和噪声

- 输出14对差分时钟

- 7对可作为JESD204B的SYSREF时钟

- 最大时钟输出频率可达3.1GHz

- 输出的差分时钟电平标准可编程选择:包括LVPECL、LVDS、HSDS以及LCPECL

- 双PLL结构

- PLL2的VCO分频系数为1-32

- 输出时钟精确的数字延时、模拟延时以及动态延时

- 多种工作模式:双PLL、单PLL以及时钟分发模式

- 3.3V供电

- QFN封装

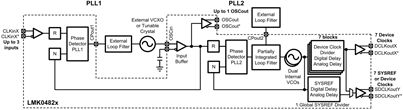

LMK04821、LMK04826以及LMK04828这3款芯片的不同之处在于支持的VCO不同,如下图所示,另外该系列芯片在最终的输出级设置了VCO0和VCO1可选,扩大了芯片的输出时钟范围。

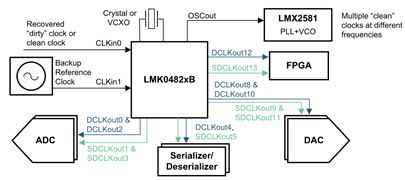

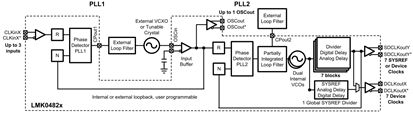

如下图所示为该系列芯片的简单应用示意图供大家有个初步印象:

如下图所示为该系列芯片的管脚分布及定义,咱们下面逐一介绍:

管脚1、2:第0路Device CLK差分输出

管脚3、4:第1路SYSREF/Device CLK差分输出

管脚5:该芯片的复位输入或者是通用GPIO

管脚6:该芯片的时钟同步输入端口或者是连续SYSREF CLK请求输入端口

管脚7、8、9:没用,悬空即可

管脚10:电源输入

管脚11:LDO旁路电容,外接10uf到地

管脚12:LDO旁路电容,外接0.1uf到地

管脚13、14:第3路SYSREF/Device CLK差分输出

管脚15、16:第2路Device CLK差分输出

管脚17:电源输入

管脚18:芯片的SPI配置CS信号

管脚19:芯片的SPI配置SCK信号

管脚20:芯片的SPI配置SDIO信号

管脚21:电源输入

管脚22、23:第5路SYSREF/Device CLK差分输出

管脚24、25:第4路Device CLK差分输出

管脚26:电源输入

管脚27、28:第6路Device CLK差分输出

管脚29、30:第7路SYSREF/Device CLK差分输出

管脚31:可编程的状态监测I/O管脚

管脚32:PLL1的电荷泵输出

管脚33:电源输入

管脚34、35:PLL1的参考时钟输入1、零延迟模式下的外部反馈时钟输入、外部VCO输入

管脚36:电源输入

管脚37、38:PLL1的参考时钟输入0

管脚39:电源输入

管脚40、41:晶振的时钟输出端口、PLL1的参考时钟输入2

管脚42:电源输入

管脚43、44:PLL2的参考时钟输入、PLL1的反馈时钟输入

管脚45:电源输入

管脚46:PLL2的电荷泵输出

管脚47:电源输入

管脚48:可编程的状态监测I/O管脚

管脚49、50:第9路SYSREF/Device CLK差分输出

管脚51、52:第8路Device CLK差分输出

管脚53:电源输入

管脚54、55:第10路Device CLK差分输出

管脚56、57:第11路SYSREF/Device CLK差分输出

管脚58:可编程的状态监测I/O管脚

管脚59:可编程的状态监测I/O管脚

管脚60、61:第13路SYSREF/Device CLK差分输出

管脚62、63:第12路Device CLK差分输出

管脚64:电源输入

DAP:扇热盘,接地

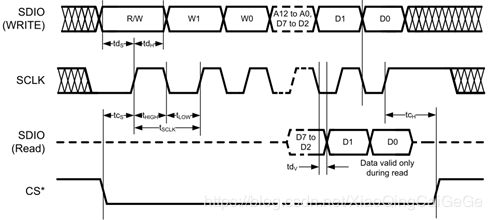

LMK0482X的配置采用的是SPI方式,其配置规则简要描述为:

- 写操作时,CS信号为低电平时,SDIO的数据在SCK上升沿写进芯片,写数据格式为1bit的读写控制位+2bit的0+13bit地址+8bit数据。

- 读操作时,先写入1bit的读写控制位+2bit的0+13bit地址,然后在接下来SCK的上升沿获取8bit数据。

需要注意的是该芯片支持3线和4线模式,其配置时序可以如下表示:

接下来咱们参考datasheet来具体介绍LMK0482X的各个功能:

- 总体介绍

LMK0482X系列芯片功能非常的灵活,其最典型的应用是双PLL级联的JESD204B系统。但是对于传统的应用来说,也是没问题的。需要注意的是Device CLK不提供单端输出,只有OSCout管脚可以提供LVCMOS单端输出。另外,除了双PLL应用,LMK0482X也可以配置成单PLL或者时钟分发模式。

-

- 抖动清除

LMK0482X系列芯片的双PLL结构保证了在很宽的输出频率范围内还可以输出最低抖动的时钟。第一级PLL(PLL1)被外部的参考时钟驱动,第二级PLL(PLL2)由VCXO或者可调晶振提供高精度、低噪声的二级参考时钟。经过这两级PLL,输出时钟的精度将会大大提高。

-

- 支持JESD204B

LMK0482X系列芯片共输出7对JESD204B Device CLK和7对SYSREF CLK,其中每个Device CLK对应一个SYSREF CLK。对于那些非JESD204B的应用,SYSREF CLK同样可以编程为Device CLK。

-

- 3个PLL1参考时钟输入

PLL1的输入参考时钟包括管脚CLKin0,CLKin1以及CLKin2,任选一个作为时钟输入即可,选择的规则由配置寄存器参数决定。

-

- VCXO/Crystal 缓存输出

LMK0482X系列芯片提供OSCout输出,该输出其实就是PLL1的反馈输入,也是PLL2的参考时钟输入,芯片的该功能其实就是为了在其编程之前可以提供一个时钟给控制器工作,控制器编程再配置LMK0482X。OSCout输出可以为LVDS、LVPECL以及LVMOS电平。

-

- 频率保持

LMK0482X具有频率保持的功能,当外部参考时钟丢失后,输出频率还能保持最小的漂移,直到外部参考时钟恢复。

-

- 内部VCOs

LMK0482X内部的PLL2有两个VCO,实际应用时根据不同频率需求选择。

-

- VCO1分频

LMK04821芯片有一个额外的功能,VCO1在反馈之前还可以进行分频。

-

- 外部VCO模式

当不需要内部VCO时,该系列芯片还可以从Fin管脚引入外部的VCO。

-

- 时钟分发

PLL2的输出可以分发为14路,每路都可以各自分频。如果再算上OSCout输出,则该芯片最多输出15路时钟。

-

- Device CLK分频

7路Device CLK都可以分别的分频,分频系数为1~32.

-

- SYSREF CLK分频

7路SYSREF CLK统一分频,分频系数为8~8191.

-

- Device CLK延迟

Device CLK具有延迟的功能,其包括模拟延迟和数字延迟。

模拟延迟是以25ps为单位的时钟延迟模块,使用该模块本身也会带来500ps的延时。

数字延时范围为4~32 VCO时钟周期,每一个延迟单元的大小为0.5 VCO周期。需要注意的是延迟的功能必须在同步使能后才起作用。

-

- SYSREF CLK延迟

SYSREF CLK同样具有模拟核数字延迟。模拟延迟的最小单位为150ps。数字延迟的范围为1.5~11VCO,同样每一个延迟单元的大小为0.5 VCO周期。

-

- 时钟可编程的输出模式

14路时钟的输出不仅在电平标准上可编程,在输出的幅度方面也可编程。

-

- 输出时钟同步

要使时钟的数字延时起作用,管脚SYNC必须给一个脉冲,在脉冲的上升沿所有的时钟同步。

-

- 零延迟模式

没用到,不介绍。

-

- 芯片状态管脚

LMK0482X提供了几个状态管脚用来供用户监测芯片内部的状态或者作为输入端口来响应用户的需求,具体的功能在寄存器配置说明里介绍。

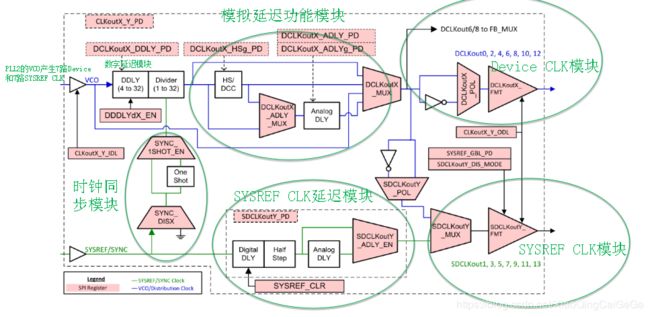

- 功能模块

如下如所示为该系列芯片的功能框图:

如下图所示为Device CLK和SYSREF CLK输出功能框图:

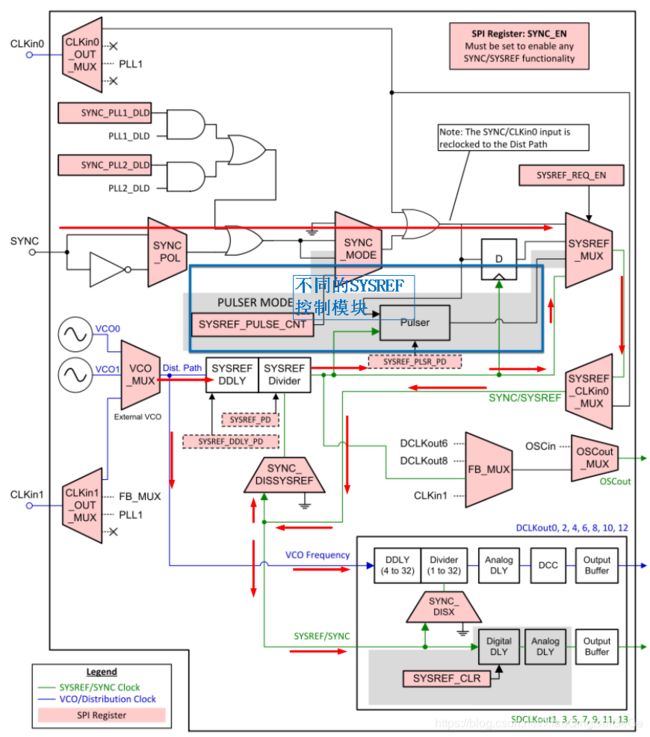

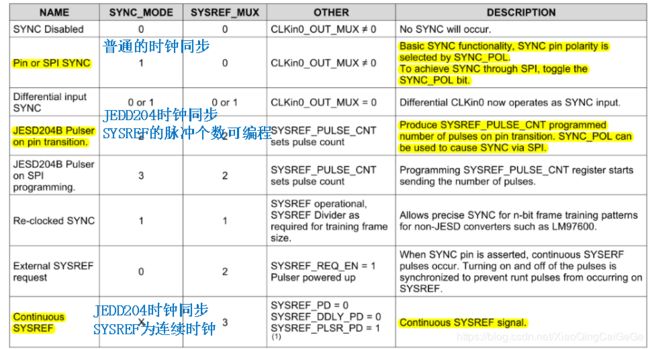

如下图所示为具体的SYSREF/SYNC功能模块:

- 特性描述

- SYNC/SYSREF

SYNC和SYSREF信号共享同一条时钟路径,也就是说同一时间,只能用其中一个的功能,要么使用SYNC实现同步功能,要么是输出SYSREF。

实现各路时钟的同步功能,实际上就是用SYNC信号的上升沿来同步除法器。实现这一目的需要注意以下几点:

- SYNC_EN必须使能

- SYSREF_MUX和SYNC_MODE这两个寄存器参数必须配置正确

- 必须配置寄存器,使延时模块上电

- SYNC_DISX信号必须拉低,使得SYNC/SYSREF能够作用到除法器来完成同步功能,此时SYSREF_MUX寄存器必须切换到SYNC模式

-

- JESD204B

要实现JESD204B的时钟功能,首先必须用SYNC来同步SYSREF输出时钟除法器,然后再配置SYSREF的其它功能。下面为配置SYSREF的例子,其中VCO为3000MHz,DCLKout0和DCLKout2输出1500MHz,用来驱动转换器。DCLKout4驱动FPGA,用两路10MHz的SYSREF同步转换器和FPGA:

在使用SYSREF之前,必须先设置SYSREF_CLR=1持续至少15VCO时钟周期,然后SYSREF_CLR=0.

SYSREF的产生模式有3种,分别为SYSREF Pulser、Continuous SYSREF以及SYSREF Request。

在SYSREF Pulser中,每来一次SYNC,就输出一次SYREF,SYSREF的脉冲个数可编程调节。分别为1、2、4或者8.

在Continuous SYSREF模式中,输出连续的SYSREF时钟,但是不推荐这种方式,因为会和相邻的时钟产生串扰。

在SYSREF Request模式中,芯片允许从外部输入一个SYSREF请求信号来控制连续SYSREF的输出与关断,每当SYSREF_REQ被使能,SYSREF_MUX将调整到Continuous SYSREF模式并输出SYSREF,直到SYSREF_REQ被取消。

-

- Digital Delay

数字延迟有两种方式,分别为静态数字延迟和动态数字延迟。静态数字延时指的是事先配置好延迟参数,然后时钟再在设定的延迟参数下工作,工作后不能变化。动态数字延迟是指时钟在正常工作时,还可以对其进行延迟操作,不影响时钟输出。

设置好静态延迟参数后,外界需要通过SYNC端口给芯片一个使能信号,然后延迟模块才能正常工作。

动态延迟没使用,忽略~

-

- Input Clock Switching

- 手动模式

当CLKin_SEL_MODE为0、1、2时,则分别选择clkin0、clkin1、clkin2为参考时钟输入

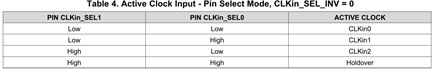

- 管脚选择模式

当CLKin_SEL_MODE为3时,通过状态管脚CLKin_SEL0 和 CLKin_SEL1来选择clkin0、clkin1、clkin2其中的哪路为参考时钟输入:

- 自动模式

当CLKin_SEL_MODE为4时,芯片循环检测clkin0、clkin1、clkin2,识别有时钟输入的那一路作为参考时钟输入。

-

- Digital Lock Detect

PLL1和PLL2都支持数字锁定检测,可通过状态管脚来实时获得PLL1和PLL2是否锁定。

-

- HoldOver

没用过,忽略~

- 芯片功能模式

- Dual PLL

在双PLL模式中,外部参考时钟通过clkin0\ clkin1\ clkin2进入PLL1的输入端,另外的VCXO或可调谐晶振进入PLL2的输入端以及PLL1的反馈端。PLL2的VCO经过分频和延迟后驱动14路时钟输出。如下图所示:

- 0-Delay Dual PLL

零延迟模式分为2种,即级联零延迟模式和嵌套零延迟模式。级联零延迟模式和双PLL模式基本一致,其唯一的区别在于PLL2的反馈不是来自VCO,而是来自于时钟输出。级联零延迟模式如下图所示:

如下图所示为嵌套零延迟模式:其和双PLL模式的区别在于PLL1的反馈输入不是来自于VCXO,而是来自于时钟输出端口,这种方式可以保证所有的输出时钟和Clkinx有确定性的相位关系。

- 芯片编程操作

LMK0482X系列芯片的编程操作采用的是SPI协议,24bit寄存器,寄存器的格式为1bit读写控制命令(R/W)、2bit字节控制命令、13bit地址、8bit数据。寄存器在SCK的上升沿从MSB(读写控制)开始写入,直到数据最低位写完。推荐的寄存器编程顺序为0X000~0X1FFF顺序执行,R/W bit为0时,执行写操作,反之执行读操作。

第二章:LMK04826硬件设计

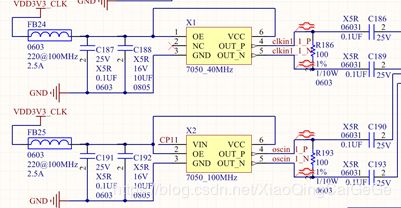

如下图所示为LMK04826的原理图设计:

具体设计包含5大设计模块:

- 电源模块

电源输入参考了开发板的设计:3.3V LDO电源输入耦合磁珠、电容,如下图所示:

- 时钟输入模块

Clkin1外接40MHz的LVDS差分晶振、Clkin0和Clkin2悬空;OSCIN外接100MHz的LVDS差分VCXO,VCXO的VIN端口接PLL1输出的CPOUT1.如下图所示:

- 控制及配置模块

CLKIN_SEL0、CLKIN_SEL1、STATUS_LD1、STATUS_LD2、RESET、SYNC、SCK、SDIO、CS均通过上下拉电阻外接到FPGA。

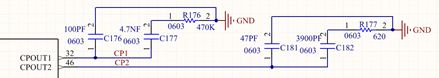

- CPOUT模块

CPOUT1和CPOUT2的滤波参数由TI提供的Clock Design Tool来确定,如果参数值不合适,则会导致PLL1和PLL2不锁定。

- 时钟输出模块

如下图所示为时钟输出模块,所有的输出电平都将被配置成LVDS标准。其中clkout0供给ADC,作为ADC的Device Clk,clkout1也供给ADC,作为ADC的SYSREF;clkout2供给GTX,作为GTX的参考时钟,clkout3供给FPGA,作为FPGA的SYSREF;clkout4供给FPGA,作为FPGA的Device Clk;clkout5、clkout7、clkout10、clkout11、clkout12、clkout13留作测试;clkout6供给另一路GTX,留作备用时钟;clkout8、clkout9作为FPGA系统时钟。

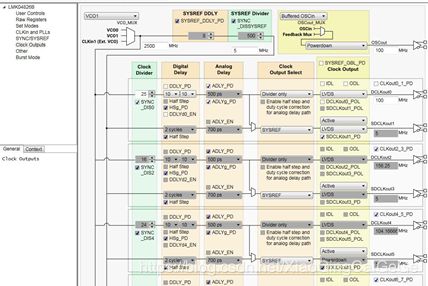

第三章:LMK04826 配置设计

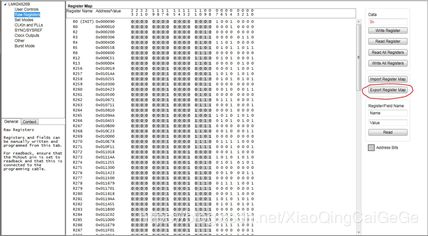

LMK04826的配置寄存器参数太多,手动很难配置,且无法保证准确性。TI公司的官网提供了专门的配置软件“TICS Pro”,免费下载即可。用该软件可以很方便的输出需要配置的寄存器参数值,大大提高工作效率。

以本设计的clkout0输出100MHz的LVDS时钟为例,操作需要以下步骤:

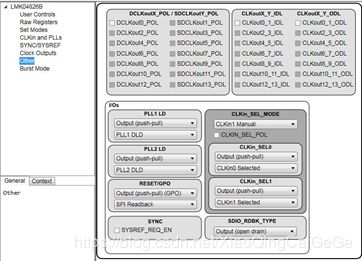

- 设置软件界面的“CLKin and PLLs”,如下图所示:

- 设置软件界面的“SYNC/SYSREF”,如下图所示:

- 设置软件界面的“Clock Outputs”,如下图所示:

- 设置软件界面的“Others”,如下图所示:

- 设置软件界面的“Raw Registers”,点击Export Register Map,即可得到所需的配置参数,如下图所示:

- 如下图所示为得到的寄存器参数:将所有的参数复制到配置程序中运行,再配置LMK04826即可。

第四章:LMK04826实验结果

本次实验测试了普通时钟模式和JESD204B时钟模式:

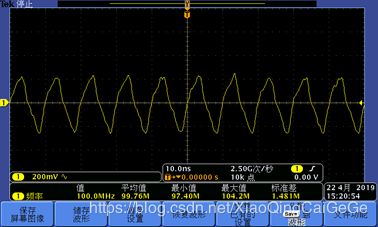

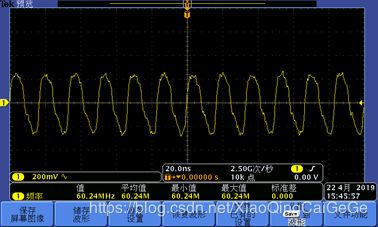

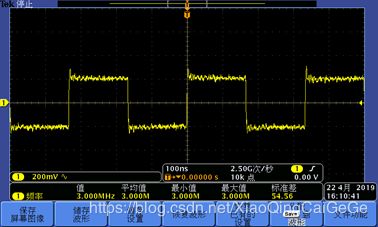

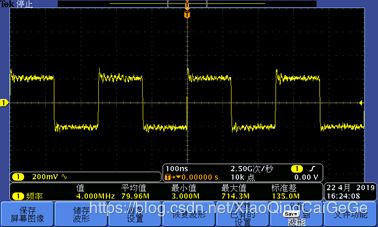

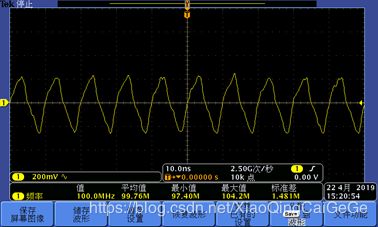

- 普通模式配置了100MHz、80MHz以及60MHz的LVDS时钟。

图:no-jesd204b 100MHz

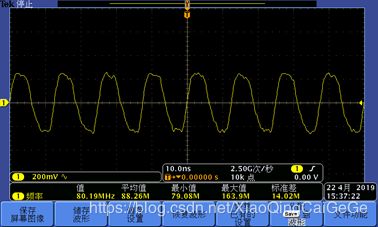

图:no-jesd204b 80MHz

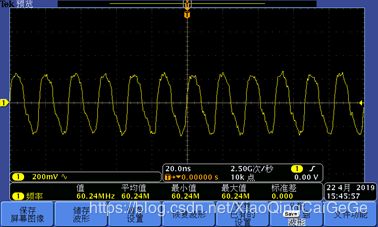

图:no-jesd204b 60MHz

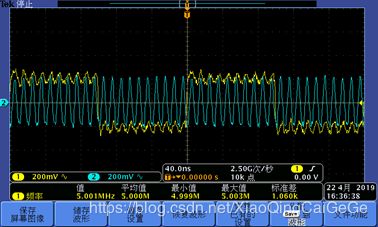

- JESD204B Device Clk-60MHz和Continuous SYSREF-3MHz

图:Continuous jesd204b Device Clk 60MHz

图:Continuous jesd204b SYSREF Clk 3MHz

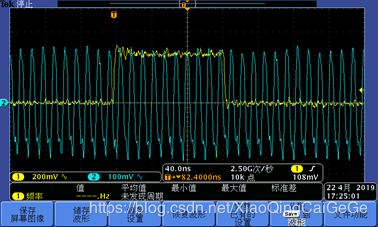

图:Continuous jesd204b Device -SYSREF Clk

- JESD204B Device Clk-80MHz和Continuous SYSREF-4MHz

图:Continuous jesd204b Device Clk 80MHz

图:Continuous jesd204b SYSREF Clk 4MHz

图:Continuous jesd204b Device -SYSREF Clk

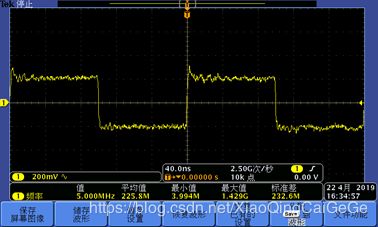

- JESD204B Device Clk-100MHz和Continuous SYSREF-5MHz

图:Continuous jesd204b Device Clk 100MHz

图:Continuous jesd204b SYSREF Clk 5MHz

图:Continuous jesd204b Device -SYSREF Clk

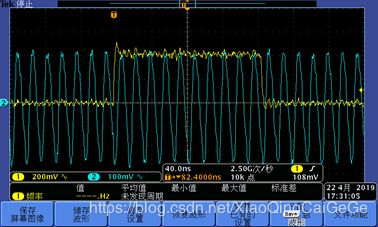

- JESD204B Device Clk-60MHz和Single SYSREF-3MHz

图:Single jesd204b Device Clk 60MHz

图:Single jesd204b Device -SYSREF Clk

- JESD204B Device Clk-80MHz和Single SYSREF-4MHz

图:Single jesd204b Device Clk 80MHz

图:Single jesd204b Device -SYSREF Clk

- JESD204B Device Clk-100MHz和Single SYSREF-5MHz

图:Single jesd204b Device Clk 100MHz

图:Single jesd204b Device -SYSREF Clk