SFF-8436 QSFP + 4X 10 Gb / s可插拔收发器规范 Rev 4.9文档翻译

之前利用闲暇时间依次翻译了SFP MSA、SFF-8024、SFF-8472的相关文档,原由是在交换机端口开发中有参考到相关的信息,虽然用到的字段不多,但是本着学习的心态,对其内容作了大部分的翻译记录。而该三篇文档大部分只涉及了SFP/SFP+相关的技术,适用于10G以及以下速率的光模块收发机。对于10G以上(如40G、100G等)其并无法实现,因此今天对这几天翻译的SFF-8436 Rev4.9(QSFP+ 4x10)【40G】的文档进行整理。之后或许有时间了会翻译SFF-8636 QSFP28【100G】,或将来的CXP、CXP10、CXP28等。凡此种种暂且按下不表,闲言少叙,书接上回SFF-8472-Rev12.3 SFP+文档翻译,咱们言归正传,这回要说的是:Ethernet发展迅猛,速率节节攀升,SFP/SFP+后继无人?SNIA大显神通,标准前赴后继,QSFP+10/28继承大统!

SFF委员会

SFF-8436

QSFP + 4X 10 Gb / s可插拔收发器规范

Rev 4.9 2018年8月31日

摘要:该规范定义了可插拔Quad SFP +模块/直接连接电缆插头和连接器的电气(铜)、光学和机械特性。本规范旨在通过添加对10 Gb/s数据速率的支持和机械规范的更新来取代INF-8438。

目录

7、管理接口

7.1、简介

7.2、时序规范

7.2.1、简介

7.2.2、管理接口时序规范

4.1.1、低速电气硬件引脚

4.1.2、低速电气规范

4.1.3、高速电气规范

7.3、内存交互规范

7.3.1、软控制和状态功能的时序

7.4、设备寻址和操作

7.5、读/写功能

7.5.1、QSFP +存储器地址计数器(读和写操作)

7.5.2、读操作

7.5.3、写操作

7.6 、QSFP +存储器映射

7.6.1、低字节的存储器map

7.6.2、高内存map,Page 00h

7.6.3、存储器高位地址映射页01H

7.6.4、用户可写和供应商特定内存02H

7.6.5、高字节内存页面03H

7、管理接口

7.1、简介

管理接口(已经在GBIC、SFP和XFP等其他形状因子中广泛使用)是为了使用户能够灵活地使用模块而指定的。为了采用多通道模块的使用,对规范进行了更改。一些时序要求对于多通道设备尤其重要,因此提高了接口速度。这个QSFP+规范基于INF-8438规范,但它不向后兼容。地址128 Page00用于指示使用QSFP +存储器映射而不是QSFP存储器映射。

7.2、时序规范

7.2.1、简介

低速信号基于在Vcc下工作的低压CMOS(LVCMOS)。主机应使用连接到2线接口SCL(时钟)和SDA(数据)信号上的Vcc_host的上拉电阻。详细的电气规范在4.1.2中给出。

对于超过1位长的所有寄存器,命名法是MSB-LSB。

7.2.2、管理接口时序规范

为了支持多通道器件,考虑了串行接口的更高时钟速率。

在启动I2C总线通信之前,主机应在I2C总线上的所有模块的ModSelL线上提供设置时间(Host_select_setup)。在2线串行总线通信完成且满足保持时间要求(Host_select_hold)之前,主机不得更改任何模块的ModSelL线。QSFP +模块的I2C接口地址为1010000X(A0h)。为了允许在同一条I2C总线上访问多个QSFP +模块,QSFP +引脚排列包括一个ModSelL或模块选择引脚。该引脚(在模块中被拉高或取消选择)必须由主机保持低电平以选择感兴趣的模块并允许通过I2C接口进行通信。除非进行选择,否则模块不得响应或接受I2C总线指令。(以下部分为第四章内容,主要为引脚定义与功能描述等)

| 表3:引脚功能定义 | |||

| Pin | 符号 | 逻辑I/O | 描述 |

| 1 | GND | Ground[*1] | |

| 2 | Tx2n | CML-I | 发射机反向(Inverted)数据输入 |

| 3 | Tx2p | CML-I | 发射机非反向(Non-Inverted)数据输入 |

| 4 | GND | Ground[*1] | |

| 5 | Tx4n | CML-I | 发射机反向数据输入 |

| 6 | Tx4p | CML-I | 发射机非反向数据输入 |

| 7 | GND | Ground[*1] | |

| 8 | ModSelL | LVTTL-I | 模块选择 |

| 9 | ResetL | LVTTL-I | 模块复位 |

| 10 | VCC Rx | +3.3V接收机供电[*2] | |

| 11 | SCL | LVCMOSI/O | I2C接口时钟 |

| 12 | SDA | LVCMOSI/O | I2C接口数据 |

| 13 | GND | Ground[*1] | |

| 14 | Rx3p | CML-O | 接收机非反向数据输出 |

| 15 | Rx3n | CML-O | 接收机反向数据输出 |

| 16 | GND | Ground[*1] | |

| 17 | Rx1p | CML-O | 接收机非反向数据输出 |

| 18 | Rx1n | CML-O | 接收机反向数据输出 |

| 19 | GND | Ground[*1] | |

| 20 | GND | Ground[*1] | |

| 21 | Rx2n | CML-O | 接收机反向数据输出 |

| 22 | Rx2p | CML-O | 接收机非反向数据输出 |

| 23 | GND | Ground[*1] | |

| 24 | Rx4n | CML-O | 接收机反向数据输出 |

| 25 | Rx4p | CML-O | 接收机非反向数据输出 |

| 26 | GND | Ground[*1] | |

| 27 | ModPrsL | LVTTL-O | 当前模块 |

| 28 | IntL | LVTTL-O | 中断 |

| 29 | VCC Tx | +3.3V发射机供电[*2] | |

| 30 | VCC1 | +3.3V供电[*2] | |

| 31 | LPMode | LVTTL-I | 低功耗模式 |

| 32 | GND | Ground[*1] | |

| 33 | Tx3p | CML-I | 接收机非反向数据输入 |

| 34 | Tx3n | CML-I | 接收机反向数据输入 |

| 35 | GND | Ground[*1] | |

| 36 | Tx1p | CML-I | 接收机非反向数据输入 |

| 37 | Tx1n | CML-I | 接收机反向数据输入 |

| 38 | GND | Ground[*1] | |

| [*1]:所有模块电压都参考该电位。 将它们直接连接到主板信号公共接地。 | |||

| [*2]:Vcc Rx,Vcc1和Vcc Tx应同时应用(在QSFP+模块内部可以以任意组合方式连接)。推荐的主板电源滤波如图3和图4,每个连接器引脚的额定最大电流为500 mA。 | |||

注:关于Rxp、Rxn、Txp、Txn;

p(positive)表示差分电路的正极;n(negative)表示差分电路的负极;反向/非反向指差分信号+/-。

图3显示了一个完整的QSFP+主机PCB原理图的示例,它连接到SerDes和control ICs。

4.1.1、低速电气硬件引脚

除2线串行接口外,该模块还具有以下用于控制和状态的低速引脚:ModSelL、ResetL、LPMode、ModPrsL、INTL

4.1.1.1、 ModSelL

ModSelL是输入引脚。当主机保持低电平时,模块响应I2C命令。ModSelL允许在单个I2C接口总线上使用多个QSFP+模块。当ModSelL为“High”时,模块不应响应或确认来自主机的任何I2C接口信号。ModSelL信号输入节点必须偏置到模块中的“High”状态。

为了避免冲突,在取消选择任何QSFP+模块后,主机系统不应在ModSelL Deassert的时间内尝试I2C接口通信。类似地,在与新选择的模块通信之前,主机必须至少等待ModSelL assert时间段。只要满足上述时序要求,不同模块的assert(断言)和assert(解除断言)周期可能重叠。

4.1.1.2 、ResetL

必须将ResetL引脚拉至QSFP+模块中的Vcc。 ResetL引脚上的低电平时间超过最小脉冲长度(t_Reset_init)会启动完整的模块复位,将所有用户模块设置恢复为默认状态。模块复位assert时间(t_init)在ResetL引脚上的低电平释放后的上升沿开始。 在执行复位(t_init)期间,主机应忽略所有状态位,直到模块指示复位中断完成:模块通过在Data_Not_Ready位被否定的前提下,断言“低”IntL信号来指示这一点。请注意,在上电(包括热插入)时,模块应发出复位完成的中断,而无需复位。

4.1.1.3 、LPMode

LPMode引脚应在QSFP +模块中上拉至Vcc。该功能受LPMode引脚以及Power_override和Power_set软件控制位(A0h,Byte93,Bit0-1)的组合影响。

该模块有两种模式:低功耗模式和高功耗模式。高功耗模式在四种功率等级之一中运行。

当模块处于低功耗模式时,其最大功耗为1.5W。如果意外插入这些模块,这可以保护无法冷却更高功率模块的主机。在这种低功耗模式下,模块I2C接口和所有激光安全功能必须完全可操作。在低功耗模式下,模块仍支持完成复位中断。

如果扩展标识符位(Page 00h,Byte129,Bit6-7)指示功耗大于1.5W且模块处于低功耗模式,则必须将功耗降至1.5W以下,同时仍保持上述功能。没有规定实现低功率的确切方法,但是在这种状态下,Tx或Rx或两者都可能无法工作。如果扩展标识符位指示其功耗小于1.5W,则模块应完全正常工作,无论其处于低功耗还是高功率模式。

如果LPMode引脚处于高电平状态,或者Power_override和Power_set都处于高电平,则模块应处于低功耗模式。如果LPMode引脚处于低电平状态,或者Power_override位为高电平且Power_set位为低电平,则模块应处于高功耗模式。请注意,Power_override位默认状态为低。真值表如下所示:

在Power up时,Power_override和Power_set位应该设置默认为0。

4.1.1.4 、ModPrsL

ModPrsL被拉到主机板上的Vcc_Host,并在模块中接地。ModPrsL在插入时断言为“低”,当模块物理上不在主机连接器上时(不在位),Modprsl将被取消断言为“高”。

4.1.1.5、 IntL

IntL是输出引脚。“低”时,表示可能的模块操作故障或对主机系统至关重要的状态。主机使用I2C接口识别中断源。IntL引脚是开路集电极输出,必须拉至主机板上的主电源电压。完成复位后,当读取Byte 2,Bit0(数据未就绪)值为“0”且读取标志字段(见7.6.1.2)时,INTL引脚置为“高电平”。

4.1.2、低速电气规范

除SCL和SDA之外的低速信号,都是基于在Vcc下工作的低电压TTL(LVTTL)。Vcc是指VccTx,VccRx,Vcc_host或Vcc1的通用电源电压。主机应在每个I2C接口SCL(时钟),SDA(数据)和所有低速状态输出上使用连接到Vcc_host的上拉电阻。SCL和SDA是一个热插拔接口,可以支持总线拓扑。在模块插入或移除期间,模块可以实现预充电电路,以防止损坏来自已使用总线的其他模块的数据传输。

4.1.3、高速电气规范

4.1.3.1 、Rx(n)(p / n)

Rx(n)(p / n)是QSFP +模块接收器数据输出。Rx(n)(p / n)是交流耦合的100欧姆差分线路,应在主机ASIC(SerDes)上以100欧姆差分端接。交流耦合在QSFP +模块内部,主板上不需要。正确端接后,差分电压摆幅应满足≤1600 mVpp或相关标准,以较小者为准。注:由于专为QSFP+设计的主板可能会插入QSFP模块,建议主板输入的损坏阈值至少为1600mv峰间差分值。

光输入信号丢失的输出抑制,称为Rx抑制,如下所示。如果任何信道上的光信号变得等于或小于断言LOS所需的电平,则该信道的接收器数据输出应被抑制或禁用。在抑制或禁用状态下,输出阻抗水平保持不变,而差分电压摆幅应小于50mVpp。

在正常操作中,默认情况下Rx抑制激活。可以通过I2C接口使用Rx Squelch Disable禁用Rx抑制。Rx Squelch Disable是一个可选功能。具体细节请参见7.6.5.2。

4.1.3.2、 Tx(n)(p / n)

Tx(n)(p / n)是QSFP +模块发送器数据输入。它们是交流耦合的100欧姆差分线路,QSFP +模块内部具有100欧姆差分端接。交流耦合在QSFP +模块内部,主板上不需要。对于6 Gb / s及以下的输入,输入可接受250 mV至800 mV之间的单端电压摆幅,以及500 mVpp至1600 mVpp之间的差分电压摆幅。为获得最佳EMI结果,建议单端摆动控制在250 mV和600 mV之间,并且差分摆动控制在500 mVpp至1200 mVpp之间。对于高于6 Gb / s的操作,请参阅相应的规范,例如:802.3ba附件86A,FC-PI-4,FC-PI-5或InfiniBand规范。10G以太网参考SFF-8431。由于有可能将QSFP +模块插入到按照INF-8438i设计用于QSFP接口的主机中,模块输入的损坏阈值应至少为1600 mV峰间差分值。

输出抑制(以下简称Tx抑制),输入信号丢失(以下简称Tx LOS)为可选功能。实现时,其功能如下。在差分情况下,任何通道上的峰间电信号小于50mvpp,则该通道的发射机光输出将被抑制或禁用,并设置相关的TxLOS标志。在抑制时,发射机OMA应小于或等于-26 dBm,禁用时发射机功率应小于或等于-30 dBm。对于如以太网的应用,其发射机关闭条件是根据平均功率定义的,建议禁用发射机;并且对于如InfiniBand的应用,其发射器关闭条件是根据OMA定义的,建议对发射器进行抑制。

在模块操作中,在实现Tx抑制的情况下,默认情况下Tx抑制是激活的。可以通过I2C接口使用Tx Squelch Disable禁用Tx抑制。Tx Squelch Disable是一个可选功能。有关具体细节,请参阅条款7.6.5.2。

7.3、内存交互规范

7.3.1、软控制和状态功能的时序

表15中描述了QSFP +软控制和状态功能的时序。

表16中定义了Squelch和disable的时序。

7.4、设备寻址和操作

串行时钟(SCL):主机向QSFP +模块提供SCL时钟输入,用于将上升沿开始的时钟数据输入到每个QSFP+设备(上升沿触发,在SCL高电平期间采样SDA管脚电平,输入QSFP+),将下降沿时钟数据从每个设备输出(下降沿触发,在低电平期间输出数据改变SDA管脚电平)。在时钟延长期间,SCL线可能被QSFP+模块拉低。

串行数据(SDA):SDA引脚是双向的,用于串行数据传输。该引脚为漏极开路或集电极开路驱动,可与任意数量的漏极开路或集电极开路器件进行线或(wire-ORed)连接。主/从:QSFP +模块仅作为从设备运行。主机必须为SCL提供总线并且主机启动所有读/写通信。

设备地址:每个QSFP+在设备地址A0h处都是硬连线。有关每个模块内存结构的信息,请参见第7.6节。每个SCL / SDA有多个器件:虽然QSFP+模块与点对点SCL / SDA兼容,但它们可以使用QSFP+ ModSelL线共享单个SCL/ SDA总线。有关详细信息,请参见子条款4.1.1.1,子条款4.1.2和表3。

时钟和数据转换:SDA引脚通常通过外部器件拉高。

SDA引脚上的数据可能仅在SCL低电平时间段内发生变化(即上面所述,上升沿触发高电平READ_ONLY,下降沿触发低电平WRITE_ONLY)。 SCL高电平期间的数据更改表示START或STOP条件。所有地址和数据字以8位字串行发送到QSFP+或从QSFP+发送出去。

SDA线上的每个字节必须为8位长。首先使用最高有效位(MSB)传输数据。

START条件:SCL和SDA均为高电平时,SDA从高到低的跳变则是START条件,必须先于任何其他命令。STOP条件:SCL为高电平时,SDA从低到高的跳变(强制拉高)是STOP条件。ACK:发送每个8位字后,发送器释放SDA线一个Bit时间,在此期间允许接收器将SDA拉低以确认(ACK)它已接收到每个字。接收器拉低表示ACK,拉高表示NACK。

由主机发起的设备地址/写数据字节应由QSFP +模块确认。QSFP+模块发送的读取的数据字节应由主机确认除最后一个字节读取之外的所有字节,主机应以STOP响应而非ACK。

内存(管理接口)复位:协议中断、断电或系统复位后,QSFP+管理接口可以复位。存储器复位仅用于复位QSFP +模块管理接口(以校正挂起的总线)。不包含其他模块功能。

1)时钟最多9个周期。

2)在SCL为高电平时,在每个周期中匹配SDA高电平。

3)当SDA为高时创建START条件

器件寻址:QSFP+器件在启动条件之后需要一个8位器件地址字,以启用读或写操作。器件地址字由图23中前七个最高有效位的强制序列组成。这对所有QSFP +器件都是通用的。

器件地址的第8位是读/写操作选择位。如果该位设置为高,则启动读操作,如果该位设置为低,则启动写操作。在比较器件地址(ModSelL处于低电平状态)时,QSFP +模块应在SDA线上输出零(ACK)以确认地址。

7.5、读/写功能

7.5.1、QSFP +存储器地址计数器(读和写操作)

QSFP +器件维护一个内部数据字地址计数器,该计数器包含在最新读写操作期间访问的最后一个地址,以1为增量。每当模块接收或发送数据字时,地址计数器就递增。只要保持QSFP+电源,该地址在操作之间保持有效。读取和写入操作期间的地址“翻转”是指从128字节存储器页面的最后一个字节到同一页面的第一个字节。

7.5.2、读操作

7.5.2.1、当前地址读取

当前地址读操作,仅需要发送设备地址(10100001)读取字,参见图24。

一旦被QSFP+确认,当前地址的数据字将被串行时钟输出。主机不会响应确认,但在读取数据字后会生成停止条件。

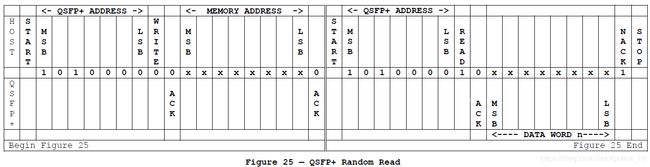

7.5.2.2、随机读取

随机读操作需要一个“虚拟(假)”的写操作来加载目标字节地址,如图25所示。这是通过以下顺序完成的。

目标8位数据字内存地址,在器件地址写入字(10100000,A0H)之后发送,并分别由QSFP +依次确认。然后,主机生成另一个START条件(在不递增计数器的情况下中止虚拟写入)和通过发送设备读取地址(10100001)读取的当前地址。QSFP +确认器件地址并串行输出所请求的数据字。主机不响应确认,但一旦读取数据字就会产生停止条件。

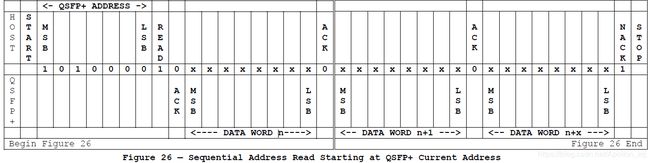

7.5.2.3、顺序读取

顺序读取由图26的当前地址读取或图27的随机地址读取启动。要指定顺序读取,主机在每个数据字后响应一个确认(而不是STOP)。只要QSFP +收到确认,它就会连续输出顺序数据字。当主机以NACK和STOP响应而不是ACK响应时,则QSFP+终止发送序列。

7.5.2.4、从随机起始地址开始的顺序读取

7.5.3、写操作

7.5.3.1、字节写

写操作在设备地址写字(10100000,A0H)和QSFP+确认之后,需要跟随一个8位数据字的内存地址,见图28。

收到该内存地址后,QSFP +将再次响应ACK,然后输入第一个8位数据字。收到8位数据字后,QSFP +应输出0(ACK),主机必须以STOP条件终止写序列,以便结束本次并开始下一次写入操作。如果发送START而非STOP(即2线接口规范重复START),则中止写入并丢弃在该操作期间接收的数据。收到正确的STOP条件后,QSFP+将内部定时写周期tWR输入内部存储器。QSFP+在此写周期内禁用其管理接口输入,并且在写完成之前不应响应或确认后续命令。注意,QSFP+写命令不支持使用重复START条件的2线接口“组合格式”。

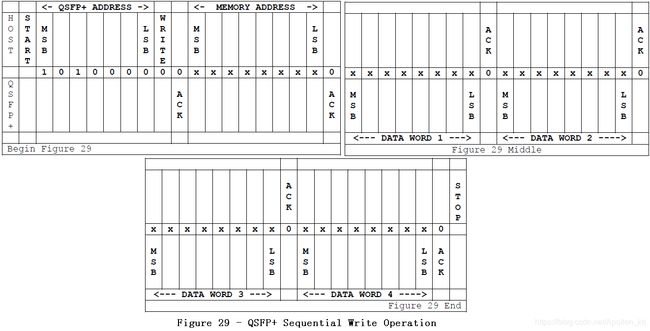

7.5.3.2、顺序写入

QSFP +应支持最多4个连续字节写的操作,而无需重复发送QSFP +地址和存储器地址信息,如图29所示。

“顺序”写入的启动方式与单字节写入相同,但主机主机在第一个字输入后不发送停止条件。相反,在QSFP +确认收到第一个数据字后,主机可以最多传输三个数据字。QSFP +应在收到每个数据字后发送确认。主机必须以STOP条件终止顺序写序列,否则写操作将被中止并丢弃数据。

7.5.3.3、确认轮询

一旦QSFP +内部定时写周期开始(并且总线上的输入被忽略),应答轮询可用于确定写操作何时完成。 这涉及发送START条件,然后发送器件地址字。 仅当内部写周期完成时,QSFP +才会响应后续命令,表示读或写操作可以继续。

7.6 、QSFP +存储器映射

本子条款定义了用于串行标识、数字监控和某些控制功能的QSFP+模块的内存映射。所有QSFP +设备都必须使用该接口。该接口主要是在INF-8077i Rev.4.0中定义的XFP MSA之后设计的。存储器映射已更改,以容纳4个光通道并限制所需的存储空间。使用单地址方法,如XFP中所示。使用分页的方式来启用主机和模块之间的实时性数据交互。

存储器的结构如图30所示。内存的结构如图30所示。内存空间被安排成一个较低的单页的、128字节的地址空间和多个较高的地址空间页。这种结构允许及时访问低页中的地址,例如中断标志和监视器。实时性要求不严格的条目,如序列ID信息和阈值设置可通过页面选择功能来实现。该结构还通过根据需要添加额外的“高”页面来提供地址扩展。例如,在图30中,页01和02是可选的。页01允许实现Application Select Table,页02提供用户读/写空间。始终实现“低”页面和“高”页面00。如果“低”页中的Byte 2,Bit 2为低,则需要页面03。有关可选页01和02的声明的详细信息,请参见表39。

使用的接口地址是A0xh,主要用于中断处理等实时性要求较高的关键数据,以便为与中断情况相关的所有数据启用“一次性读取”。在断言IntL之后,主机可以读出标志字段以确定受影响的通道和标志类型。

为了允许在同一个I2C接口上访问多个QSFP +模块,QSFP +引脚排列包括一个ModSelL引脚,允许主机选择相应的模块进行交互。有关I2C接口的详细信息,请参见第4.1.1.1节和4.1.2,了解有关ModSelL的详细信息。

注:保留的内存位置在保留字节的所有位位置中都用逻辑零填充,保留内存字节的部分为,则仅填充该位为0,如本节所述。未使用的可选位(O)将填充逻辑零。不适用的位(NA)应填充逻辑零。对于适当的电缆类型,每个表中都显示了可选(O,Optional),必需(R,Required)和不适用(NA,Not Applicable)寄存器的标识。

7.6.1、低字节的存储器map

2线串行总线地址空间的低128字节(见表17)用于访问各种测量和诊断功能,一组控制功能,以及后用于后续的选择各种高字节存储器映射页中的哪一个的功能。地址空间的这一部分总是可直接寻址,因此被选择用于可能需要重复访问的监视和控制功能。Identifier字段的定义与页面00h地址Byte 128相同。

7.6.1.1、状态指示位

模块上电期间和监视器读数无效之前,Data_Not_Ready位为1。一旦所有监视器读数都有效,该位将设为0,直到器件断电。如果存储器内容是静态的,则该位可以始终为低。

7.6.1.2、中断标志

内存map的一部分(Byte 3-21)形成一个标志字段。在此字段中,将报告LOS和Tx Fault的状态以及各种受监控项目的警报和警告。对于正常操作和默认状态,此字段中的位的值为0b。对于LOS,Tx Fault,模块和通道报警和警告的定义条件,设置适当的位或值,value = 1b。 置位后,这些位保持置1(锁存)状态,直到被包括受影响位的读操作清除或被ResetL引脚复位。

在底层故障持续时清除的故障位可以立即由模块重新设置。这可能会导致IntL取消断言,然后快速地重新断言,也可能不会。主机应该容忍这两种行为。通道状态中断标志定义在表19中。这些标志可能被屏蔽(见7.6.1.6)。

模块监视器中断标志在表20中定义。

通道监视器中断标志在表21中定义。

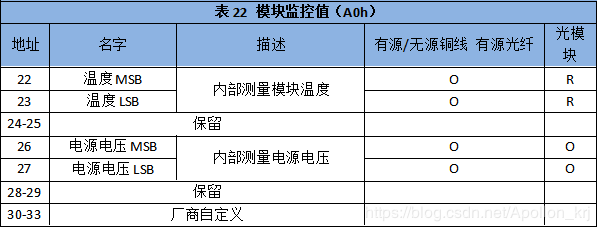

7.6.1.3、模块监控

QSFP +模块的实时监控包括模块温度,模块电源电压以及每个发送和接收通道的监控。通道监控功能在第7.6.1.4节中描述。

测量的参数在16位数据字段中报告,即两个连接的字节。16位数据字段允许较大(宽)的动态范围。这并不意味着为了达到下面所述的精度目标,建议或要求使用16位A /D系统。数据字段的宽度不应视为暗示给定的精度水平。可以想到,这里的精度目标可以通过具有小于16位分辨率的系统来实现。建议将超出系统指定精度的任何低阶数据位固定为零。整体系统的准确度和精确度将取决于供应商。

收发器需要确保用诊断监测数据更新的任何多字节字段必须以保证一致性的方式完成此更新和最终数据的一致性。换句话说,收发器不必更新多字节字段,以便可以将部分更新的多字节字段传送到主机。此外,在将该多字节字段传送到主机期间,收发器不应更新结构内的多字节字段,使得部分更新的数据将被传送到主机。

下列精度要求适用于有关标准规定的工作信号范围。在满足精度要求的条件下,应参考制造商的规范以获得更详细的信息。

测量值在供应商指定的工作温度和电压下校准,并应按下面的定义解释。警报和警告阈值应以与实时16位数据相同的方式解释。

内部测量的模块温度表示为16位有符号二进制补码值,增量为1/256摄氏度,产生-128C至+ 128C的总范围,在-40和+ 125C之间被认为是有效的。内部测量的模块电源电压表示为16位无符号整数,电压定义为所有16bit值(0 - 65535),LSB等于100 uV,产生的总测量范围为0至+6.55 V。

7.6.1.4、通道监控

实时通道监控是针对每个发射和接收通道,包括光输入功率和Tx偏置电流。模块监控功能见第7.6.1.3款。测量值在供应商指定的工作温度和电压范围内进行校准,并应按如下定义进行解释。报警和警告阈值的解释应与实时16位数据相同。表23定义了通道监视。

测量的TX偏置电流为mA,用16位无符号整数表示(0 - 65535),LSB = 2uA,总测量范围为0 ~ 131mA。

值可以表示平均接收功率或OMA,具体取决于Page 0,Byte 220(A0h)的第3位的设置方式。表示为16位无符号整数,其功率定义为完整的16位值(0-65535),LSB等于0.1 uW,产生的总范围为0到6.5535 mW(〜-40到+8.2 dBm)。

绝对精度取决于确切的光学波长。对于供应商指定的波长,在指定的温度和电压下,精度应优于±3dB。根据适当的标准,在输入功率不超过最大传输功率或最大接收功率中较小的那一个的情况下,应保持这种准确度。应根据适当的标准将其维持在传输功率减去电缆设备损耗(插入损耗或无源损耗)的最小值。超出此最小要求的接收输入光功率绝对精度范围是供应商特定的。

7.6.1.5、控制字节

控制字节在表24中定义。这些字节旨在由主机写入。

*1、 写入“1”将禁用通道的激光器。如果软件速率选择没有实现,模块将忽略速率选择位。寄存器在通电时读取所有bit均为“0”。

7.6.1.6、模块和通道掩码(屏蔽)

主机系统可以通过设置来自用于模块标志的字节100-104中的一组Mask(屏蔽/掩码位)的,以及用于信道标志的page 03h的Byte 242-253来控制哪些标志导致中断(IntL)。表25和表48中对这些进行了描述。掩码位中的1值可防止硬件IntL引脚被相应的锁存标志位置位。掩码位是易失的,并且在所有未屏蔽的情况下启动(掩码位0)。

掩码位可用于防止持续中断的情况,否则将不断由硬件IntL引脚产生中断。无论何时实现关联的标志位,都需要一个掩码位(用C表示Conditional,有条件的)。

7.6.1.7、速率选择(Byte 87-88)

Rate Select是一个可选控件,用于限制接收器带宽以兼容多种数据速率(很可能是光纤通道)。 此外,速率选择允许发射机针对特定数据速率传输进行微调。该模块可能:

a)不支持速率选择;

b)使用扩展速率选择进行速率选择;

c)使用应用程序选择表进行速率选择。

7.6.1.7.1、不支持速率选择

当不支持速率选择时,Page 00h,Byte 221,Bit[3:2]=0b’00,Option(Page 00h,Byte 195,Bit5)的值为0。缺少实现并不表示缺少同时符合多种速率标准。应根据模块值确定是否符合特定标准(参见表33)。

7.6.1.7.2、扩展速率选择

当Page 00h,Byte 221,Bit[3:2]=0b’01,且扩展速率一致性字节(Page 00h,Byte 141)中的至少一个位的值为1时,模块支持扩展速率选择。扩展速率选择在Rxn_Rate_Select(Byte 87)中为每个通道保留两个比特,在Txn_Rate_Select(Byte 88)中为每个通道保留两个比特,以表示最多四种速率。表26定义了Byte 141的Bit 0=1时的功能。扩展速率符合字节的所有其他值都是保留的。

7.6.1.7.3、使用应用程序选择表选择速率

对于兼容SFF-8472的模块,应用程序选择(Byte 89)最大化了与SFF-8079 Part 2的兼容性。当速率选择声明位Page 00h,Byte 221 Bit[3:2]=01,使用第01h页中定义的应用程序选择方法(参见第7.6.3节)。

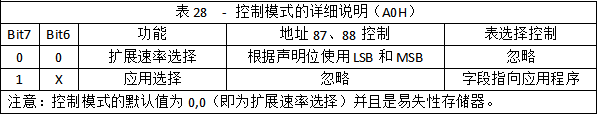

主机读取第01h页上的整个应用程序选择表以确定模块的功能。主机通过将控制模式和表选择(Table Select,TS)字节写入Byte 89-92和Byte 94-97来分别控制每个通道。表27中定义了Rx_Application Select和Tx_Application Select每个字节的位功能。

控制模式定义了应用程序的控制模式。表格选择从63种可能性(000000到111110)中选择AST中的模块行为。注意,111111无效。

7.6.1.8、密码输入和更改

字节119-126保留用于可选的密码输入功能。密码输入字节是只写的,并且将被保留,直到由主机断电,复位或重写。此功能可用于控制对供应商特定页面02h的读/写访问。此外,模块供应商可以使用此功能实现串行ID的写保护和其他QSFP+只读信息。密码可以提供给主机制造商使用,以限制用户EEPROM页面中的写访问。

访问下内存页00h或上内存页00h、02h和03h中的QSFP+定义数据不需要密码访问。请注意,可以定义多个模块制造商密码,以允许有选择地访问上面所允许的内存的各个部分。

主机制造商密码和模块制造商密码应通过高位(Byte 123,Bit 7)进行区分。所有主机制造商密码应在00000000h至7FFFFFFFh范围内,所有模块制造商密码在80000000h至FFFFFFFFh范围内。在新模块中,主机厂商密码初始设置应为00001011h。

当在123-126中输入正确的当前主机制造密码时,可以通过在字节119-122写入新密码来更改主机制造商密码,其中高位被忽略并在新密码中强制为0。上电和复位时,密码输入字段应设置为00000000h。

7.6.2、高内存map,Page 00h

第00h页由序列号组成,用于只读标识信息。串行ID分为Base_ID字段、扩展ID字段和特定于供应商的ID字段。串行ID内存map的格式如表29所示。[译注:对于SFF-8472 SFP+,读取0~127字节,共128字节;对于SFF-8436 QSFP 10/SFF-8636 QSFP 28,读取Page0的0~127 Byte即A0H偏移的128~255Byte,那么对于I2C读取出来的128Byte组成的数组sfp[128],其对于电缆长度字段都是在sfp[18];前者是A0H+18D,后者是A0H+128D+18D=A0H+146D]。

注*1:值为零表示模块不支持指定的技术,或者必须根据模块技术确定长度信息。

注2:对有/无源铜、有源光纤、光模块,BASE_ID所表示内容信息均为R(Required,必需)。

7.6.2.1、标识符(Byte 128)

标识符值指定由串行信息描述的物理设备。该值应包括在串行数据中。定义的标识符值如表30所示(略,这些值在SFF-8024的收发器管理部分中维护,适用于QSFP+的从0x00~0x0D,具体参见SFF-8024 Table4-1)。QSFP +模块应使用标识符0Dh。

7.6.2.2、扩展标识符(Byte 129)

扩展标识符提供有关基本模块类型的其他信息,例如模块是否包含CDR功能并标识其所属的功耗级别。

比如:Byte129,Bits[7:6]=0b’00即1类电源模块(最大功耗1.5W)。

7.6.2.3、连接器(Byte 130)

Connector值表示接口上提供的外部连接器。 该值应包含在串行数据中。 定义的连接器值如表32所示(注:这些值在SFF-8024的连接器类型维护)。请注意,01h - 0Bh不兼容QSFP+(即在QSFP+中不存在这些比较陈旧的连接器类型,SFF-8436包含从00h-23h,具体参见SFF-8024 Table4-3连接器类型参考),为了与其他标准(如SFP MSA、SFF-8024等)兼容而包含在内。

7.6.2.4、规范合规性(Byte 131-138)

以下位有效指示器定义了QSFP +模块支持的电子或光学接口。对于光纤通道QSFP +,应指示光纤通道速度,传输介质,发射器技术和距离能力。

7.6.2.5、编码(Byte 139)

编码值表示串行编码机制,它是特定QSFP +模块的标称设计目标。该值应包含在串行数据中。定义的编码值如表34所示(略,具体参见SFF-8024 Table4-2编码值参考)。

7.6.2.6、标称BR(Byte 140)

标称比特率(BR,标称值)以100Mbps为单位指定,四舍五入到最接近的100Mbps。比特率包括编码和分隔信号所需的那些比特,以及携带数据信息的那些比特。值为0表示未指定比特率,必须根据模块技术确定。实际信息传输速率将取决于编码值定义的数据编码。

7.6.2.7、扩展的速率选择合规性(Byte 141)

Extended Rate Select Compliance字段用于允许单个QSFP +模块灵活地符合单个或多个扩展的速率选择定义。通过在指定的位标记位置存在“1”来指示定义。如果使用独占的非重叠位标记定义,则page 00h,Byte 141将允许符合8(1-8)个不同的多速率定义。

| 表35 - 扩展的速率选择合规性标签分配(Byte 141)(Page 00h) | ||

| 地址 | Bit | 描述 |

| 141 | 7月1日 | 保留 |

| 0 | QSFP +速率选择版本1,此功能与SFF-8472和SFF-8431不同。 | |

注:有关使用该字段的更多详细信息,请参见第7.6.1.7节。

7.6.2.8、长度(标准SM光纤)-km(Byte 142)

从原始GBIC定义中添加EEPROM数据。此值指定QSFP+模块使用单模光纤按照在符合适用标准的情况下支持的链路长度。支持的链路长度在SFF 8074i标准中指定。这个值的单位是km。值为零意味着模块不支持单模光纤,或者长度信息必须由模块技术确定。

7.6.2.9、长度(OM3)( Byte 143)

此值指定QSFP+模块在使用2000 MHZ*km (850 nm)扩展带宽50um核心多模光纤按适用标准操作时支持的链路长度。这个值的单位是2m。0表示模块不支持OM3光纤,或者长度信息必须由模块技术确定。

7.6.2.10、长度(OM2)( Byte 144)

此值指定QSFP +模块在使用500 MHz * Km(850 nm和1310 nm)50um多模光纤按适用标准操作时支持的链路长度。这个值的单位是1m。0表示模块不支持OM2光纤,或者长度信息必须由模块技术确定。

7.6.2.11、长度(OM1)(Byte 145)

此值指定QSFP +模块在使用200 MHz * Km(850 nm)和500 MHz * Km(1310 nm)62.5um多模光纤按适用标准操作时支持的链路长度。 该值以1米为单位。 值为零表示模块不支持OM1光纤,或者必须根据模块技术确定长度信息。

7.6.2.12、电缆组件长度(铜缆或有源电缆)(Byte146)

此值指定有源电缆组件的链路长度。该值以1m为单位。 链路长度在INF 8074中规定。小于1米的链路长度应表示为1米。值为零表示模块不是电缆组件,或者必须根据模块技术确定长度信息。值255表示模块支持的链接长度大于254米。注:对于所有直接连接电缆组件,包括有源光缆,Byte142-145值应为零。

7.6.2.13、设备技术(Byte 147)

表36和表37中描述了器件中使用的技术。Device Tech字节的前4位描述了所使用的器件技术。Device Tech字节的低4位(位7-4)用于描述发送器技术。

| 表36 - 器件技术描述(Byte147)(Page 00H) | |

| Bits | 物理器件描述 |

| 7月4日 | 发送器技术 |

| 3 | 0:无波长控制;1:主动波长控制 |

| 2 | 0:非制冷发射器设备;1:制冷发射器 |

| 1 | 0:管脚检测器;1:APD探测器 |

| 0 | 0:发射器不可调;1:发射器可调 |

| 表37 -发射机技术(Byte147,Bits[7:4])(Page 00H) | |

| 值 | 发射机描述 |

| 0 | 850nm VCSEL(vertical-cavity surface-emitter laser,垂直腔面发射激光器) |

| 1 | 1310nm VCSEL |

| 10 | 1550nm VCSEL |

| 11 | 1310nm FP(Fabry-perot,法布里-珀罗激光器,低速短距离) |

| 100 | 1310nm DFB(Distributed Feedback,分布式反馈半导体激光器,高速中长距) |

| 101 | 1550nm DFB |

| 110 | 1310nm EML(Electro-absorption Modulated Laser,电吸收调制激光器) |

| 111 | 1550nm EML |

| 1000 | 其他 |

| 1001 | 1490nm DFB |

| 1010 | 铜电缆,非均衡器 |

| 1011 | 铜电缆,无源均衡器 |

| 1100 | 铜电缆,近/远端限制有源均衡器 |

| 1101 | 铜电缆,远端限制有源均衡器 |

| 1110 | 铜电缆,近端限制有源均衡器 |

| 1111 | 铜电缆,线性有源均衡器 |

7.6.2.14、供应商名称(Bytes148-163) ;

7.6.2.16、 厂商 OUI (Bytes 165-167;

7.6.2.17、厂商PN (Bytes 168-183);

7.6.2.18、厂商Rev (Bytes 184-185)

有关格式参见:SFF-8472-Rev12.3 SFP+文档翻译

7.6.2.15、扩展模块代码(Byte164)

扩展模块代码定义了由QSFP+模块支持的InfiniBand的电子或光学接口,如表38所示。

| 表38 -扩展模块代码值(Byte 164)(Page 00) | |||||

| Addr | Bit | Description of Module Data | 单通道 | 4通道 | 12通道 |

| 164 | 7~6 | Reserved | |||

| 5 | HDR(High Data Rate) | 50Gbps | 200Gbps | 600Gbps | |

| 4 | EDR(Enhanced Data Rate) | 26 Gbps | 104Gbps | 312 Gbps | |

| 3 | FDR(Fourteen Data Rate) | 14 Gbps | 56Gbps | 168 Gbps | |

| 2 | QDR(Quard Data Rate) | 10 Gbps | 40 Gbps | 120 Gbps | |

| 1 | DDR(Double Data Rate) | 5 Gbps | 20 Gbps | 60 Gbps | |

| 0 | SDR(Single Data Rate) | 2.5 Gbps | 10 Gbps | 20 Gbps | |

注:HDR、EDR、FDR都在SFF-8436标准中未使用,只是保留,在SFF-8636 QSFP28中才进行使用。SDR、QDR、DDR、FDR、EDR、HDR等只是形容数据速率的量级,以单倍速2.5Gbps为准进行倍增。相关的技术如SFP+ 1x10、QSFP+ 4x10、QSFP+ 4x14、QSFP+ 4x28、CXP 12x14、CXP 12x28等。

对于高速信号编码,其代表性编码为,第一代:8B/10B编码(常用测试码型为:PRBS7 [x7+x5+1],10G以下速率如PCIe、XAUI、1000Base-LX等);第二代:64B/66B(常用测试码型为:PRBS31 [x31 + x28 + 1]);第三代:128B/132B。

7.6.2.19、波长(Bytes 186-187)

室温下标称发射机输出波长。16位值,字节186为MSB,字节187为LSB。激光波长等于16位整数值除以20nm(单位为0.05nm)。该精度范围应足以覆盖所有相关波长,同时为所有预期的DWDM应用提供足够的分辨率。为了准确表示受控波长,该值应代表中心频率对应的波长。

如果电缆被识别为铜缆,则这些寄存器将用于定义电缆衰减。0 dB衰减的指示是指衰减未知或不可用的情况。

Byte 186(00-FFh)是一个8位值,表示2.5GHz处的铜缆衰减,单位为1dB;

Byte 187(00-FFh)是一个8位值,表示在5.0GHz时铜缆衰减,单位为1dB。

7.6.2.20、波长容差(Bytes 188-189)

在所有正常工作条件下,保证+/-范围的发射机输出波长。对于直接连接电缆组件,该值为零。16位值,Byte 188为MSB,Byte 189为LSB。激光波长等于16位整数值除以200nm(0.005nm为单位)。因此,以下两个例子:

例1:对于10GBASE-LR,波长范围为1260nm ~ 1355 nm

标称波长= (1260nm + 1355nm)/2 = 1307.5nm。

表示为INT(Bytes166~167) = (1307.5nm * 20) = 26150 = 6626H

波长容差 = (1355nm – 1260)/2 = 47.5nm。

表示为INT(Bytes168~169) = (47.5nm * 200) = 9500 = 251CH

7.6.2.21、最高温度(Byte190)

允许指定除标准70摄氏度外的最高外壳温度。最高外壳温度为8位值,单位为摄氏度。00h表示标准的70摄氏度额定值。

7.6.2.22、CC_BASE(Byte 191)

检查代码是一个字节代码,可用于验证QSFP+模块page 00H中的前63个字节的串行信息是否有效。校验码为从第128字节到第190字节(含)的所有字节内容之和的低8位。

7.6.2.23、选项(Bytes192-195)

选项字段中的位应指定QSFP+模块中是否实现对应的选项(即标志位),如表39所示。

注:对有/无源铜、有源光纤、光模块,EXT_ID所表示内容信息均为R(Required,必需)。

7.6.2.24、供应商SN(Bytes 196-211)

7.6.25.25、日期代码(Bytes 212-219)

关于SN的16Byte ACSCII码和日期代码的8Byte编码,参见SFF-8472。

7.6.2.26诊断监控类型(Byte220)

“诊断监控类型”是一个1字节的字段,其中包含8个单比特指示符,用于描述如何在特定QSFP +模块中实施诊断监视。位指示符如表41所示(略,SFF-8436只有Bit3使用,其他位参照SFF-8636)。数字诊断监视器监视接收功率、偏置电流、电源电压和温度。此外,必须按照本文档中的规定编写警报和警告阈值。辅助监控字段是数字诊断的可选扩展。所有数字监控值必须在内部校准,并以本文档中定义的单位报告。Bit 3表示接收功率测量值是表示平均输入光功率还是OMA。如果该位置位,则监视平均功率。如果没有,则监控OMA。

7.6.2.27、增强选项(Byte 221)

表42中显示了增强选项字节的格式。增强选项字段的使用在子条款7.6.1.7中定义。 速率选择声明位的值均为1的状态是保留的,不应使用。

| 表42 - 增强选项(Byte221,Page 00H) | ||

| Addr | Bit | 描述 |

| 221 | 7月4日 | 保留 |

| 3 | 速率选择声明:为0时,模块不支持速率选择。 | |

| 为1时,使用扩展速率选择实现速率选择。见7.6.1.7.2 | ||

| 2 | 应用程序选择表声明:为1时,模块支持使用应用程序选择表机制进行速率选择。为0时,模块不支持应用程序选择,并且Page 01H不存在 | |

| 1-0 | 保留 | |

7.6.2.28、CC_EXT(Byte 223)

校验码是一个单字节代码,可用于验证QSFP +模块中扩展串行信息的前31个字节是否有效。校验码位Byte 192~222的所有字节的内容之和的低位8位。

7.6.2.29、特定供应商(Bytes 224-255)

该区域可能包含供应商特定信息,可从QSFP +模块中读取。数据是只读的。

7.6.3、存储器高位地址映射页01H

页面01h的格式在表43中定义。

TL字段全1时无效。当TL=62时,为最大TL值,最后一项的地址为:130+2*62 = 254、131+2*62=255。

| 表44 – 应用程序代码结构 | |||||||||||||||

| 低字节:130 + 2*条目数 | 高字节:131 + 2*条目数 | ||||||||||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 保留 | 类别 | 变化 | |||||||||||||

7.6.4、用户可写和供应商特定内存02H

可选择提供页面02作为用户可写EEPROM。主机系统可以出于任何目的读取或写入该存储器。但是,如果设置了page 00H,Byte129的Bit4,则表02H的前10个字节,字节128-137将用于存储模块的CLEI(Common Language Equipment Identifier,通用语言设备标识)代码。

7.6.5、高字节内存页面03H

存储器map页03h包含模块阈值,通道阈值和掩码以及可选的通道控制。这些显示在表45中,并在7.6.1子条款,7.6.1.6和7.6.1.4中详细描述。

7.6.5.1、模块和通道阈值

这些值存储在Page 03h的Bytes 128-223中的只读存储器中,如表46所示。每个监视器值具有相应的高报警,低报警,高警告和低警告阈值。对于所实现的每个监视器,需要高和低警报阈值,并由C(可选的)或由R(必须实现的)指示。警告阈值,高和低是可选的。这些出厂预设值允许用户确定特定值何时超出模块制造商确定的“正常”限值。这些值将随着不同的技术和不同的实现而变化。

“警报和警告阈值”区域中报告的值可能是某些选定标称操作条件下的典型值,并且可能在设置警告和/或警报标志时进行温度补偿或以其他方式调整。任何阈值补偿或调整都是供应商特定的和可选的。有关警报和警告阈值的使用,请参阅供应商的数据表。

7.6.5.2、可选通道控制

页控制位定义在表47中,(输出强度等级见表48),注:对有/无源铜、有源光纤、光模块,EXT_ID所表示内容信息均为R(Required,必需)。

RX Squelch禁用和输出控制功能是可选的; 如果实现,则使用页面03h的字节240和241为每个通道控制RX Squelch禁用和输出禁用。Squelch通常可按照4.1.3高速电气规范中的描述进行操作。在Squelch禁止寄存器中写入“1”(Byte 240,Page 03h)将禁用相关通道的Squelch。在输出禁止寄存器(Byte 241,Page03)中写入“1”会抑制相关通道的输出。当一个通道的两个寄存器中都写入“1”时,相关的输出被禁用。寄存器在通电时读取全为“0”。

7.6.5.3、通道监控掩码

表49定义了通道监控功能的掩码位。每当实现监控和相关标志时,都需要一个掩码位。