系统结构中的中断

这篇文章是四月写的一份报告,当时花费了很长时间,现在重新整理下。

什么是中断?

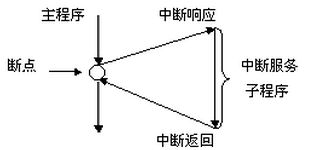

中断(Interrupt)是硬件和软件驱动事件,它使得CPU暂停当前的主程序,并转而去执行一个中断服务程序。

当CPU与外设交换信息时,若用查询方式,则CPU就要浪费很多时间去等外设。这是快速的CPU与慢速的外设之间的矛盾,也是计算机发展过程中遇到的一个严重的问题之一,为了解决这个问题,一方面要提高外设的工作速度;另一方面引入了中断的概念。

中断的分类

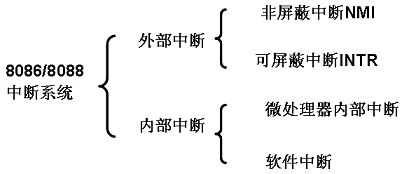

在微机系统中,中断可分为外部中断(或硬件中断)和内部中断(或软件中断)。

外部中断

外部中断是指由外部设备通过硬件请求的方式产生的中断,也称为硬件中断。

外部中断又可分为非可屏蔽中断(non-maskable interrupt,NMI)和可屏蔽中断(interrupt request),CPU通过NMI和INTR引脚分别接收这两种中断。

- 不可屏蔽中断 NMI:当外设通过非屏蔽中断请求信号向微处理器提出中断请求时,微处理器在当前指令执行结束后,就立即无条件的予以响应,这样的中断就是不可屏蔽中断。不可屏蔽中断在外部中断源中优先级最高,主要用于处理系统的意外或故障,如电源掉电、存储器读/写错误、扩展槽中输入/输出通道错误等。

- 可屏蔽中断 INTR:CPU对可屏蔽中断请求的响应是有条件的,它受中断允许标志位IF的控制。当IF=1时,允许CPU响应INTR请求;当IF=0时,禁止CPU响应INTR请求。可屏蔽中断用于CPU与外设进行数据交换。可屏蔽中断受8259A可编程中断控制器的控制。时钟中断(8253定时器发出的中断信号)就属于可屏蔽中断。

系统中必须由硬件实现的中断有:保护中断点,转向中断服务程序入口。

内部中断

内部中断是由CPU运行程序错误或执行内部程序调用引起的一种中断,也称为软件中断,它分为异常和INT n指令中断两类,内部中断不受eflags中IF位的影响。

异常分为故障(Fault)、陷阱(Trap)和中止(Abort)3种。是在指令执行过程中由于微处理器内部操作发生异常引起的,如硬件失效或非法的系统调用,以及程序员预先设置断点等。

INT n指令中断是指系统执行INT n指令所引起的中断。其实INT n和INT0也归类于异常,属同步性事件。

系统中必须由软件实现的中断有:中断服务,返回到中断点。

CPU处理中断的过程:

在微机系统中,对于外部中断,中断请求信号是由外部设备产生,并施加到CPU的NMI或INTR引脚上,CPU通过不断地检测NMI和INTR引脚信号来识 别是否有中断请求发生。对于内部中断,中断请求方式不需要外部施加信号激发,而是通过内部中断控制逻辑去调用。无论是外部中断还是内部中断,中断处理过程 都要经历以下步骤: 请求中断→响应中断→关闭中断→保留断点→中断源识别→保护现场→中断服务子程序→恢复现场→中断返回。

详细的过程如下:

- 请求中断

当某一中断源需要CPU为其进行中断服务时,就输出中断请求信号,使中断控制系统的中断请求触发器置位,向CPU请求中断。系统要求中断请求信号一直保持到CPU对其进行中断响应为止。 - 中断响应

CPU对系统内部中断源提出的中断请求必须响应,而且自动取得中断服务子程序的入口地址,执行中断 服务子程序。对于外部中断,CPU在执行当前指令的最后一个时钟周期去查询INTR引脚,若查询到中断请求信号有效,同时在系统开中断(即IF=1)的情 况下,CPU向发出中断请求的外设回送一个低电平有效的中断应答信号,作为对中断请求INTR的应答,系统自动进入中断响应周期。 - 关闭CPU中断

CPU响应中断后,输出中断响应信号,自动将状态标志寄存器FR或EFR的内容压入堆栈保护起来,然后将FR或EFR中的中断标志位IF与陷阱标志位TF清零,从而自动关闭外部硬件中断。因为CPU刚进入中断时要保护现场,主要涉及堆栈操作,此时不能再响应中断,否则将造成系统混乱。 - 保护中断点

保护断点就是将CS和IP/EIP的当前内容压入堆栈保存,以便中断处理完毕后能返回被中断的原程序继续执行,这一过程也是由CPU自动完成。 - 撤销设备的中断请求

- 避免开CPU中断后,再次请求中断服务。

- 保护硬件现场

保存处理机状态字PSW及堆栈指针SP中的内容,执行压栈操作。 - 中断源识别

当系统中有多个中断源时,一旦有中断请求,CPU必须确定是哪一个中断源提出的中断请求,并由中断控制器给出中断服务子程序的入口地址,装入CS与IP/EIP两个寄存器。CPU转入相应的中断服务子程序开始执行。 - 改变设备的屏蔽状态

- 转向中断程序入口

- 保护软件现场

主程序和中断服务子程序都要使用CPU内部寄存器等资源,为使中断处理程序不破坏主程序中寄存器的内容,应先将断点处各寄存器的内容压入堆栈保护起来,再进入的中断处理。现场保护是由用户使用PUSH指令来实现的。 - 中断服务

包括开CPU中断,执行中断服务程序,关CPU中断。中断服务是执行中断的主体部分,不同的中断请求,有各自不同的中断服务内容,需要根据中断源所要完成的功能,事先编写相应的中断服务子程序存入内存,等待中断请求响应后调用执行。 - 恢复现场

包括恢复软件现场,恢复屏蔽状态,恢复硬件现场。当中断处理完毕后,用户通过POP指令将保存在堆栈中的各个寄存器的内容弹出,即恢复主程序断点处寄存器的原值。 - 中断返回

在中断服务子程序的最后要安排一条中断返回指令IRET,执行该指令,系统自动将堆栈内保存的 IP/EIP和CS值弹出,从而恢复主程序断点处的地址值,同时还自动恢复标志寄存器FR或EFR的内容,使CPU转到被中断的程序中继续执行。

中断机制

X86的中断机制

X86 CPU支持256个中断向量,0~19是系统预定义的异常和NMI,20~31被Intel保留,所以外部中断从32开始(Linux使用80h实现系统调用)。

CPU处理的流程都一样,在执行完当前指令后,根据中断源提供的中断向量,在IDT中找到并调用相应的服务例程。

x86中断分为实模式中断和虚模式中断。在实模式下,0~1KB的内存存放中断向量表,每项由2字节的段地址和2字节的段偏移组成,共256项。

保护模式下,通过中断门实现。x86中断系统具体分类如下结构:

- 外部中断 :来自CPU外部,由外设的请求引起,通过外部硬件产生,也称为硬件中断。

- 内部中断 :来自CPU内部,由执行指令引起的。

- 非屏蔽中断 :通过NMI引脚引入CPU,不受中断允许标志IF的屏蔽,一个系统一般只允许有一个非屏蔽中断。

- 可屏蔽中断 :通过INTR引脚引入CPU,只有当中断允许标志位IF=1时,才能被CPU响应。通过8259A,一个系统中可有多个可屏蔽中断。

ARM的中断机制

ARM处理器的中断主要有两种:IRQ普通中断和FIQ快速中断。快速中断本质上与普通中断没有太大的差别,它们在处理机制上有许多相同的地方。IRQ中断是最频繁的也是最为影响系统性能的。

在IRQ中断发生时,ARM处理器的硬件会自动执行以下工作:

- 将被中断任务模式的CPSR值保存到IRQ模式中的SPSR寄存器中;

- 置位I位(禁止IRQ中断);

- 清零T位(进入ARM状态);

- 设置MOD位,切换处理器模式为IRQ模式;

- 将被中断任务模式的PC值保存到IRQ模式中的LR寄存器中;

- 将CPSR中的bit7位置1禁止后继IRQ中断的发生;

- PC被赋予跳转指令的地址值,实现跳转。

- 异常处理结束后,异常程序完成下列动作:

- 将SPSR寄存器的值复制到CPSR寄存器;

- 将LR寄存的值减去一个常量后复制到PC寄存器,跳转至被中断的用户程序。

- 清零在入口置位的中断禁止标志。

FIQ适用于对一个突发事件的快速响应,这是因为该模式下有8个寄存器用来满足寄存器保护的需要。特权模式下,可通过置位CPSR的F位禁止FIQ异常。

IRQ异常由nIRQ输入端的低电平所产生的正常中断。IRQ的优先级低于FIRQ。相应的在一个特权模式下,都可通过置位CPSR中的I位来禁止IRQ。

ARM的中断机制特点

主要由中断源和控制寄存器两大部分组成,其寄存器主要有四种:模式、屏蔽、优先级、挂起寄存器。具体如下图:

中断系统有6个分仲裁器和一个总仲裁器,每一个仲裁器都可以处理6路中断。

MIPS的中断机制

MIPS中有3种中断模式:

- 兼容中断模式(Interrupt Compatibility mode);

- 向量中断模式(Vectored Interrupt (VI) mode);

- 外部中断控制器模式(External Interrupt Controller (EIC) mode)。

MIPS的中断处理,通常来说,和其他体系结构的 中断处理,没有太多的区别,总的来说分为三段:

- 保存现场寄存器组(Register File)。在堆栈中开辟一段区域,将32个通用寄存器和CP0的相关寄存器,如Status,BadVaddr,Cause等,保存在这段内存中。其中尤为重要的是 EPC,EPC指向引发异常时的指令。

- 异常处理部分。以Address Error异常为例,当异常发生时,根据保存的BadVaddr,调用两次非对齐加载/存储指令,对内存地址进行数据的读写操作。

- 返回。将保存在堆栈中的寄存器组内容恢复。

从异常状态返回的这个动作,是由硬件完成的。它必须同时完成三个操作:

- 将SR寄存器恢复;

- 返回到EPC寄存器所指向的地址继续执行;

- 恢复到用户态。

如果这三个过程没有能够“原子地”执行完毕,那么将会导致一个安全漏洞,用户有可能在某种情况下僭越CPU内核态设定的壁垒,从而非法获得管理员权限。

MIPS的中断机制特点

MIPS CPU有8个独立的中断位(在Cause寄存器中),其中,6个为外部中断,2个为内部中断(可由软件访问)。一般来说,片上的时钟计数/定时器,会连接到一个硬件位上去。

当MIPS CPU发生中断后,CPU的状态变化到如下状态,总结如下列表:

EPC寄存器保存了发生中断是程序执行指令的地址

CP0中STATUS寄存器 EXL置位为1,表示正在异常状态,这个时候CPU不能再响应中断(不管IE是否开启),自动进入核心状态。

CP0中CAUSE寄存器中ExcCode为0,表示是中断异常

CP0中CAUSE寄存器IP被设置为不同的中断号

规则如下:

- SR(IE)位控制全局中断响应,为0的话,就禁止所有中断;

- SR(EXL)和SR(ERL)位(任何一个)如果置1的话,会禁止中断;

- SR(IM)有8位,对应8个中断源,要产生中断,还得把这8位中相应的位置1才行;

中断处理程序也是用通用异常入口。但有些新的CPU有变化。

三种机器中断处理机制的不同点:(以中断源为例)

当CPU响应中断、保护断点之后,就要进行中断源的识别,即寻找中断源,找到相应的中断服务程序入口。识别中断源有三种方法:查询法、向量法和强置程序计数器法。

查询法(ARM使用):

这是通过程序来查询是哪一个中断源提出的中断请求。该方法需要必要的硬件支持。设置一个输入端口,以便CPU可通过该端口读取各个中断请求触发器的 状态。在响应中断周期之后,对所有的中断,都先进入到这个查询流程。先看中断源1 是否提出请求,若是,转去执行中断源1的中断服务程序,否则再看中断源2是否提出 请求,若是,转去执行中断源2的中断服务程序。否则继续查看后面的中断源。

查询的顺序决定了中断的优先级,这是因为,当发现一个中断源提出中断请求后,就转去执行相应的服务程序,而不再继续向下查找,不管它们是否也提出了请求。中断源1的级别最高,中断源2的级别次之,中断源n的级别最低。

查询法的优点是硬件简单、程序层次分明,只要改变程序中的查询次序即可改变中断源的中断优先级,而不必变更硬件连接,其缺点是速度慢(从CPU响应中断到进入中断服务的时间较长),实时性差,特别是当中断源较多时,尤为突出。此外,查询要占用CPU时间,降低了CPU的使用效率。

向量法(x86使用):

这是一种硬件方法。在CPU发出中断响应信号INTA时,由硬件产生请求中断且在当前所有请求中级别最高的中断源的中断标识码(早期微机系统中称之为中断向量,向量法因此得名,而在8086/8088系统以及PC系列机中称之为中断类型码)。中断标识码是中断源的识别标志,可用来形成相应的中断服务程序的人口地址或存放中断服务程序的首地址。该方法需要的硬件支持。当有中断源提出请求时,中断排队与编码器进行判优并产生其中级别最高的中断源的中断标识码。在INTA来时,CPU通过三态门获得中断标识码。

用向量法识别中断源不占用CPU额外的时间,在中断响应周期即可完成,所以得到广泛的应用。即便在功能相对简单的单片机中,一般也采用此方法。

MIPS和ARM都是RISC架构,但是两者在很多方面有比较大的区别。CPU的行为比ARM更加精简,连TBL查找都需要靠软件来设置。ARM更像是介于MIPS和X86之间的一种CPU,结合了两者的一些特点。

参考文献

《计算机系统结构》(第二版)清华出版社 郑炜民 汤志忠 编著

《嵌入式系统结构》清华出版社 李宥谋 编著