单板硬件设计

1、电源滤波

1.1、输入侧电源的滤波:

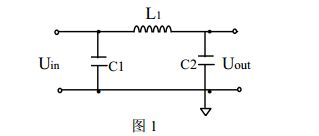

对于单板的电源输入侧,出于上电特性及热插拔的需要,需要加π型滤波电路,基本电路形式为图1所示。

其中,C1为输入侧的输入电容,L为输入电感,C2为π型滤波电路的输出侧电容;C1的主要目的是为了限制上电瞬间的电压上升率,并滤除输入侧电路由电源引入的纹波,因此,C1一般是由直流电容及交流电容组成的并联电容组,其中直流电容的主要作用是去除电容中的纹波,而交流电容的主要作用是为了去耦。

从参数及器件选择上,输入侧一般选取胆电容,去耦电容的值为0.01uf-1uf之间,针式或贴片均可,但从生产工艺的角度,则以选取贴片为佳,推荐的参数为直流电容10uf,交流电容0.1uf。

电感的作用为抑制电流变化率,电感越大,抑制效果越好,但同时电感太大时的上电特性不好,上电及下电时,电感两端会产生反电势,这样会对后面的负载产生影响,故参数不宜过大,因而推荐的参数为10uH。

输出侧的电容不仅要完成去耦及滤纹波的作用,而且还须维持滤波后电平不受电感反电势的影响,兼顾考虑板内负载大小及其他去耦电容的数量,推荐参数为直流电容10uf,直流电容0.01-1uf。

1.2、IC的电容去耦:

经过π型滤波电路的瞬态电压特性会有较大改善,但由于负载及非线性器件的影响,使得电源纹波不可能完全消除,且分布特性对于电源的特性影响较大,因此,在器件两端应加上去耦电容,以改善板内IC侧的电源特性。器件选择同1.1所述,推荐的参数为直流电容10uf,交流电容推荐0.01-1uf。

2、带电插拔座:

带电插拔座的特性是先使地线连接,然后电源部分再上电,这样使得热插拔的上电过程有序,避免了电源上电不均衡所带来的冲击。

而在系统调试中,一些单板的热插拔成为了一种经常且必要的行为,而热插拔所带来的电流及电压冲击是及其巨大的,这时对单板的损伤是由电流及电压变化率过快所造成的,因此,遏制电流电压变化率,减轻负载突变是热插拔的先决条件,但单靠π型滤波电路是不够的,这样需要有热插拔的单板必须加带电插拔座。

3、上下拉电阻:

3.1、上拉电阻的选取原则:

A. 提高灌电流的能力:

单板内部的器件功耗及驱动能力各不相同,这样在器件连接时的灌电流能力不尽相同,连接上会有驱动问题,此时需要加上拉电阻。

B.电平兼容:

板内或板间器件选取各不相同,信号电平特性各不相同,出于兼容性考虑,须加上拉电阻仪保证兼容性。

C.电平稳态的特性:

个别器件在上电时要求莫些管脚的初始电平固定为高,此时必须加上拉电阻以保证器件能够正常工作。

D.器件及参数选取:

对于A,B,一般的上拉电阻选取2K-1M欧姆,视负载情况而定,重负载时电阻应选取靠近下限,轻负载是选取上限,这里的负载以器件功耗指标来确定;对于上述C的情况,则以该种器件的数据特性来决定。器件一般以金属膜的电阻或排阻为准。

3.2、下拉电阻的选取原则:

A.电平兼容:

板内或板间器件选取各不相同,信号电平特性各不相同,出于兼容性的考虑,需加下拉电阻以保证兼容性。

B.端接:

板内或板间的信号频率较高或信号上升沿较陡时,需要加端接电阻下拉到地,一般此时经常性的会再串入一个适当的电容。

C.电平稳定特性:

个别器件在上电时要求某些管脚的初始电平为低,此时必须加下拉电阻以保证器件能够正常工作。

D.器件及参数选取:

对于A,下拉电阻一般选取1K-100K欧姆,视负载电平情况而定,CMOS电平的负载,电阻应选取下限,TTL电平时选取上限,这里的电平以负载指标来确定;对于B的情况,一般选取75-150Ω的电阻;对于C的情况,则以该器件的数据特性来决定;器件一般以金属膜的电阻或阻排为准。

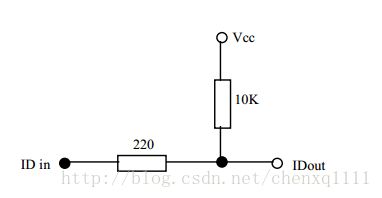

4、ID的标准电路

ID即为单板的板位信号,一般用来作邮箱地址译码选择,ID信号在母板上接VCC或GND,所以在单板上需作处理,典型电路如下:

5、 高速时钟设计

在PCB布线中对高速时钟信号线,应少打过孔,减少线径变化层次,维持线宽一致性,不用T型接头分支,增加时钟线与其他线的间距,减少平行走线,条件允许的情况下,在时钟线两侧加上地线隔离。另外可采用终端匹配技术消除反射。

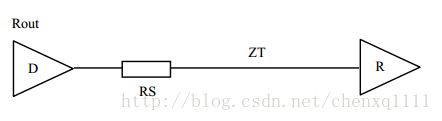

(1) 始端电阻

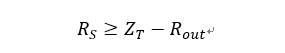

在驱动端,加一个小电阻值串阻,反射将发生在负载端,目的是确保反射波不会从源端再反射回来、串阻的值须满足下列等式:

Rs--串阻

Z

T--线的特性阻抗Rout--源端输出阻抗

串阻方式对每根时钟线只需一个电阻,几乎没有直流功耗,而且电阻还起着限流的作用,减小地线反冲。但是反射仍然有可能发生,沿线也将存在中间电压,因此,这种方式不适合分布式负载。另外,高的电阻值还会减少时钟波形的幅度和增加上升时间(在驱动端的接口芯片应为74AC16244系列芯片)。

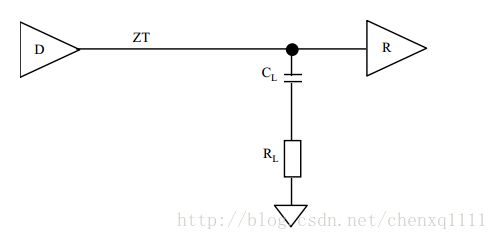

(2)终端并联AC方式

在负载端并联一个RC,电容值的选取一定要非常小心,它的值必须大的能够吸收传输波的能量,但又一定要小的不会损害信号的上升时间,通常用小于50PF的电容。电阻值RL大约等于ZT(几十欧姆左右)。

并接RL方式对时钟线来说很少采用,对信号的上升时间损害较大,但它没有DC功耗,能够消除长线的反射。

总的来说,终端匹配技术,常用来防止电压反射,减小上冲和下冲,防止时钟错误和损害片子。对一个系统来说,可选的终端匹配技术有很多,弹药确保终端远见尽量靠近源端(串阻)或靠近负载端(并接RC),这样可以减少诱导电感,使匹配有效。

6、接口驱动及支持芯片

这里所说的接口主要是指总线(地址总线,数据总线等),从驱动能力和速度上综合考虑,对地址总线,控制总线和时钟信号等统一采用TI的74AC16244;对双向的数据总线采用TI的74AC16245。禁止选用74FCT16244或74FCT16245系列芯片。

7、复位电路

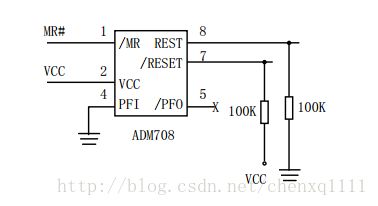

复位电路采用AD公司的复位芯片ADM708,常用电路如下:

/MR为复位信号输入端,低电平有效。它可以直接和手动复位开关相连,也可以接由逻辑电路产生的软复位信号,或二者的组合。

8、 Watchdog电路

根据清除Watchdog方法的不同,常用到两种Watchdog电路。

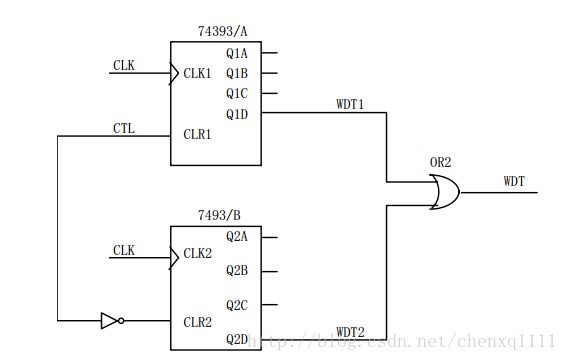

1)、利用并行口某一位对Watchdog进行清除,电路原理如下:

这种电路的特点是对Watchdog不能进行开关,CTL脚为高电平或低电平超过一定的时间就会引起Watchdog触发,避免了因CPU死机,Watchdog造成被长期清除的现象。

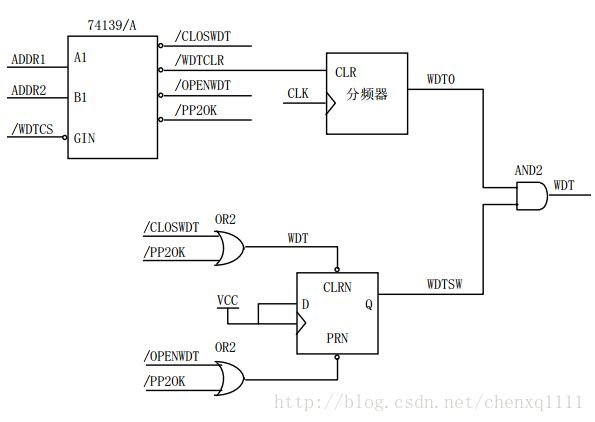

2)、Watchdog占用CPU的地址空间,电路原理如下:

这种电路的特点是对Watchdog可以灵活地进行开关。并且只要Watchdog打开,如果没有定时清Watchdog,就一定会出现Watchdog无法触发的现象。