Zynq : Using the AXI DMA

此文是转载自 http://www.fpgadeveloper.com/2014/08/using-the-axi-dma-in-vivado.html

我在测试AXI DMA时参考了这个文章,调通了xilinx官方的axidmatest.c

环境:uboot:2015.4 kernel 2015.3 vivado 2015.4.1

修改的地方:

1、用SDK生成设备树要添加axidmatest的节点:

axidma-test{

compatible = "xlnx,axi-dma-test-1.00.a";

dmas = <&axi_dma_0 0 &axi_dma_0 1>;

dma-names = "axidma0", "axidma1";

};

这个在xilinx官方论坛上有个帖子有说明,在4.0内核此要这个。

2、在vivado中打开AXI DMA 的IP,修改width of Buffer Length Register 修改为16(默认是14,我不知道这个有没有影响)。

n a previous tutorial I went through how to use the AXI DMA Engine in EDK, now I’ll show you how to use the AXI DMA in Vivado. We’ll create the hardware design in Vivado, then write a software application in the Xilinx SDK and test it on the MicroZed board (source code is shared on Github for the MicroZed and the ZedBoard, see links at the bottom).

What is DMA?

DMA stands for Direct Memory Access and a DMA engine allows you to transfer data from one part of your system to another. The simplest usage of a DMA would be to transfer data from one part of the memory to another, however a DMA engine can be used to transfer data from any data producer (eg. an ADC) to a memory, or from a memory to any data consumer (eg. a DAC).

Tutorial overview

In this design, we’ll use the DMA to transfer data from memory to an IP block and back to the memory. In principle, the IP block could be any kind of data producer/consumer such as an ADC/DAC FMC, but in this tutorial we will use a simple FIFO to create a loopback. After, you’ll be able to break the loop and insert whatever custom IP you like.

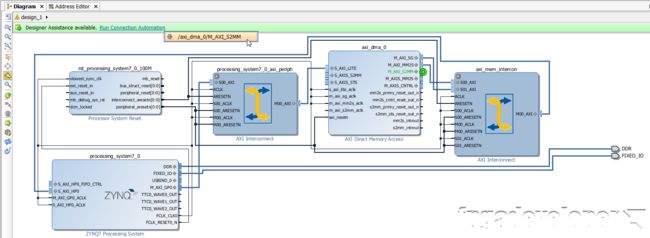

The block diagram above illustrates the design that we’ll create. The processor and DDR memory controller are contained within the Zynq PS. The AXI DMA and AXI Data FIFO are implemented in the Zynq PL. The AXI-lite bus allows the processor to communicate with the AXI DMA to setup, initiate and monitor data transfers. The AXI_MM2S and AXI_S2MM are memory-mapped AXI4 buses and provide the DMA access to the DDR memory. The AXIS_MM2S and AXIS_S2MM are AXI4-streaming buses, which source and sink a continuous stream of data, without addresses.

The block diagram above illustrates the design that we’ll create. The processor and DDR memory controller are contained within the Zynq PS. The AXI DMA and AXI Data FIFO are implemented in the Zynq PL. The AXI-lite bus allows the processor to communicate with the AXI DMA to setup, initiate and monitor data transfers. The AXI_MM2S and AXI_S2MM are memory-mapped AXI4 buses and provide the DMA access to the DDR memory. The AXIS_MM2S and AXIS_S2MM are AXI4-streaming buses, which source and sink a continuous stream of data, without addresses.

Notes:

- MM2S stands for Memory-Mapped to Streaming, whereas S2MM stands for Streaming to Memory-Mapped.

- When Scatter-Gather is used, there is an extra AXI bus between the DMA and the memory controller. It was left out of the diagram for simplicity.

Requirements

Before following this tutorial, you will need to do the following:

- Vivado Instructions were written for version 2014.2, but the source code will be maintained to the latest version

- MicroZed

- Platform Cable USB II (or equivalent JTAG programmer)

Start from the base project

We’ll start this tutorial with the base system project for the MicroZed that you can access here:

Base system project for the MicroZed

Add the AXI DMA

- Open the base project in Vivado.

- In the Flow Navigator, click ‘Open Block Design’.

- The block diagram should open and you should only have the Zynq PS in the design.

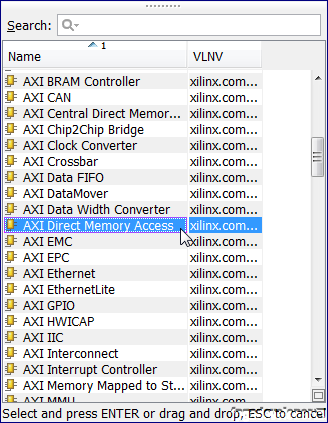

- Click the ‘Add IP’ icon and double click ‘AXI Direct Memory Access’ from the catalog.

Connect the Memory-mapped AXI buses

- The DMA block should appear and designer assistance should be available. Click the ‘Run Connection Automation’ link and select ‘/axi_dma_0/S_AXI_LITE’ from the drop-down menu.

- Click ‘OK’ in the window that appears. Vivado will connect the AXI-lite bus of the DMA to the General Purpose AXI Interconnect of the PS.

- Your block diagram should now look like this :

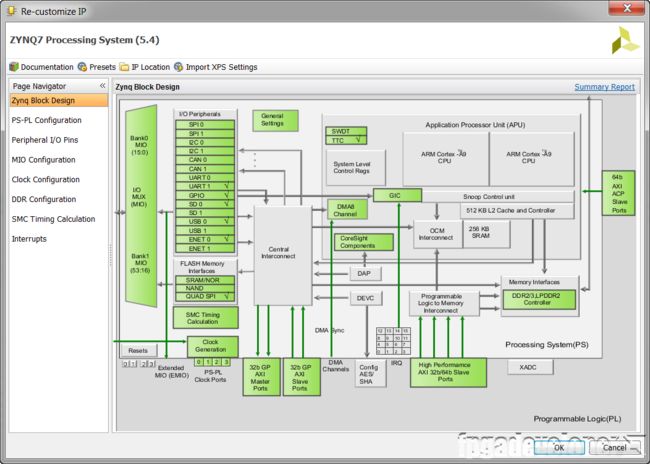

- Now we need to connect AXI buses M_AXI_SG, M_AXI_MM2S and M_AXI_S2MM of the DMA to a high performance AXI slave interface on the PS. Our PS doesn’t seem to have a high-performance AXI slave interface, so we need to change the Zynq configuration to enable one. Double click on the Zynq block.

- Select ‘PS-PL Configuration’, open the ‘HP Slave AXI Interface’ branch and tick the ‘S AXI HP0 interface’ to enable it. Then click OK.

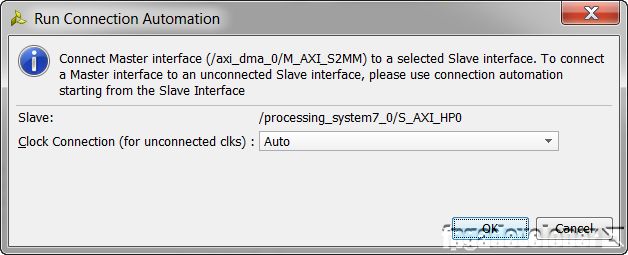

- The high-performance AXI slave ports should now be visible in the block diagram, and designer assistance should be available. Click the ‘Run Connection Automation’ link and select ‘/processing_system7_0/S_AXI_HP0’ from the drop-down menu.

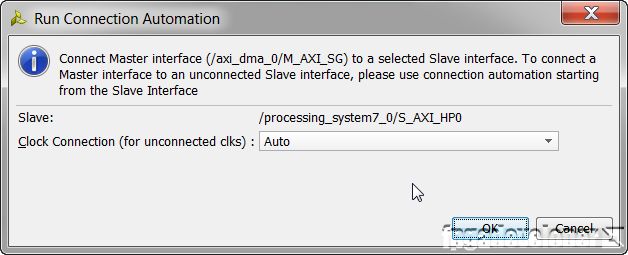

- In the window that appears, make sure that Vivado intends to connect it to the DMA and click OK.

- Designer assistance should again be available, click the ‘Run Connection Automation’ link and select ‘/axi_dma_0/M_AXI_SG’ from the drop-down menu.

- In the window that appears, click OK.

- Designer assistance should still be available, click the ‘Run Connection Automation’ link and select ‘/axi_dma_0/M_AXI_S2MM’ from the drop-down menu.

- In the window that appears, click OK.

Now all the memory-mapped AXI buses are connected to the DMA. Now we only have to connect the AXI streaming buses to our loopback FIFO and connect the DMA interrupts.

Add the FIFO

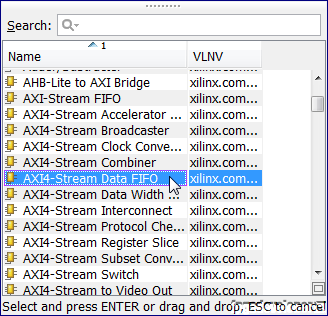

- Click the ‘Add IP’ icon and double click ‘AXI4-Stream Data FIFO’ from the catalog.

- The FIFO should be visible in the block diagram. Now we must connect the AXI-streaming buses to those of the DMA. Click the ‘S_AXIS’ port on the FIFO and connect it to the ‘M_AXIS_MM2S’ port of the DMA.

- Then connect the ‘M_AXIS’ port on the FIFO and connect it to the ‘S_AXIS_S2MM’ port of the DMA.

- Now we must connect the FIFO clock and reset. Click the ‘s_axis_aresetn’ port of the FIFO and connect it to the ‘axi_resetn’ port of the DMA.

- Click the ‘s_axis_aclk’ port of the FIFO and connect it to the ‘s_axi_lite_aclk’ port of the DMA.

Remove the AXI-Streaming status and control ports of the DMA

In our design, we won’t need the AXI-Streaming status and control ports which are used to transmit extra information alongside the data stream. You might use them if you were connecting to the AXI Ethernet core or a custom IP that made use of them.

- In the block diagram, double click the AXI DMA block.

- Un-tick the ‘Enable Control / Status Stream’ option and click OK.

Connect the DMA interrupts to the PS

Our software application will test the DMA in polling mode, but to be able to use it in interrupt mode, we need to connect the interrupts ‘mm2s_introut’ and ‘s2mm_introut’ to the Zynq PS.

- First we have to enable interrupts from the PL. Double click the Zynq block and select the Interrupts tab.

- Tick ‘Fabric Interrupts’ and ‘IRQ_F2P[15 :0]’ to enable them, and click OK.

- Click the ‘Add IP’ icon and double-click ‘Concat’ from the catalog.

- Connect the ‘dout’ port of the Concat to the ‘IRQ_F2P’ port of the Zynq PS.

- Connect the ‘mm2s_introut’ port of the DMA to the ‘In0’ port of the Concat.

- Connect the ‘s2mm_introut’ port of the DMA to the ‘In1’ port of the Concat.

Validate and build the design

- From the menu select Tools->Validate Design.

- You should get this message saying that validation was successful.

- We can clean up the block diagram by clicking the Regenerate Layout icon.

- Our block diagram now looks like this :

- In the Flow Navigator, click ‘Generate Bitstream’.

Export the hardware design to SDK

Once the bitstream has been generated, we can export our design to SDK where we can develop the software application that will setup a DMA transfer, wait for completion and then verify the loopback.

- In Vivado, from the File menu, select “Export->Export hardware”.

- In the window that appears, tick “Include bitstream” and click “OK”.

- Again from the File menu, select “Launch SDK”.

- In the window that appears, use the following settings and click “OK”.

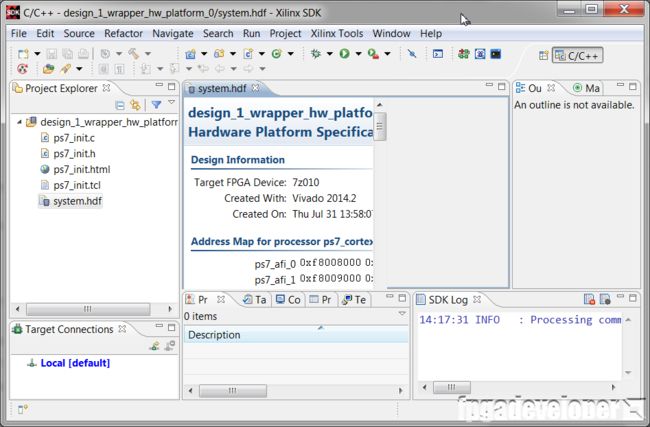

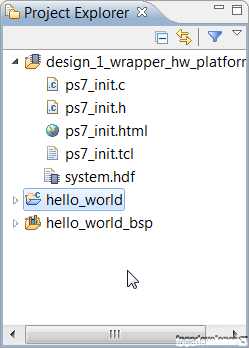

At this point, the SDK loads and a hardware platform specification will be created for your design. You should be able to see the hardware specification in the Project Explorer of SDK as shown in the image below.

We are now ready to create the software application.

Create a Software application

At this point, your SDK window should look somewhat like this:

To make things easy for us, we’ll use the template for the hello world application and then modify it to test the AXI DMA.

- From the File menu, select New->Application Project.

- In the first page of the New Project wizard, choose a name for the application. I’ve chosen “hello_world”. Click “Next”.

- On the templates page, select the “Hello World” template and click “Finish”.

- The SDK will generate a new application which you should find in the Project Explorer as in the image below.

The “hello_world” folder contains the Hello World software application, which we will modify to test our AXI DMA.

Modify the Software Application

We need to modify the hello world software application to test our DMA.

- From the Project Explorer, open the “hello_world/src” folder. Open the “helloworld.c” source file.

- Replace all the code in this file with the code that you will find on Github here:https://github.com/fpgadeveloper/microzed-axi-dma/blob/master/SDK/hello_world/src/helloworld.c

- Save and close the file. The application should build automatically.

The application source code is derived from an example provided by Xilinx in the installation files. You can find it at this location on your PC:

C:\Xilinx\14.7\ISE_DS\EDK\sw\XilinxProcessorIPLib\drivers\axidma_v7_02_a\examples\xaxidma_example_sg_poll.c

By the way, if you didn’t know about it already, that folder contains heaps of examples that you will find useful, I suggest you check it out.

Test the design on the hardware

To test the design, we are using the MicroZed board from Avnet. Make the following setup before continuing:

- On the MicroZed, set the JP1, JP2 and JP3 jumpers all to the 1-2 position.

- Connect the USB-UART (J2) to a USB port of your PC.

- Connect a Platform Cable USB II programmer (or similar device) to the JTAG connector. Connect the programmer to a USB port of your PC.

Now you need to open up a terminal program on your PC and set it up to receive the test messages. I use Miniterm because I’m a Python fan, but you could use any other terminal program such as Putty. Use the following settings:

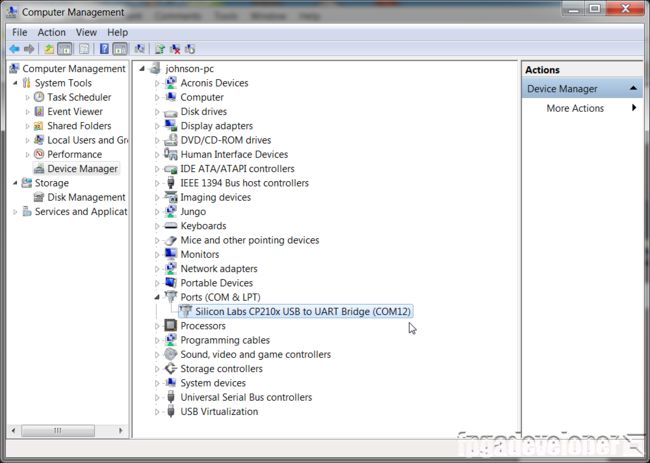

- Comport – check your device manager to find out what comport the MicroZed popped up as. In my case, it was COM12 as shown below.

- Baud rate: 115200bps

- Data: 8 bits

- Parity: None

- Stop bits: 1

Now that your PC is ready to receive the test messages, we are ready to send our bitstream and software application to the hardware.

- In the SDK, from the menu, select Xilinx Tools->Program FPGA.

- In the Program FPGA window, we select the hardware platform to program. We have only one hardware platform, so click “Program”.

- The bitstream will be loaded onto the Zynq and we are ready to load the software application. Select the “hello_world” folder in the Project Explorer, then from the menu, select Run->Run.

- In the Run As window, select “Launch on Hardware (GDB)” and click “OK”.

- The application will be loaded on the Zynq PS and it will be executed. Look out for the results in your terminal window!