【人工智能系列 - 智能硬件 - 13】附录:JBits SDK的详细说明

JBits软件是由Xilinx公司Levi等人开发的,提供了对Virtex FPGA进行实时重构和实时参数化设计的接口和工具。

这些接口和工具可以用来对设计过程进行编码、调试、仿真和校验。

每个接口工具提供了不同抽象层次的设计,用户可以根据需要选择设计的抽象层次。

JBits API是用Java语言编写的类函数包,它提供了配置Virtex器件的最底层接口,可以用来构建数字系统设计和可参数化核模块在Xilinx FPGA器件上运行及实现。

JBits SDK支持对Virtex FPGA的动态局部重构设计,并且保证位流文件的安全格式。

它是一系列的Java类,提供对Xilinx Virtex II FPGA位流进行操作的API接口。

这种接口的操作对象是由Xilinx设计工具生成的位流,或者从实际硬件中读回的位流。

这就提供了对Xilinx Virtex II 系列FPGA设备进行设计、修改和动态调整电路的能力。

JBits所使用的设计模式是一个二维的CLB阵列。每个CLB通过行列值被引用,并且所选中的CLB的所有的配置资源都可能被设置或探查。另外,所选CLB邻近布线资源的控制都是可用的。因为编码是在Java里被编写,编译时间是非常快的,并且因为控制是在CLB级的,位流能够特别地被修改或者非常快速地生成。这种API接口一直被用来构建通路并且改变已存在电路。最后,这种API接口可能被用作构建其它工具的基础平台。这包括传统的设计工具为执行作业如电路布局布线,还有执行更为精细规定作业任务的专用工具。

使用JBits产生配置数据有可能会破坏芯片设备和芯片所连接的那些硬件设备。

因为它是一种强力的工具,要确保你很清楚自己的电路和结果在涉及到配置和重配置芯片设备时。

JBits具有以下特征:

- 每秒一万行的编译速度;

- 动态重配置支持;

- 电路的运行时参数支持;

- 预布局、预布线支持;

- 简单的CLB可编程模型阵列;

- 支持Virtex系列;完全由Java实现。

JBits3.0

JBits3.0只支持Virtex-II结构,对于Virtex应用需要使用JBits2.8。

JBits3.0只提供了JBits的精髓部分,包括Bit、Tile、Device classes、get/set API、Wire Database和局部重配置的支持。没有提供较高层的JRoute和CoreTemplate。CoreTemplate的缺少意味着没有核可视化和网表。它不包含BoardScope和DeviceSimulator工具。没有提供应用软件、核库和基本要素图元。

它的层次结构不同于JBits2.8。新的类和类的成员被创建,旧类被移除、重命名或整理。尽管JBits2.8提供了一个模块组件生成能力使用RTPCores,我们注意到大部分用户更喜欢用ISE工具发展和实现模块只要有可能,JBits典型地被用于作为一个必须的基础。自JBits2.8发展后,ISE模块设计流也开始支持部分重配置。这已经改变了JBits的关注点从模块生成到配置,例如改变LUTs。

JBits3.0提供了一个基本层,在用户能够发展他们自己的抽象概念和工具。

例如,Wire Database API适合于特定应用布线的发展。

JBits实现局部重构的过程

- 采用jBit.read()方法读入初始零位流nullfile。

- 采用JBits中实现连线的方法Bitstream.connect()和添加子核的方法addChild()在进化设计的顶层核EHTop中控制RC1000pp板上SRAM读/写的信号、实现FPGA与SRAM通信的接口、演化区域CLB间随机连接状态及CLB内部连接情况等写入位流中。

- 使用clearPartial()方法清除部分重构标志,启动第一次对硬件的完全配置,即生成包含SRAM读写控制电路、FPGA与SRAM接口电路和演化区域CLB间连线及其内部连线的位流。

- 使用getPartial()方法,设置部分重构标志,这样,每次对硬件的配置将只包含使用jBits.set()方法修改的数据帧部分。

- 使用board.setConfiguration(device, jbits.getPartial())方法,利用与硬件接口XHWIF启动对于演化区域中修改的部分进行重构。

JBits设计流

JBits API可以用来构建数字设计和参数核,能在Xilinx Virtex II FPGA devices中执行的。

它们提供了对硬件的最底层的接口,因此能够提供一个构造传统电路布局布线的基础,和一些专用工具联合实现更大精细的任务。

它提供了设计、改变和动态改变Xilinx Virtex II FPGA devices电路的能力,提供了通向CLB中的LUT的通道和布线资源。

设备结构被表示为一个二维CLB阵列在JBits里。每个CLB通过行列值被引用,并且在所选择的CLB中的所有的配置资源都可以被设置或探查。接近于所选CLB的布线资源的控制在API中也是可利用的。

静态设计流,使用JBits产生静态设计位流文件,它不同于传统的CAD工具,不使用HDL或方案设计入口,通过API使用JAVA编程实现。应用获取位流文件作为输入并生成配置数据,数据被改变通过使用API并且被输出到位流文件来配置硬件设备。一旦下载到FPGA,设计可以通过XHWIF接口进行调试。设计的起始位流通过Xilinx ISE设计工具产生。

动态设计流,JBits的真正威力体现于它在发展Java实时运行配置(RTR)应用上的使用(Design Flow for RTR Mode)。电路可以通过一个Java应用(负责与包含Virtex II device的电路板进行通信)在运行中实时改变配置,使用JBits指定设计并使用XHWIF API下载Java应用中的设计。输入Java应用中的位流可以是空位流或者已存在设计的位流。

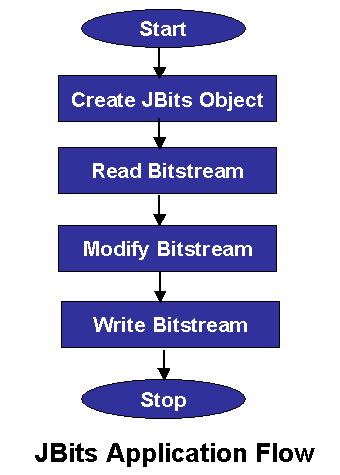

JBits应用的关键步骤流程

1)创建一个JBits对象

首先构造对象,构造函数很简单,并带有一个device参数。

设备表可以在device类中找到,构造函数建立设备模型并且执行多种初始化操作。

2)读位流到该对象

读位流文件到所构造的对象并映射到所建立的设备模型中,一旦位流载入,位形式的配置数据就能够被读和写。

注意各种配置和I/O异常可能被该函数出现。

3)结合设计数据改变位流

改变给定设计资源的配置数据,资源通过CLB的行列值来确定。

所选CLB的资源由一个常数来定义,这些常数被定义在包含定义对象的Java类里。例如,使用F1_B0类中的F1_B0常数(F1_B0.F1_B0)完成SLICE0 F1输入的配置设定。

注意,因为资源和位值都是和硬件结构紧密相连的,只有在各种Java类中定义的预定义常数值应当被使用在setCLBBits()命令中。

4)输出设计位流

将一个所构造对象的位流写到一个文件中,分为类型JBits.PARTIAL和JBits.FULL。后者返回与读入相同顺序的源位流包,源位流包与被写的位流包之间惟一的不同在于对CLB和BRAM配置的改变;前者可生成在线位流,可以输出全位流或部分位流,取决于JBits对象的状态。

5)获取位

读取一个配置单元中给定资源的配置。