执行单元(EU-Execution Unit):负责指令的译码和执行。

1.4个16位数据寄存器(AX、BX、CX、DX)

AX和AL可用作累加操作,因此又称作累加器

2.4个16位地址指针寄存器:通常用于存放操作数偏移地址

(1) SP (Stack Pointer)—堆栈指针寄存器,指示堆栈段栈顶位置

(2) BP (Base Pointer)—基址指针寄存器,指示堆栈段数据区基址

(3) SI (Source Index)—源变址寄存器,指示数据段源串地址

(4) DI(Destination Index)—目的变址寄存器,指示扩展段目的串地址

3.标志寄存器 FLAG- 状态标志

a) CF(Carry Flag)进(借)位标志,加法运算最高位产生进位或减法运算最高位产生借位,表示无符号数运算产生溢出,CF置1,否则置0

b) AF(Auxiliary Carry Flag)辅助进位标志,加法运算时第3位往第4位有进位,或减法运算时第3位往第4位有借位,则AF置1,否则置0

c) ZF(Zero Flag)零标志, 若当前运算结果为零, 则ZF置1,否则置0

d) SF(Sign Flag)符号标志,与运算结果最高位相同,若为负数,则SF置1,否则置0,SF指示了当前运算结果是正还是负

e) OF(Overflow Flag)溢出标志,有符号数算术运算结果溢出,则OF置1,否则置0

f) PF(Parity Flag)奇偶标志,运算结果低8位所含1个数为偶数则PF置1,否则置0

- 控制标志

a) DF(Direction Flag)方向标志

DF=1,串操作时,地址不断递减;DF=0,串操作时,地址不断递增

b) IF(Interrupt enable Flag)中断允许标志

IF=1,CPU允许接收可屏蔽中断请求,即开中断;IF=0,则关中断

c) TF(Trap Flag)跟踪标志,又称单步标志

TF=1,CPU为单步工作方式,每执行完一条指令产生一次软件中断

总线接口单元(BIU-Bus Interface Unit):与系统总线连接,实现与存储器、I/O口之间的数据传送。

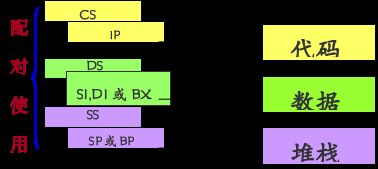

- 4个16位段地址寄存器

a) CS (Code Segment)——代码段寄存器,代码段存放代码

b) DS (Data Segment)——数据段寄存器,数据段存放数据

c) SS (Stack Segment)——堆栈段寄存器,堆栈段用作堆栈操作

d) ES (Extra Segment)——扩展段寄存器,扩展段存放数据

8086对存储器采用分段管理,4个段寄存器分别存放4个当前段的起始地址,又称作段基址寄存器。

2.指令指针寄存器IP (Instruction Pointer)

16位IP存放当前代码段(CS)所要取出的下一条指令的偏移地址

3.地址加法器∑

8086用20位地址线寻址1MB内存空间,但其内部寄存器是16位的,因此需要用地址加法器∑根据16位寄存器的值计算出20位物理地址

4.指令缓冲队列

8086执行指令的同时,会从内存取1条或几条指令,取来的指令就存放在指令队列中

5. 暂存器:用于与EU通信的内部寄存器

6. 总线控制电路:负责总线操作控制

存储器和I/O管理

-

逻辑地址形式为 段地址 : 偏移地址

-

段超越

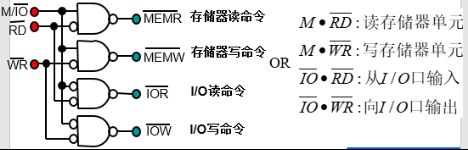

8086 I/O编址

8086对I/O端口操作,需要专门的IN、OUT指令,并且只能通过累加器(AX/AL)来完成,例: IN AL, 80H8086系统中,存储器和I/O端口分别独立编址

存储器的地址范围是00000H – 0FFFFFH

I/O端口的地址范围是0000H – 0FFFFH

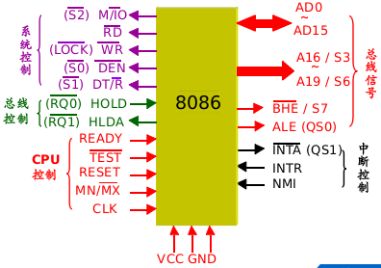

8086引脚信号和工作模式

最小模式:系统中只有一个处理器;MN/MX为高电平

最大模式:系统中包括两个或多个处理器;MN/MX为低电平

8086 CPU为40pin双列直插(DIP)封装。

最小模式下引脚信号和功能

1.总线信号

a) AD0~AD15: 地址/数据复用引脚,双向工作

分时传送16位数据和地址的低16位,由ALE锁存地址信息。

b) A16~A19(S3~S6): 地址/状态复用引脚,输出

分时输出地址的高4位和CPU当前状态,地址信息由ALE锁存。

c) BHE/S7: 高8位数据总线允许/状态复用引脚,输出

低电平有效,表示高8位数据线D15~D8上数据有效

d) ALE: 地址锁存允许信号输出

高电平有效,表示总线上的信息是地址信息。

2.总线控制信号

a) HOLD: 总线保持请求信号输入

高电平有效,表示其他模块(如DMA)申请占用总线

b) HLDA: 总线保持响应信号输出

高电平有效,表示CPU已让出总线

3.系统控制信号

a) M/IO: 存储器/输入输出选择信号,输出,高电平表示CPU访问存储器,低电平表示CPU访问I/O端口

b) RD: 读信号输出,低电平有效,表示CPU从存储器或I/O口读入信息

c) WR: 写信号输出,低电平有效,表示CPU向存储器或I/O口输出数据

d) DT/R: 数据收发信号输出,高电平表示CPU正在发送数据,低电平表示CPU接收数据

e) DEN: 数据允许信号输出,低电平有效,表示CPU当前准备发送或接收一个数据

4.中断控制信号

a) INTR: 可屏蔽中断请求信号输入,高电平有效,表示外部向CPU提出中断申请

b) INTA: 中断响应信号输出,低电平有效,表示CPU响应外设中断请求

c) NMI: 非屏蔽中断请求信号输入,上升沿有效。表示外部有非屏蔽中断申请。非屏蔽中断不受软件控制,CPU必须响应

5.CPU控制信号

a) RESET: 复位信号输入

高电平有效,至少保持4个时钟周期的高电平。复位时CPU停止现行操作,开始复位,并进行初始化:标志寄存器FLAG、IP、DS、SS、ES及指令队列均清零,CS为FFFFH,复位结束时CPU从FFFF0H开始执行程序;

b) MN/MX:最小模式/最大模式选择信号输入,高电平为最小模式

c) READY:“准备好”信号输入,高电平有效,表示存储器或I/O口已准备就绪,可进行一次数据传输;

d) TEST: 测试信号输入,低电平有效,有效时CPU退出WAIT指令;

6.其它信号

a) CLK: 时钟信号,8086主频为4.77MHZ T=210ns;单相,占空比为1/3。

b) VCC,GND: 电源及地,+5V,满足TTL规范

8086最小模式下的总线连接

1. Intel 8282

把AD复用引脚连接到地址总线的8位地址锁存器。3片8282(功能同74LS373)A0~A19和BHE,ALE为锁存信号。

2. Intel 8286

把AD复用引脚连接到数据总线的8位数据缓冲器。2片8286(功能同74LS245)做D15~D0的缓冲器,DT/R做方向选择,DEN为选通信号。

4. 中断控制信号INTR、INTA、NMI

INTR: 外部可屏蔽中断请求引脚,高电平有效

INTA: 中断响应信号,低电平有效

NMI: 不可屏蔽中断请求引脚,上升沿有效

5. 总线控制信号HOLD、HLDA

HOLD:总线保持请求引脚,高电平有效

HLDA:总线保持响应引脚,高电平有效

HLDA控制8282的OE,当CPU总线保持响应时让出总线

8086操作和时序

1. 8086时钟电路与复位电路

8284为8086提供CLK时钟信号、 RESET复位信号和READY准备好信号

8086/8088内部无时钟发生器,时钟由8284提供,频率为4.77MHz

输入RES经8284内部斯密特触发器整形,同步后产生RESET信号,给CPU复位

外界准备好信号输入到8284的RDY端,同步后产生READY信号给CPU

2. 8086/8088系统的复位操作和启动过程

CPU接到RESET信号,停止现有工作,进行复位操作:CS置FFFFH,IP置0,指令队列清空,其余寄存器清0;

从存储器FFFFH :0000H取第一条指令,一般在此处放一条跳转指令,跳转到ROM BIOS中的系统测试程序

系统测试程序执行硬件自检(对CPU、RAM、ROM等硬件进行测试),然后执行ROM BIOS中的初始引导程序

初始引导程序再从磁盘0面0道1扇区装入引导程序,执行引导操作

按引导程序的指令,顺序装入其他程序模块,完成操作系统的引导操作

注:在3、4步之间微机还会检查C0000H开始的扩展ROM空间中是否有程序,如果有,并且校验正确,则先执行这些程序

3. 8086总线周期

时钟周期T(T状态)

时钟脉冲的一个循环时间叫做一个时钟周期。每个时钟周期T又称为一个“状态”。它是CPU工作的最小时间单位,是计算机系统工作速度的重要标志。8086 CPU的F=4.77M,T=210ns总线周期

CPU通过总线从存储器或I/O端口存取一个字或字节的时间称为总线周期。包括三类:存储器读写周期、I/O端口读写周期、中断响应周期

一个基本总线周期包括4个状态:T1,T2,T3,T4指令周期

执行一条指令所需要的时间称为指令周期。8086指令周期最短为2个时钟周期,最长为200个时钟周期。

4. 8086总线操作时序(最小模式下存储器读周期)

T1状态

置M/IO为高电平,指示是从存储器读数据

T1开始,ALE置高,8282输出跟随输入,T1上升沿,ALE置低,8282锁存20位地址

BHE也在T1状态锁存,指示T2、T3状态传送数据时,高8位是否有效

置DT/R为低,控制8286接收数据,置DEN为高,让8286输出浮空T2状态

撤销地址信号,AD15~AD0处于高阻状态,为读入数据作准备

A19/S6~A16/S3及BHE/S7引脚输出状态信息S6~S3

置RD信号为低电平,输出读信号到存储器

置DEN为低电平,打开8286三态门,准备接收存储器输出的数据T3状态

存储器将数据送到数据总线,CPU通过AD15~AD0接收数据

T3上升沿检测READY信号,若为高电平,则下一个为T4状态;否则插入等待周期TwT4状态

T4开始,撤销RD和DEN信号,置为高电平无效,数据总线浮空

T4上升沿撤销DT/R信号

CPU读取存储器数据的时间为 2T = 420ns (RD或DEN有效时间)

注:最小模式下I/O口读周期与存储器读周期类似,区别为读I/O口时,T1状态将置M/IO为低电平,表示是对I/O口进行读