恩智浦的i.MX RT600是跨界处理器产品,同样也是i.MX RTxxx系列的开山之作。不同于i.MX RT1xxx系列单片机,i.MX RT600 采用了双核架构,将新一代Cortex-M33内核与高性能Cadence Tensilica HiFi 4 音频DSP内核相结合,适用于32位沉浸式音频播放和视频用户界面应用。i.MX RT600旨在通过安全、功率优化的嵌入式处理器充分挖掘语音辅助终端节点的潜力,因此针对音频数据的采集、传输和处理,i.MX RT600都有丰富的硬件资源进行支持。其中,针对RT600的DMIC外设,本文详细地进行了介绍,并基于i.MX RT600 EVK开发板,在RT600的DSP端(HiFi4)实现了一个8通道音频数据采集的demo。

一、DMIC介绍

1.1 DMIC 接口

DMIC接口也称双/立体声数字麦克风接口。i.MX RT600提供了最多8通道的PDM(脉冲密度调制)数字接口,共8根引脚,其中4根时钟引脚为PDM接口的数字麦克风提供时钟参考,4根数字引脚能够从PDM接口的数字麦克风上采集数据。每个PDM接口都支持两个单通道麦克风或单个立体声麦克风的连接选项,下图给出了本次应用中采用的8通道DMIC多路复用连接方式作为参考。

1.2 RT600 DMIC硬件架构

i.MX RT600总共包含8个DMIC通道,可以从多路的数字麦克风设备采集PDM数据,经过内部一系列处理后,就可以得到16bits或24bits的PCM数据,并支持CPU或DMA直接访问。每个DMIC通道的内部框图如下所示。

从DMIC内部通道的框图可以看出,PDM数据到PCM转换的滤波过程包括四个阶段。

第一阶段,从CIC滤波器开始,它是结合了抽取器的FIR滤波器。 CIC滤波器以给定的过采样率将来自数字麦克风的PDM数据转换为PCM数据,该采样率可以被OSR寄存器配置。

第二阶段,PCM数据由半带抽取滤波器处理后频率降为原来的一半,同时经过这一阶段后,补偿了音频带上限的滚降。

第三阶段,同第二阶段一样,PCM数据经过一个半带抽取滤波器处理,频率降为原来的一半。

第四阶段,DC滤波器用于消除了音频信号中任何不需要的直流分量。

另外,为了实现更低的功耗,将Use 2FS register寄存器中的USE2FS位置1可以绕过第二个半带抽取滤波器,并为DC滤波器提供2FS而不是1FS信号。当通过CPU或DMA从FIFO中读取PCM数据时,其位宽可以是16bit和24bit,这可以通过配置DCCTRL寄存器的SATURATEAT16BIT和SIGNEXTEND位来控制。

1.3 DMIC时钟和采样频率计算

DMIC采样频率取决于三个方面:

1)DMIC接口基础时钟。

DMIC接口的基础时钟为整个DMIC外设提供一个参考时钟,可以通过寄存器CLKCTL1 DMIC0CLKSEL和寄存器DMIC0CLKDIV进行配置。 DMIC外设的可选时钟源如下图所示,包括SFRO,FFRO,audio_pll_clk, mclk_in,1m_lposc和32k_wake_clk。

2)提供给数字麦克风设备的DMIC采样时钟。

这里的DMIC采样时钟用于提供给连接在DMIC外设上的数字麦克风设备一个PDM基准采样频率。当然这个频率的范围是有限制的,最高不超过6.144MHz,这就导致DMIC的基础时钟的频率不应超过24.576MHz。

3)PCM采样频率。

由上面的DMIC通道内部框图可知,从DMIC采集得到PDM数据,再经过一些列滤波器处理后,最终得到的PCM数据的频率是降低的。它们之间的关系如下:

PCM采样频率= DMIC采样时钟频率 /(N * OSR),其中2 FS模式时,N = 2; 1 FS模式,N = 1)

以本文介绍的demo配置为例,DMIC采样时钟频率配置为3.072MHz,DMIC通道配置为2 FS模式(N=2),OSR设置为32,那么可以得到:

PCM采样频率 = DMIC采样时钟频率 / (N * OSR) = 3.072MHz / (2 * 32) = 48KHz

该频率正是本次应用中DMIC外设得到的PCM数据的采样频率。

1.4 FIFO和DMA支持

DMIC FIFO中PCM数据的有效宽度可以是16位或24位,DMIC提供了两种访问FIFO数据的方式:CPU或DMA直接访问。通过配置FIFO的触发级别,选择中断或DMA的方式,就可以将PCM数据从FIFO复制到SRAM。下图显示了通过DMA复制DMIC FIFO数据的过程。

二、应用

2.1 系统架构

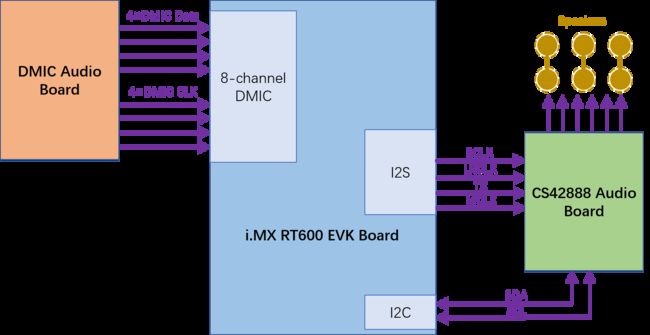

在此应用中,8通道DMIC音频数据采集的整个架构如图所示。HiFi4控制8通道DMIC接口从DMIC音频板接收PDM数据,CS42888编解码器通过I2S接口接收HIFI4处理过后的PCM数据,并将其传输到扬声器进行实时播放。

2.2 CS42888 Codec介绍

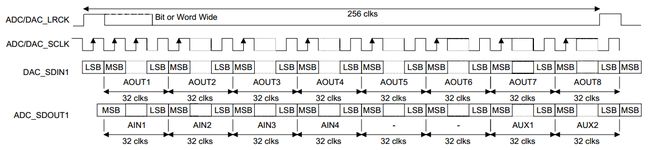

CS42888是高度集成的24位音频编解码器,包含具备delta-sigma技术的4个模数转换器(ADC)和8个数模转换器(DAC),8个DAC通道均提供数字音量控制,并可以使用差分或单端输出进行操作。 CS42888的DAC串行端口支持I2S TDM音频数字接口格式,位深度从16到24不等,并允许时分复用(TDM)接口格式的DAC通道多达8个。CS42888支持的TDM时序图如图7所示。

在DAC_LRCK上升沿之后的第二个DAC_SCLK上升沿,首先接收TDM数据的最高有效位(MSB)。 所有数据在DAC_SCLK的上升沿有效,在DAC_SCLK的下降沿发送。从图中可以注意到, CS42888在TDM模式下要求每一通道的PCM数据占32个时钟周期,也就是32bit的位宽,并且DAC_SCLK必须是PCM数据采样频率的8倍。因此在配置I2S的时候需要遵从这几个注意事项。

2.3 DMIC配置

DMIC的采样频率与1.3小节中的举例一致,并为了得到48kHz的PCM采样频率,需要进行如下配置:

- DMIC时钟源:audio_pll_clk

- DMIC外围输入时钟:24.576MHz

- DMIC时钟分频器:8

- DMIC时钟频率:3.072MHz

- OSR寄存器:32

- FS模式:2FS

- DMIC采样位宽:16bit

因此,DMIC PCM采样率 = DMIC采样时钟频率 / (N * OSR) = 3.072MHz / 2 / 32 = 48kHz

以下代码给出了每一路DMIC通道的具体配置:

/* dmic channel configurations */

static dmic_channel_config_t s_dmicChannelConfig = {

.divhfclk = kDMIC_PdmDiv1,

.osr = 32U,

.gainshft = 3U,

.preac2coef = kDMIC_CompValueZero,

.preac4coef = kDMIC_CompValueZero,

.dc_cut_level = kDMIC_DcCut155,

.post_dc_gain_reduce = 1U,

.saturate16bit = 1U,

.sample_rate = kDMIC_PhyFullSpeed,

.enableSignExtend = false,

};2.4 Flexcomm配置

i.MXRT600上最多提供8个多功能Flexcomm接口。 在此应用程序中,Flexcomm2被配置为I2C接口。CS42888提供了标准的I2C控制接口,并支持所有功能的软件配置。因此,HiFi4利用I2C对CS42888进行初始化,配置为TDM工作模式。CS42888作为I2C从设备,读写命令的操作时序如图所示。

Flexcomm4接口在本应用中配置为I2S接口,用于传输DMIC采集的8通道PCM数据。DMIC采集的PCM数据的采样频率为48kHz,I2S采样频率需保持一致。下面是I2S采样频率的配置参数:

- I2S时钟源:audio_pll_clk

- I2S时钟源频率:24.576MHz

MCLK频率:12.288MHz

- I2S传输模式:TDM

- I2S声道数:8

- I2S声道位宽:32bit

- I2S BCLK = WS * 声道数 * 声道位宽 = 48KHz * 8 * 32 = 12.288MHz

I2S_DIV (I2S分频系数) = audio_pll_clk / BCLK = 24.576MHz / 12.288MHz = 2

2.5 DMA和中断配置

在RT600上做音频数据的处理推荐用DMA,从而减少对CPU资源的消耗。DMA在RT600上推荐的用法是CM33核使用DMA0,而HiFi4使用DMA1。此外,在HiFi4中使用DMA与在CM33端是有一定区别的,这个主要体现在以下几点:

- 需要在XOS或XTOS中注册并启用HiFi4中断。

- 在HiFi4中DMA操作的SRAM地址必须是non-cacheable。

- 需要由使用INPUTMUX注册HiFi4中断。

这些注册的中断与HiFi4的连接关系如下表所示。表中除了提供所需的中断选择之外,还显示了各个中断的中断优先级。L1中断的优先级最低,而L3中断的优先级最高。

以下代码给出了HiFi4 DMA和中断的具体配置:

#define XCHAL_EXTINT19_NUM 23 /* (intlevel 2) */

DMA_Init(DMA1);

/* XCHAL_EXTINT19_NUM, intlevel 2 */

INPUTMUX_AttachSignal(INPUTMUX, 18U, kINPUTMUX_Dmac1ToDspInterrupt);

xos_register_interrupt_handler(XCHAL_EXTINT19_NUM,

(XosIntFunc *) DMA_IRQHandle,

DMA1);

xos_interrupt_enable(XCHAL_EXTINT19_NUM); 2.6 音频数据流的处理

为了能够将8通道DMIC采集的音频数据发送到CS42888音频板并播放,根据CS42888数据手册,我们需要将CS42888配置成TDM模式。在TDM模式下,CS42888接收的PCM数据位宽必须是32bit,其有效数据范围可以是16位到24位。为此,本应用中我们需要软件程序将DMIC采集到的16bit位宽的PCM数据处理为32bit位宽,下面我们就介绍该方法。

首先,DMIC采集到的每一通道的PCM数据都利用了ping-pang buffer的形式放在对应的缓冲区,而RT600的DMA支持了最多4通道DMIC的数据搬移。因此,采用DMA memory to memory的功能,我们可以把DMIC的4通道PCM数据搬到一个固定的缓冲区(假设为BUFFER1),但是这个BUFFER1中4通道的PCM数据是有固定间隔的,间隔的大小为48bit。有的小伙伴或许这里有疑惑了,为什么间隔的大小是48bit,而不是32或16bit呢?我们接下来慢慢分析。

正是由于DMIC和DMA外设的限制,导致DMA一次只能搬运4通道16bit的PCM数据,假如BUFFER0没有被操作的内存地址已经初始化为0x00,那么我们就可以把那些内存地址上为0x00的地址与PCM数据拼凑成32bit的PCM数据,PCM数据的有效位依旧是16bit,满足CS42888的要求。PCM数据间隔大小为48bit是针对16bit的PCM数据,那针对于32bit的PCM数据来说,这4通道的PCM数据在BUFFER1上的间隔就是32Bbit。

看到这里相信读者已经明白了8通道的PCM数据该怎么处理了,没错,只需要另外再开启1路DMA,还是采用DMA memory to memory的功能,就可以将另外DMIC的4通道PCM数据搬移到BUFFER1内存空间上那些间隔出来的32bit位宽的地址上。

整个DMIC采集的8通道PCM数据后续软件过程如下图所示。

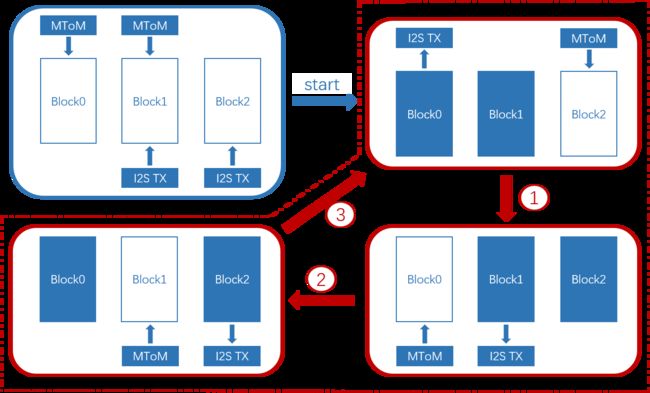

接下来,HiFi4控制一路I2S将处理成TDM格式的PCM数据传输到CS42888编解码器。为了能够流畅地播放音频流数据,与RT600之I2S外设介绍及应用中介绍的处理方法一样,笔者采用了如下图所示的方法。图中,总共3个缓冲区用于处理PCM数据,这3个缓冲区构成一个闭环。每个缓冲区为1024字节,包含32帧PCM数据,每一帧包含8包32bit的PCM数据。 每当一个缓冲区中的PCM数据接收满时,下一个缓冲区将立即开始接收,发送也同理。因为本次应用中需要处理的PCM数据有8路,数据量比较大,因此采用ring buffer的机制能够保证数据传输的稳定和可靠。

三、RT600 硬件演示平台搭建

8通道DMIC音频数据采集demo基于i.MX RT600 EVK RevE板子实现,整个硬件平台包括3部分:DMIC音频采集板,CS42888音频板和i.MX RT600 EVK板,如下图所示。

为了演示该demo,需要注意以下几点:

DMIC音频采集板与RT600 EVK板的J31连接。

CS42888音频板与RT600 EVK板进行连接,连接情况如表所示:

CS42888 audio board RT600 EVK board A4 PIN J26 PIN1 (GND) A5 PIN J27 PIN3 (BCLK) A6 PIN J27 PIN2 (WS) A8 PIN J27 PIN1 (TX) A9 PIN J29 PIN4 (3V3) A11 PIN J28 PIN1 (RESET) A13 PIN J29 PIN8 (5V) A16 PIN JS2 PIN1 (1V8) B5 PIN J28 PIN10 (SCL) B6 PIN J28 PIN9 (SDA) B12 PIN J27 PIN6 (MCLK) 音频扬声器插入CS42888音频板的J11,J12,J13,J14,J15和J16端口。

对RT600 EVK板进行改动:

- 去掉R379-A,R380-A,R384-A,R389-A,R390-A,R391-A,R392-A,R393-A这些电阻。

- 用0欧姆电阻焊接R379-B,R380-B,R384-B,R389-B,R390-B,R391-B,R392-B,R393-B这些位置。

至此,RT600之DMIC外设介绍完毕。