可编程中断控制器PIC

x86体系架构包含一个可编程的中断控制器PIC(Programmable Interrupt Controller),用于收集外部中断并将其发送给CPU。外部设备不能直接和CPU链接^ ^_

intel体系结构的PIC通常包含两种:8259,以及最新的APIC(Advanced PIC)。

8259芯片(重点)

简介

8259芯片由IBM公司开发,用于接受外部设备(如键盘)的中断请求并将其发送给CPU。

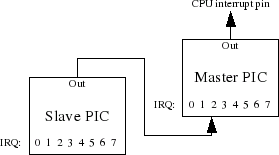

起初,只有一个8259芯片,能向CPU提供8种中断请求。后来,通过将另一块8259芯片与其相连,则能提供总共15种中断请求。

其结构如下图所示:

PIC与CPU交互

PIC作为可编程的硬件,我们可以通过CPU执行相关指令来对其进行操作。

每个8259芯片都有一个命令端口和数据端口,具体如下:

| 端口名称 | IO端口号 |

|---|---|

| Master 命令 | 0x20 |

| Master 数据 | 0x21 |

| Slave 命令 | 0xA0 |

| Slave 数据 | 0xA1 |

APIC(简介)

Advanced PIC,常见于现代多核心CPU。、其实从P5开始就已经有APIC了,虽然当时并为内嵌进CPU中。相对8259,APIC有很多优势,将来有时间再做详细介绍。

为什么不详细介绍?

我们现在常见的PC,以及模拟器其实都是有APIC的。之所以不详细介绍APIC是因为市面上很多将操作系统的教材都只是在介绍8286,对APIC设计不多,考虑到学习曲线,故只做简单介绍。

如果我有时间完成支持多核的操作系统,我会再详细地介绍APIC。

架构简介

APIC包含了LAPIC(Local APIC)、和I/O APIC。每个CPU都内嵌一个LAPIC,

关闭APIC

我们的项目中选择使用遗留的8259,因此我们选择关闭APIC。

从Intel开发手册卷三可知:关闭APIC有两种方式。这里只简单介绍一种:通过MSR来关闭apic。

MSR寄存器的第11位表示了APIC是否开启。

因为通过这么久的联系,自己对汇编也算相对收悉了,所以部分代码采用汇编编写。

static void disable_local_apic(){

uint32_t eax;

uint32_t edx;

cpuid(1, &eax, &edx);

if (edx & CPUID_FLAG_APIC ){

printf("Deteced APIC, will disable it.\n");

if (edx & CPUID_FLAG_MSR){

_shutdown_apic();

printf("Disabled\n");

} else {

printf("No MSR detected!\n");

}

}

}

代码会首先检查是否有APIC和MSR寄存器,然后调用_shutdown_apic将apic关闭。

.global _shutdown_apic

.type _shutdown_apic, @function

_shutdown_apic:

movl $0x1b, %ecx

rdmsr

andl $0xFFFFF7FF, %eax

wrmsr

ret

其中MSR的地址为0x1b。

问题

我在阅读资料的时候,产生了一些小问题,怕将来产生同样的困惑故稍作记录。

- 如何检测一个8259芯片是否有slave芯片?

虽然不知道如何检测是否有slave芯片,但是除了特别特别早期的CPU,8259芯片都有slave芯片。

- 如何检测是否有8259芯片?

虽然不知道如何检测,但是常见的IBM-PC兼容机都有8259芯片。

- APIC能与8259共存与一个芯片吗?

可以并且使用APIC之前需要禁用8259。

接下来的内容,我们将进行如下假设:我们的硬件满足通用的IBM-PC兼容机中断

PIC(8259A)相关编程实现

重置PIC映射关系

启动时,BIOS程序默认将8259的中断映射为如下表所示关系:

| 芯片 | 中断号(in 8259) | CPU接收到的中断号 |

|---|---|---|

| Master | 0~7 | 8~15 |

| Slave | 8~15 | 112~119 |

从上表中可以看出,由于IBM的设计失误,8259Master芯片的默认映射的中断号8~15与intel保留的中断号相冲突。因此,我们必须对其进行重新配置。

具体的硬件细节不做过多介绍,可以参看代码(后期会开源)。下述代码将IRQ015映射到3247。

/* reinitialize the PIC controllers, giving them specified vector offsets

rather than 8h and 70h, as configured by default */

#define ICW1_ICW4 0x01 /* ICW4 (not) needed */

#define ICW1_SINGLE 0x02 /* Single (cascade) mode */

#define ICW1_INTERVAL4 0x04 /* Call address interval 4 (8) */

#define ICW1_LEVEL 0x08 /* Level triggered (edge) mode */

#define ICW1_INIT 0x10 /* Initialization - required! */

#define ICW4_8086 0x01 /* 8086/88 (MCS-80/85) mode */

#define ICW4_AUTO 0x02 /* Auto (normal) EOI */

#define ICW4_BUF_SLAVE 0x08 /* Buffered mode/slave */

#define ICW4_BUF_MASTER 0x0C /* Buffered mode/master */

#define ICW4_SFNM 0x10 /* Special fully nested (not) */

static void remap_pic(){

//reinitialize pic

outb(PIC1_COMMAND, ICW1_INIT+ICW1_ICW4); //starts the initialization sequence (in cascade mode)

io_wait(); //on older machines its necessary to give the PIC some time to react to commands as they might not be processed quickly

outb(PIC2_COMMAND, ICW1_INIT+ICW1_ICW4);

io_wait();

outb(PIC1_DATA, ICW2_PIC1); //ICW2: Master PIC vector offset

io_wait();

outb(PIC2_DATA, ICW2_PIC2); //ICW2: Slave PIC vector offset

io_wait();

outb(PIC1_DATA, 4); //ICW3: tell Master PIC that there is a slave PIC at IRQ2 (0000 0100)

io_wait();

outb(PIC2_DATA, 2); //ICW3: tell Slave PIC its cascade identity (0000 0010)

io_wait();

outb(PIC1_DATA, ICW4_8086);

io_wait();

outb(PIC2_DATA, ICW4_8086);

io_wait();

//Enable all

outb(PIC1_DATA, 0);

outb(PIC2_DATA, 0);

}

添加相应的中断处理程序

和之前处理IDT一样,我们同样采用两段式的中断处理程序。但是和通用的中断处理程序不一样的是:必须通知PIC,我们已经完成了对其中断的处理,它可以进行下一轮的中断请求。

汇编层“接收”中断

提供如下汇编代码作为参考:注意!在我的实现中,我用err_code来保存PIC的IRQ号,而int_num保存的是IRQ映射的中断号

.macro IRQ irq_num,idt_num

.global irq\irq_num

.type irq\irq_num, @function

irq\irq_num:

cli

pushl $\irq_num

pushl $\idt_num

jmp irq_comman_stub

.endm

IRQ 0, 32

IRQ 1, 33

...

IRQ 15, 47

上诉代码中的irq_comman_stub和上一篇博客内的isr_comman_stub除了调用irq_handler之外,其它一致。

处理中断,通知PIC

我们的操作系统,在接收到IRQ之后,应该通知PIC它可以处理下一个中断。需要注意的是,如果IRQ由slave芯片发出,那么我们必须对两块芯片都进行通知:

#define PIC_EOI 0x20

//Send EOI to PIC

if (regs->err_code >= 8){ //Also send EOI to slave chip

outb(PIC2_COMMAND,PIC_EOI);

}

outb(PIC1_COMMAND,PIC_EOI);

其它逻辑

参考源码或者上一篇介绍IDT的文章。

PIC示例:接收时钟中断

PIT,Programmable Interval Timer,是连接在8259的第0号输入针脚(即IRQ0)的定时器。可用于以指定的时间间隔想CPU产生中断。

因为没有什么复杂的知识,在此不做过多介绍。可以直接参看以下代码:

void init_timer(uint32_t frequency){

//Regiser timer callback

register_i_handler(IRQ0, timer_callback);

// The value we send to the PIT is the value to divide it's input clock

// (1193180 Hz) by, to get our required frequency. Important to note is

// that the divisor must be small enough to fit into 16-bits.

uint32_t divisor = 1193180 / frequency;

// Send command type

outb(0x43, 0x36);

//Divisor has to be sent byte-wise, so split here into upper/lower bytes.

uint8_t l = (uint8_t)(divisor & 0xFF);

uint8_t h = (uint8_t)((divisor >> 8) & 0xff);

// Send the frequency divisor.

outb(0x40, l);

outb(0x40, h);

}

static uint32_t count = 0;

void timer_callback(registers_t *regs){

printf("Tick: %d\n", count++);

}

VWware 运行截图

从现在开始,我将在VWware Fusion上运行玩具系统。

可能会遇到的问题:接收不到8259中断?

确定启用了中断(

sti),并且能通过软中断的方式确认IDT能正常工作。

参考资料

- http://jamesmolloy.co.uk/tutorial_html/5.-IRQs%20and%20the%20PIT.html

- http://wiki.osdev.org/PIC

- http://wiki.osdev.org/APIC

- http://wiki.osdev.org/IOAPIC

- http://wiki.osdev.org/Interrupts#General_IBM-PC_Compatible_Interrupt_Information

- http://wiki.osdev.org/Inline_Assembly

- http://wiki.osdev.org/Inline_Assembly/Examples

- http://wiki.osdev.org/Model_Specific_Registers

- http://wiki.osdev.org/CPUID

- http://forum.osdev.org/viewtopic.php?t=11998

- http://www.jaist.ac.jp/iscenter-new/mpc/altix/altixdata/opt/intel/vtune/doc/users_guide/mergedProjects/analyzer_ec/mergedProjects/reference_olh/mergedProjects/instructions/instruct32_hh/vc273.htm

- http://ethv.net/workshops/osdev/notes/notes-3

- http://www.intel.cn/content/www/cn/zh/processors/architectures-software-developer-manuals.html