晶振及其内部电路详解:

晶振及其内部电路详解:

晶振原理:晶振,在电气上它可以等效成一个电容和一个电阻并联再串联一个电容的二端网络,电工学上这个网络有两个谐振点,以频率的高低分其中较低 的频率是串联谐振,较高的频率是并联谐振。由于晶体自身的特性致使这两个频率的距离相当的接近,在这个极窄的频率范围内,晶振等效为一个电感,所以只要晶振的两端并联上合适的电容它就会组成并联谐振电路。这个并联谐振电路加到一个负反馈电路中就可以构成正弦波振荡电路,由于晶振等效为电感的频率范围很窄, 所以即使其他元件的参数变化很大,这个振荡器的频率也不会有很大的变化。

晶振有一个重要的参数,那就是负载电容值,选择与负载电容值相等的并联电容,就可以得到晶振标称的谐振频率。

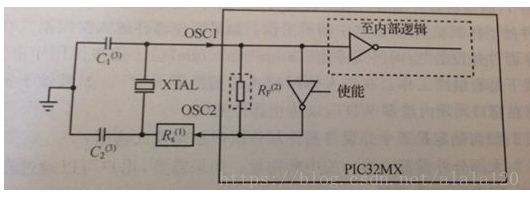

一般的晶振振荡电路都是在一个反相放大器(注意是放大器不是反相器)的两端接入晶振,再有两个电容分别接到晶振的两端,每个电容的另一端再接到地,这两个电容串联的容量值就应该等于负载电容,请注意一般IC的引脚都有等效输入电容,这个不能忽略。

一般的晶振的负载电容为15p或12.5p ,如果再考虑元件引脚的等效输入电容,则两个22p的电容构成晶振的振荡电路就是比较好的选择。 负载电容+等效输入电容=22pF

无源晶振 有源晶振:

晶振是为电路提供频率基准的元器件,通常分成有源晶振和无源晶振两个大类,无源晶振需要芯片内部有振荡器,并且晶振的信号电压根据起振电路而定,允许不同的电压,但无源晶振通常信号质量和精度较差,需要精确匹配外围电路(电感、电容、电阻等),如需更换晶振时要同时更换外围的电路。有源晶振不需要芯片的内部振荡器,可以提供高精度的频率基准,信号质量也较无源晶振要好。

晶振起振原理:

石英晶片所以能做振荡电路(谐振)是基于它的压电效应,从物理学中知道,若在晶片的两个极板间加一电场,会使晶体产生机械变形;反之,若在极板间施加机械力,又会在相应的方向上产生电场,这种现象称为压电效应。如在极板间所加的是交变电压,就会产生机械变形振动,同时机械变形振动又会产生交变电场。一般来说,这种机械振动的振幅是比较小的,其振动频率则是很稳定的。但当外加交变电压的频率与晶片的固有频率(决定于晶片的尺寸)相等时,机械振动的幅度将急剧增加,这种现象称为压电谐振,因此石英晶体又称为石英晶体谐振器。 其特点是频率稳定度很高。

石英晶体振荡器与石英晶体谐振器都是提供稳定电路频率的一种电子器件。石英晶体振荡器是利用石英晶体的压电效应来起振,而石英晶体谐振器是利用石英晶体和内置IC来共同作用来工作的。振荡器直接应用于电路中,谐振器工作时一般需要提供3.3V电压来维持工作。振荡器比谐振器多了一个重要技术参数为:谐振电阻(RR),谐振器没有电阻要求。RR的大小直接影响电路的性能,也是各商家竞争的一个重要参数。

可能有些初学者会对晶振的频率感到奇怪,12M、24M之类的晶振较好理解,选用如11.0592MHZ的晶振给人一种奇怪的感觉,这个问题解释起来比较麻烦,如果初学者在练习串口编程的时候就会对此有所理解,这种晶振主要是可以方便和精确的设计串口或其它异步通讯时的波特率。

问: 我发现在使用晶振时会和它并一个电阻,一般1M以上,我把它去掉,板子仍可正常工作,请问这个电阻有什么用?可以不用吗? 我有看到过不用的!不理解

答: 这个电阻是反馈电阻,是为了保证反相器输入端的工作点电压在VDD/2,这样在振荡信号反馈在输入端时,能保证反相器工作在适当的工作区。虽然你去掉该电 阻时,振荡电路仍工作了。但是如果从示波器看振荡波形就会不一致了,而且可能会造成振荡电路因工作点不合适而停振。所以千万不要省略此电阻。 这个电阻是为了使本来为逻辑反相器的器件工作在线性区, 以获得增益, 在饱和区是没有增益的, 而没有增益是无法振荡的. 如果用芯片中的反相器来作振荡, 必须外接这个电阻, 对于CMOS而言可以是1M以上, 对于TTL则比较复杂, 视不同类型(S,LS...)而定. 如果是芯片指定的晶振引脚, 如在某些微处理器中, 常常可以不加, 因为芯片内部已经制作了, 要仔细阅读DATA SHEET的有关说明.和晶振并联的电阻作为负载,一般1M欧。也有和晶振串联的电阻为谐振电阻。

晶振的参数里有配用的谐振电容值。比如说32.768K的是12.5pF;4.096M的是20pF. 这个值和实际电路中晶振上接的两个电容值是什么关系?像DS1302用的就是32.768K的晶振,它内部的电容是6pF的

答: 你所说的是晶振的负载电容值。指的是晶振交流电路中,参与振荡的,与晶振串联或并联的电容值。晶振电路的频率主要由晶振决定,但既然负载电容参与振荡,必 然会对频率起微调作用的。负载电容越小,振荡电路频率就会越高,4.096MHz的负载电容为20pF,说明晶振本身的谐振频率<4.096MHz, 但如果让20pF的电容参与振荡,频率就会升高为4.096MHz。或许有人会问为什么这么麻烦,不如将晶振直接做成4.096MHz而不用负载电容?不是没有这样的晶振,但实际电路设计中有多种振荡形式,为了振荡反馈信号的相移等原因,也有为了频率偏差便于调整等原因,大都电路中均有电容参与。

PLL:PLL是Phase-Locked Loop的缩写,中文含意为锁相环。PLL基本上是一个闭环的反馈控制系统,它可以使PLL的输出可以与一个参考信号保持固定的相位关系。PLL一般由鉴相器、电荷放大器(Charge Pump)、低通滤波器、压控振荡器、以及某种形式的输出转换器组成。为了使得PLL的输出频率是参考时钟的倍数关系,在PLL的反馈路径或(和)参考信号路径上还可以放置分频器。

压控振荡器产生周期性的输出信号,如果其输出频率低于参考信号的频率,鉴相器通过电荷放大器改变控制电压使压控振荡器就的输出频率提高。如果压控振荡器的输出频率高于参考信号的频率,鉴相器通过电荷放大器改变控制电压使压控振荡器就的输出频率降低。低通滤波器的作用是平滑电荷放大器的输出,这样在鉴相器进行微小调整的时候,系统趋向一个稳态。