亚稳态专题(亚稳态的概念、亚稳态的产生、亚稳态的后果、以及如何避免亚稳态)

亚稳态是FPGA系统中的一个常见问题,亚稳态的出现轻则导致输出错误,严重的甚至会导致系统崩溃。因此对亚稳态的了解必不可少,本文在查阅众多资料的基础上,对亚稳态的概念、亚稳态的产生原因、以及如何避免亚稳态进行了分析与记录。

目录

一、概念

1、建立时间与保持时间

2、恢复时间与去除时间

3、亚稳态

二、产生与消除

1、跨时钟域信号传输

2、异步信号采集

3、异步复位电路

三、亚稳态概率分析

1、亚稳态产生概率:

2、多级触发器减少亚稳态

四、避免

五、参考文献

一、概念

1、建立时间与保持时间

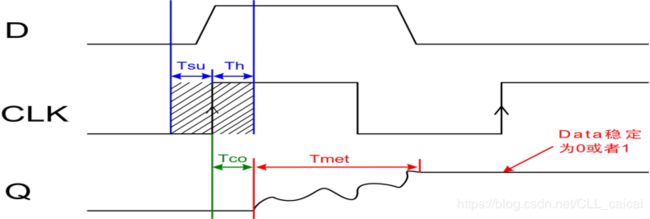

触发器在时钟上升沿来临时对数据进行采样,产生对应的输出。但是实际器件无法瞬时完成数据采样这一过程,需要数据在时钟沿前后均稳定一定时间,即引入了(触发器的)建立时间与保持时间这一概念。

建立时间Tsu:时钟有效沿到来之前数据必须保持稳定的最小时间;

保持时间Th:时钟有效沿到来之后数据必须保持稳定的最小时间;

2、恢复时间与去除时间

恢复时间(Recovery time):与同步电路中的建立时间类似,是指异步控制信号(如寄存器的异步清除和置位控制信号)在“下个时钟沿”来临之前变无效的最小时间长度。这个时间的意义是,异步控制信号在时钟上升沿来临Trecovery时间就要保持稳定,如果保证不了这个最小恢复时间,也就是说“下个时钟沿”来临时,这个异步控制信号不能保证正常执行。

去除时间(Removal time):与同步电路中的保持时间类似,是指异步控制信号(如寄存器的异步清除和置位控制信号)在“有效时钟沿”之后变无效的最小时间长度。这个时间的意义是,异步控制信号在时钟上升沿后仍需保持Tremoval的稳定时间,如果保证不了这个去除时间,也就是说这个异步控制信号的解除与“有效时钟沿”离得太近,那么依旧不能保证这一异步控制信号能正常执行。

3、亚稳态

概念:

亚稳态是指触发器无法在某个规定的时间段内到达一个可以确认的状态。即:如果触发器的输入电压采样时间过短,则触发器需要花很长时间来实现输出逻辑达到标准电平,在这段时间里输出端在高低电平之间处于振荡状态,而不是等于理想输出值。也就是说,电路处于中间态的时间变长,使得电路“反应”迟钝,这就是“亚稳态”。(例如输入信号在时钟有效沿的建立时间和保持时间之间改变了,导致不满足触发器的建立时间或保持时间,导致输出有一段时间的不稳定态,就是亚稳态。)

后果:

1、亚稳态中间态时间变长:亚稳态是触发器的一个固有特性,正常采样也会有一个亚稳态时间。当建立时间和保持时间满足时,触发器也会经历采样---亚稳态---随后稳定输出。而出现亚稳态问题时,亚稳态(中间态)时间变长

2、亚稳态的输出不一定正确:正常工作时,触发器经历较短的亚稳态时间,随后会正确输出;而出现亚稳态问题时,触发器经历较长的亚稳态时间,最终输出稳定但无法保证正确(是稳定的标准电平信号,但难以保证是输入对应输出);

物理意义:

数字电路中,对于电平小于电压阈值 VL的称为0,大于电压阈值VL 称之为1,而电平位于电压阈值之间时(无法确定电压为0还是1)叫做系统的亚稳态。

工程意义:

亚稳态是指触发器无法在某个规定的时间内达到可以确认的状态。一旦触发器进入亚稳态,则既无法预测触发器的输出电平,也无法预测什么时候稳定在某个确认的电平上。(稳定所需时间不定、输出结果不定)

二、产生与消除

亚稳态一般发生在跨时钟传输、异步信号采集中以及复位电路中。 在同步系统中,输入总是与时钟同步,因此寄存器的setup time和hold time是满足的,一般情况下是不会发生亚稳态情况的。(在同步逻辑中只要STA分析过了正常是不会遇到亚稳态问题的,STA分析已经保证了每个触发器都能满足自己的建立时间以及保持时间)。

1、跨时钟域信号传输

产生:在跨时钟域信号传输时,由于源寄存器时钟和目的寄存器时钟相移未知,所以源寄存器数据发出数据,数据可能在任何时间到达异步时钟域的目的寄存器,所以无法保证满足目的寄存器Tsu和Th的要求,从而出现亚稳态。

消除:对异步信号进行同步处理;如添加两级D触发器、采用握手进行交互等。

2、异步信号采集

产生:在异步信号采集中,由于异步信号可以在任意时间点到达目的寄存器,所以也无法保证满足目的寄存器Tsu和Th的要求,从而出现亚稳态。

消除:采用FIFO对跨时钟域数据通信进行缓冲设计;

3、异步复位电路

产生:在异步复位电路中,复位信号的释放时间不定,难以保证满足恢复时间(Recovery Time)以及去除时间(Removal Time),从而出现亚稳态。

消除: 对复位电路采用异步复位、同步释放方式处理。详见:三种复位方式详解---同步复位/异步复位/异步复位同步释放

三、亚稳态概率分析

1、亚稳态产生概率:

概率 = (建立时间 + 保持时间)/ 采集时钟周期

可以看出,亚稳态出现的概率与工作时钟频率以及触发器自身的特性(器件的工艺等因素决定了它的建立/保持时间)有关;所以在异步信号采集过程中,要想减少亚稳态发生的概率可以:

1、降低系统工作时钟,增大系统周期,亚稳态概率就会减小(降低工作频率,不常用);

2、 采用工艺更好的FPGA,也就是Tsu和Th时间较小的FPGA器件;

2、多级触发器减少亚稳态

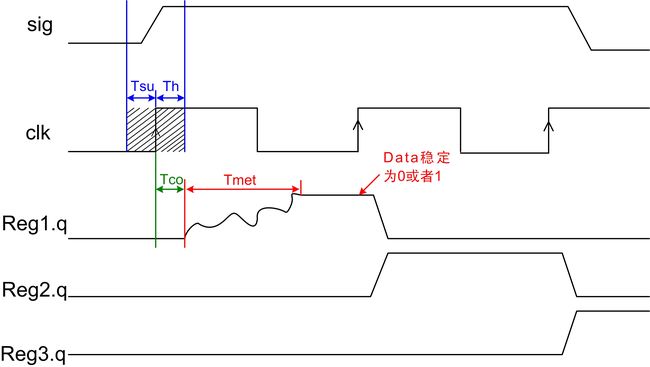

异步信号进行使用的时候,常会对异步信号进行同步处理,同步一般采用多级D触发器级联处理,常见为采用二级D触发器对异步信号进行同步处理,如下图示意:

第一级寄存器产生亚稳态后,如果直接输出很可能将亚稳态传递下去导致系统崩溃;而添加了第二级D触发器后,相当于多给了寄存器一个时钟周期的时间恢复稳定,因此出现亚稳态的几率就会大大减小。由分析可见,触发器级数越多,出现亚稳态的几率就会越小,但是一般来说两级寄存器已经足够,而不需要再添加额外的级数导致资源浪费。(第二级寄存器稳定输出概率为90%,第三极寄存器稳定输出的概率为99%)

四、避免

1 降低系统时钟(不常见,因为高速率正确处理才是目的)

2 用反应更快的触发器(工艺相关,受硬件制约)

3 引入同步机制,防止亚稳态传播(常见的处理方式,即通过一些机制,在现有硬件条件下,最大程度的减少亚稳态发生)

4 改善时钟质量,用边沿变化快速的时钟信号

五、参考文献

关于亚稳态的总结

三种复位方式详解---同步复位/异步复位/异步复位同步释放

静态时序分析STA公式推导以及本质分析(基础概念、多角度公式推导、本质分析)

https://www.cnblogs.com/linjie-swust/archive/2012/01/07/YWT.html

FPGA 基础知识(亚稳态、流水线、时序约束、信号同步、时钟等)

http://blog.sina.com.cn/s/blog_503cdf0d0100cygn.html