IP核:ARM宫斗大戏背后的芯片产业,三大巨头制霸食物链顶端【附下载】| 智东西内参

看点:ARM背后的IP核产业,芯片产业链进一步专业化的未来。

6月10日,芯片设计公司ARM开除其中国合资企业安谋中国CEO吴雄昂,因发现该名高管成立竞争性基金“Alphatecture”,该基金旨在投资使用ARM技术的公司。随后,当事双方发表多份声明,事件也产生多次反转,上演了一场科技行业的“宫斗”大戏。自2016年被软银收购后,ARM公司的名气可谓是蒸蒸日上,一举一动都吸引着整个芯片行业的眼球。今天,我们并不想讨论ARM这场宫斗大戏的是是非非,而是来看看ARM公司背后的大产业——IP核。

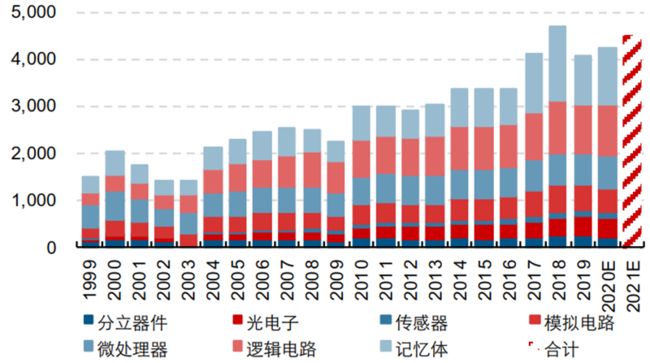

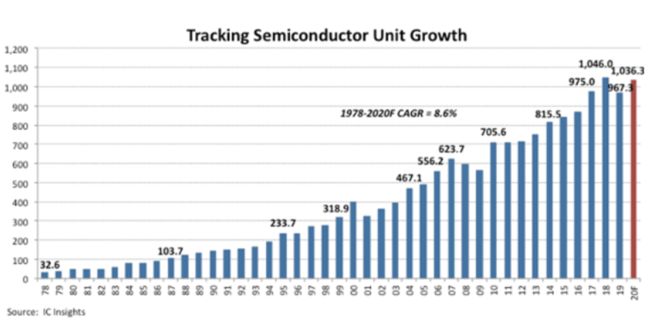

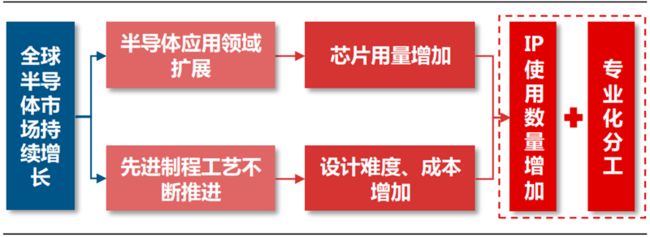

IP(Intellectual Property)核是芯片设计环节中逐步分离出来的、经过验证的、可重复使用的设计模块,其作用就是在芯片设计环节中降低冗余设计成本,降低错误发生的风险,提高芯片设计效率。IP 核本身是产业链不断专业化的产物,是芯片设计知识产权的重要体现,也是半导体产业链下一步升级的重要方向。产业每一轮专业化升级都有其内在的供需原因,且往往是追求规模成本效应的结果,IP 核行业的产生和发展也是如此。

当前全球核心 IP 主要由 ARM、Synopsys、Cadence 提供,合计占比近 65%,以 ARM Cortex、Synopsys ARC、Cadence Tensilica 为首的 IP 核生态覆盖全球芯片设计行业。一方面ARM 份额远超其余玩家,另一方面后进竞争玩家也在奋力追赶。未来,IP 核的技术、生态、平台化建设将是企业护城河的核心构成。

本期的智能内参,我们推荐长江证券公司的研究报告《 模块化芯片设计,稀缺性价值赛道 》,详解IP核行业的内涵、发展现状和国产替代趋势。如果想收藏本文的报告,可以在智东西(公众号:zhidxcom)回复关键词“nc465”获取。

本期内参来源:长江证券

原标题:

《 模块化芯片设计,稀缺性价值赛道》

作者:莫文宇

6月10日,芯片设计公司ARM开除其中国合资企业安谋中国CEO吴雄昂,因发现该名高管成立竞争性基金“Alphatecture”,该基金旨在投资使用ARM技术的公司。随后,当事双方发表多份声明,事件也产生多次反转,上演了一场科技行业的“宫斗”大戏。自2016年被软银收购后,ARM公司的名气可谓是蒸蒸日上,一举一动都吸引着整个芯片行业的眼球。今天,我们并不想讨论ARM这场宫斗大戏的是是非非,而是来看看ARM公司背后的大产业——IP核。

IP(Intellectual Property)核是芯片设计环节中逐步分离出来的、经过验证的、可重复使用的设计模块,其作用就是在芯片设计环节中降低冗余设计成本,降低错误发生的风险,提高芯片设计效率。IP 核本身是产业链不断专业化的产物,是芯片设计知识产权的重要体现,也是半导体产业链下一步升级的重要方向。产业每一轮专业化升级都有其内在的供需原因,且往往是追求规模成本效应的结果,IP 核行业的产生和发展也是如此。

当前全球核心 IP 主要由 ARM、Synopsys、Cadence 提供,合计占比近 65%,以 ARM Cortex、Synopsys ARC、Cadence Tensilica 为首的 IP 核生态覆盖全球芯片设计行业。一方面ARM 份额远超其余玩家,另一方面后进竞争玩家也在奋力追赶。未来,IP 核的技术、生态、平台化建设将是企业护城河的核心构成。

本期的智能内参,我们推荐长江证券公司的研究报告《 模块化芯片设计,稀缺性价值赛道 》,详解IP核行业的内涵、发展现状和国产替代趋势。如果想收藏本文的报告,可以在智东西(公众号:zhidxcom)回复关键词“nc465”获取。

本期内参来源:长江证券

原标题:

《 模块化芯片设计,稀缺性价值赛道》

作者:莫文宇

半导体知识产权的集中体现——IP 核

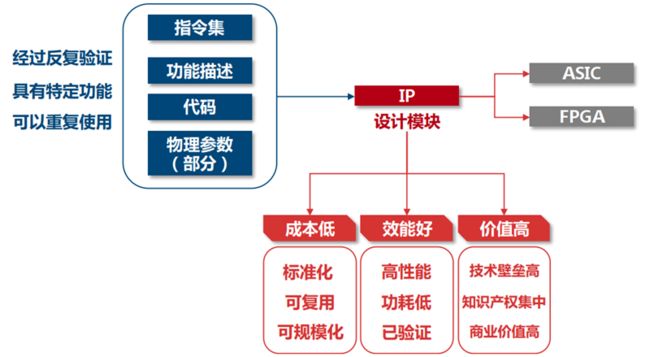

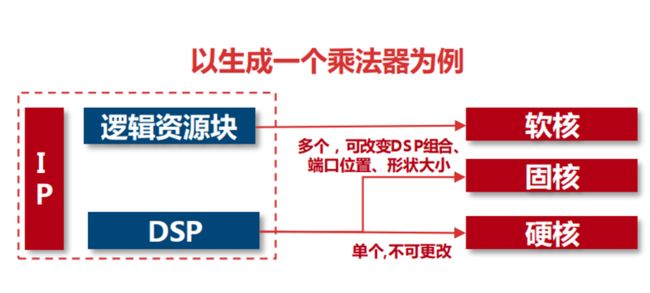

IP 核,是具有知识产权核的集成电路芯核的总称,是经过反复验证过的、具有特定功能的、可以重复使用的、包含特定核心元素的(指令集、功能描述、代码等)集成电路设计宏模块(逻辑或功能单元),如 AHB、 APB、 以太网、SPI、USB、UART 内核等,主要应用于专用集成电路(ASIC)或者可编辑逻辑器件(FPGA)。采用 IP 授权方式设计和开发芯片有如下优点:

1、 经过验证的优质 IP 模块,具有高性能、功耗低、可复用、可规模化、成本适中的特点,可作为独立设计成果被交换、转让和销售;

2、 使用 IP 模块可以让芯片设计厂商基于“模块”开发,避免了重复劳动,有利于芯片设计厂商将精力聚焦到提升核心竞争力的研发中。

3、 在智能终端创新升级加速的阶段,快速的芯片设计并推出产品是抢占市场的重要手段,IP 核心让研发团队仅须整合预先制作的功能区块,不须进行任何设计或检验作业,即能迅速开发大型的系统单芯片设计。

目前,IP 核已经变成系统设计的基本单元,如 Intel 的 CPU 技术、Nvidia 的 GPU 技术、TI 的 DSP 技术、Motorola 的嵌入式 MCU 技术、Trident 的 Graphics 技术等。

从行业主要玩家探寻IP核未来发展趋势

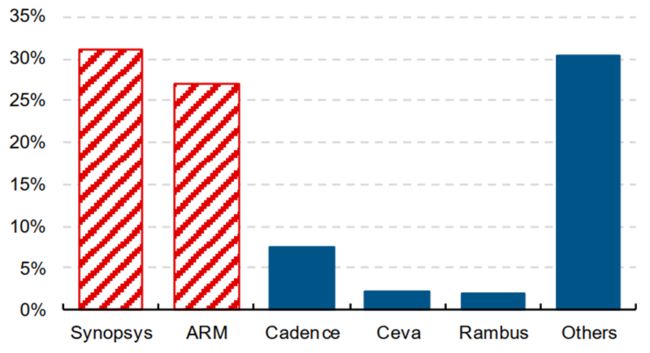

IP 核行业格局的总体格局是高度集中,后进追赶。整体市场保持成长,产品需求增长较快,同时由于 IP 核技术壁垒较高,进入难度大,主要玩家为 ARM、Synopsys、Cadence,同时后进新发竞争者较多;同时,竞争者提供不大相同的产品或服务,用户转换成本较高。

全球 IP 核龙头企业 ARM 从 2007 年 33%的市场占有率增加到 2017 年的 46.2%,但2018~2019 份额分别为 43.02%、40.8%,表明 IP 行业一方面具有高度集中的特征,另一方面集中度在后来者的逐步跟进下呈现下降的趋势。

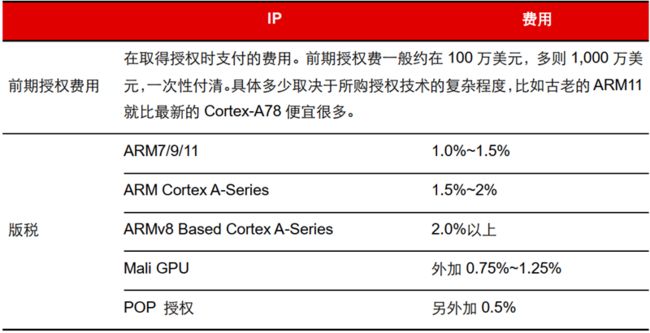

从授权和版权收费来看,Synopsys 收费模式主要为授权,ARM 则在版权收费上一骑绝尘,同时授权收费亦处于第一梯队。ARM 的授权+版税模式是支撑其保持全球龙头地位的重要支柱。

国产替代浪潮

总结前文,IP核行业有以下三大特点:

1、高度集中,Synopsys、Cadence 等老牌 EDA 厂商在积极扩张 IP 核业务,新兴玩家也在持续加入;

2、不涉及实际制造环节,毛利率较高,研发费用+并购费用高;

3、竞争核心力:

对于一家IP核公司,其核心竞争力体现在以下三个方面:

IP 种类丰富度。需要技术自研能力,也需要以并购方式更快地获取技术,打造自身的技术护城河;

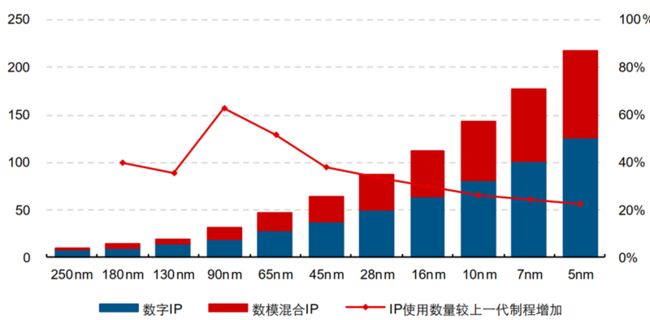

对制程和工艺的持续探索。随着摩尔定律演进,FinFET、FD-SOI 等新技术持续发展,SoC、Chiplet 技术也在不断完善,对于 IP 行业来说对先进技术的不断探索将会是竞争的重要环节。

生态+平台化建设。由于 IP 模块和芯片设计企业客户的研发体系是深度耦合的,IC 设计企业的技术积累,全都基于所采用的 IP,因此迁移成本较高。建立上下游生态网络可增强客户粘性,打造护城河;同时拓展多种客户群体也可增强经营韧性,寻求新的增长机遇。平台化建设则是在丰富、可靠的 IP 核基础上提供多样化的协同服务,如软件、IC 设计平台、IC 定制等设计服务,一方面提高了对设计能力较弱的初创型公司、系统厂商的服务能力,另一方面可通过业务之间的协同性增强用户粘性。

半导体国产化将为 IP 产业发展提供增长动能。目前我国绝大部分的芯片都建立在国外公司的 IP 授权或架构授权基础上,一方面国外企业具有的优势地位使得授权费用较高,增加了我国芯片设计企业的设计成本;另一方面半导体核心技术和知识产权如果受制于人对于我国的国产芯片的自主和安全而言是一个潜在的风险,因此推进 IP 和芯片底层架构国产化是市场的选择也是国家战略的需求。

本土初创公司快速发展带来 IP用量新市场。随着中国芯片制造及相关产业的快速发展,本土产业链逐步完善,晶圆代工、封测等厂商实力日益提升,为我国初创型芯片设计公司提供了强大的下游支持,我国芯片设计公司数量快速增加。同时,由于初创芯片设计公司技术基础相对薄弱,而快速变化的市场需求对芯片设计的效率和成本有了更高的要求,IP 核可大幅提高芯片设计效率的特性将吸引大量初创芯片设计公司。ICCAD 公布的数据显示,自 2016 年以来,我国芯片设计公司数量大幅提升, 2015 年仅为 736家, 2019 年则增长至 1,780 家,年均复合增长率为 24.71%。

系统厂商和互联网公司芯片定制需求推动 IP 行业进一步发展。随着市场竞争的加剧,终端电子产品如手机、相机及平板电脑等生产厂商开始面对功能多样化挑战及成本压力,进而需要定制符合其特定应用环境下的高性能及低功耗的芯片,因此越来越多的系统厂商和互联网公司加入了定制芯片的行业,以应对产业升级、竞争加剧及核心技术国产化的挑战。例如华为、小米、苹果等系统厂商都拥有了自己的芯片设计团队或者希望依托集成电路设计服务企业帮助自己开发专用芯片,Facebook、谷歌、亚马逊、阿里巴巴等互联网公司纷纷着手开发与其业务相关的自有芯片,这种趋势为集成电路设计产业中半导体 IP 和设计服务模式的发展扩展了市场空间。国内大部分 IP 公司为初创型企业,芯原股份具备全球竞争力。

智东西认为, IP核产业自诞生以来就不断演进。最开始主要由各半导体公司内部的IP核部门来开发维护,伴随设计复杂度上升与上市时间要求缩短,第三方商业IP核开始出现,他们在成本、性能与规模效应上优势明显,很多半导体公司开始采用第三方IP核,并逐渐减少在自研IP核上的投入,IP核产业日益兴盛。经过多年发展,IP核已形成了几家巨头垄断的格局。但是,由于物联网、5G、人工智能等新兴技术的发展,半导体产品生态将会更加丰富,同时设计规模和设计难度也将进一步加大,使得客户对于IP核的种类、功能和性能都提出了更多个性化的需求。这些需求对于国内的新玩家来说是一次难得的机会, 随着中国芯片产业飞速发展,国内IP核行业相信也即将迎来其黄金发展期。

(本账号系网易新闻·网易号“各有态度”签约帐号)

6月10日,芯片设计公司ARM开除其中国合资企业安谋中国CEO吴雄昂,因发现该名高管成立竞争性基金“Alphatecture”,该基金旨在投资使用ARM技术的公司。随后,当事双方发表多份声明,事件也产生多次反转,上演了一场科技行业的“宫斗”大戏。自2016年被软银收购后,ARM公司的名气可谓是蒸蒸日上,一举一动都吸引着整个芯片行业的眼球。今天,我们并不想讨论ARM这场宫斗大戏的是是非非,而是来看看ARM公司背后的大产业——IP核。

IP(Intellectual Property)核是芯片设计环节中逐步分离出来的、经过验证的、可重复使用的设计模块,其作用就是在芯片设计环节中降低冗余设计成本,降低错误发生的风险,提高芯片设计效率。IP 核本身是产业链不断专业化的产物,是芯片设计知识产权的重要体现,也是半导体产业链下一步升级的重要方向。产业每一轮专业化升级都有其内在的供需原因,且往往是追求规模成本效应的结果,IP 核行业的产生和发展也是如此。

当前全球核心 IP 主要由 ARM、Synopsys、Cadence 提供,合计占比近 65%,以 ARM Cortex、Synopsys ARC、Cadence Tensilica 为首的 IP 核生态覆盖全球芯片设计行业。一方面ARM 份额远超其余玩家,另一方面后进竞争玩家也在奋力追赶。未来,IP 核的技术、生态、平台化建设将是企业护城河的核心构成。

本期的智能内参,我们推荐长江证券公司的研究报告《 模块化芯片设计,稀缺性价值赛道 》,详解IP核行业的内涵、发展现状和国产替代趋势。如果想收藏本文的报告,可以在智东西(公众号:zhidxcom)回复关键词“nc465”获取。

本期内参来源:长江证券

原标题:

《 模块化芯片设计,稀缺性价值赛道》

作者:莫文宇

6月10日,芯片设计公司ARM开除其中国合资企业安谋中国CEO吴雄昂,因发现该名高管成立竞争性基金“Alphatecture”,该基金旨在投资使用ARM技术的公司。随后,当事双方发表多份声明,事件也产生多次反转,上演了一场科技行业的“宫斗”大戏。自2016年被软银收购后,ARM公司的名气可谓是蒸蒸日上,一举一动都吸引着整个芯片行业的眼球。今天,我们并不想讨论ARM这场宫斗大戏的是是非非,而是来看看ARM公司背后的大产业——IP核。

IP(Intellectual Property)核是芯片设计环节中逐步分离出来的、经过验证的、可重复使用的设计模块,其作用就是在芯片设计环节中降低冗余设计成本,降低错误发生的风险,提高芯片设计效率。IP 核本身是产业链不断专业化的产物,是芯片设计知识产权的重要体现,也是半导体产业链下一步升级的重要方向。产业每一轮专业化升级都有其内在的供需原因,且往往是追求规模成本效应的结果,IP 核行业的产生和发展也是如此。

当前全球核心 IP 主要由 ARM、Synopsys、Cadence 提供,合计占比近 65%,以 ARM Cortex、Synopsys ARC、Cadence Tensilica 为首的 IP 核生态覆盖全球芯片设计行业。一方面ARM 份额远超其余玩家,另一方面后进竞争玩家也在奋力追赶。未来,IP 核的技术、生态、平台化建设将是企业护城河的核心构成。

本期的智能内参,我们推荐长江证券公司的研究报告《 模块化芯片设计,稀缺性价值赛道 》,详解IP核行业的内涵、发展现状和国产替代趋势。如果想收藏本文的报告,可以在智东西(公众号:zhidxcom)回复关键词“nc465”获取。

本期内参来源:长江证券

原标题:

《 模块化芯片设计,稀缺性价值赛道》

作者:莫文宇

![]()

半导体知识产权的集中体现——IP 核

IP 核,是具有知识产权核的集成电路芯核的总称,是经过反复验证过的、具有特定功能的、可以重复使用的、包含特定核心元素的(指令集、功能描述、代码等)集成电路设计宏模块(逻辑或功能单元),如 AHB、 APB、 以太网、SPI、USB、UART 内核等,主要应用于专用集成电路(ASIC)或者可编辑逻辑器件(FPGA)。采用 IP 授权方式设计和开发芯片有如下优点:

1、 经过验证的优质 IP 模块,具有高性能、功耗低、可复用、可规模化、成本适中的特点,可作为独立设计成果被交换、转让和销售;

2、 使用 IP 模块可以让芯片设计厂商基于“模块”开发,避免了重复劳动,有利于芯片设计厂商将精力聚焦到提升核心竞争力的研发中。

3、 在智能终端创新升级加速的阶段,快速的芯片设计并推出产品是抢占市场的重要手段,IP 核心让研发团队仅须整合预先制作的功能区块,不须进行任何设计或检验作业,即能迅速开发大型的系统单芯片设计。

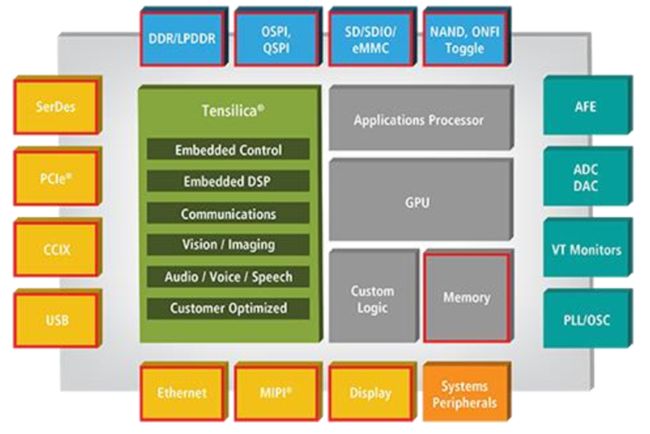

目前,IP 核已经变成系统设计的基本单元,如 Intel 的 CPU 技术、Nvidia 的 GPU 技术、TI 的 DSP 技术、Motorola 的嵌入式 MCU 技术、Trident 的 Graphics 技术等。

▲以 ARM 的 IP 应用设计为例,芯片可视作多个 IP 模块搭建而成的

▲以 ARM 的 IP 应用设计为例,芯片可视作多个 IP 模块搭建而成的

![]()

从行业主要玩家探寻IP核未来发展趋势

IP 核行业格局的总体格局是高度集中,后进追赶。整体市场保持成长,产品需求增长较快,同时由于 IP 核技术壁垒较高,进入难度大,主要玩家为 ARM、Synopsys、Cadence,同时后进新发竞争者较多;同时,竞争者提供不大相同的产品或服务,用户转换成本较高。

全球 IP 核龙头企业 ARM 从 2007 年 33%的市场占有率增加到 2017 年的 46.2%,但2018~2019 份额分别为 43.02%、40.8%,表明 IP 行业一方面具有高度集中的特征,另一方面集中度在后来者的逐步跟进下呈现下降的趋势。

从授权和版权收费来看,Synopsys 收费模式主要为授权,ARM 则在版权收费上一骑绝尘,同时授权收费亦处于第一梯队。ARM 的授权+版税模式是支撑其保持全球龙头地位的重要支柱。

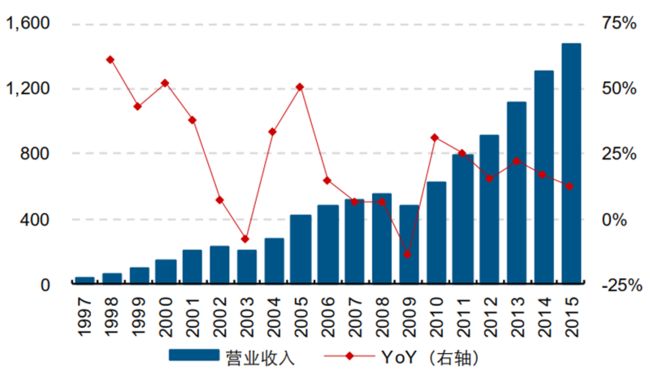

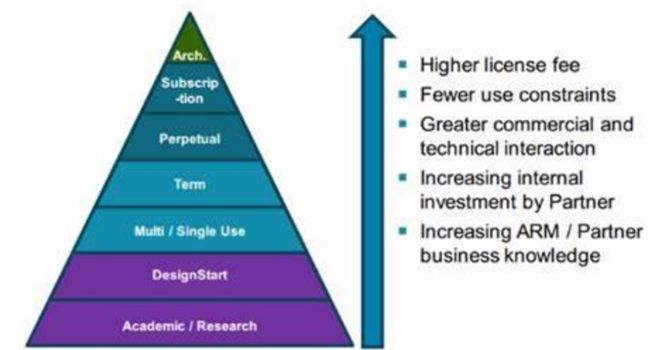

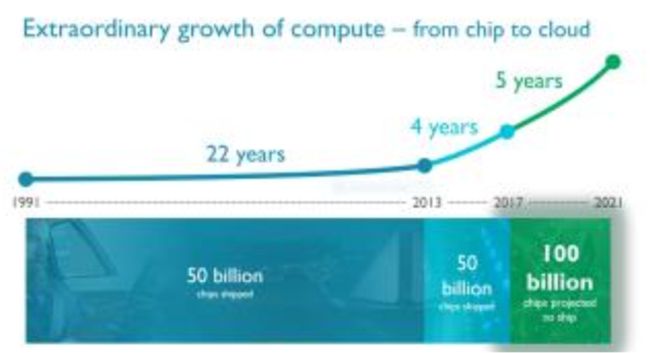

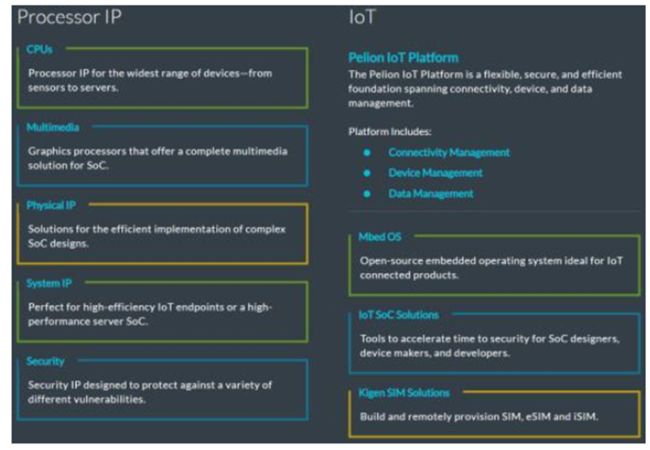

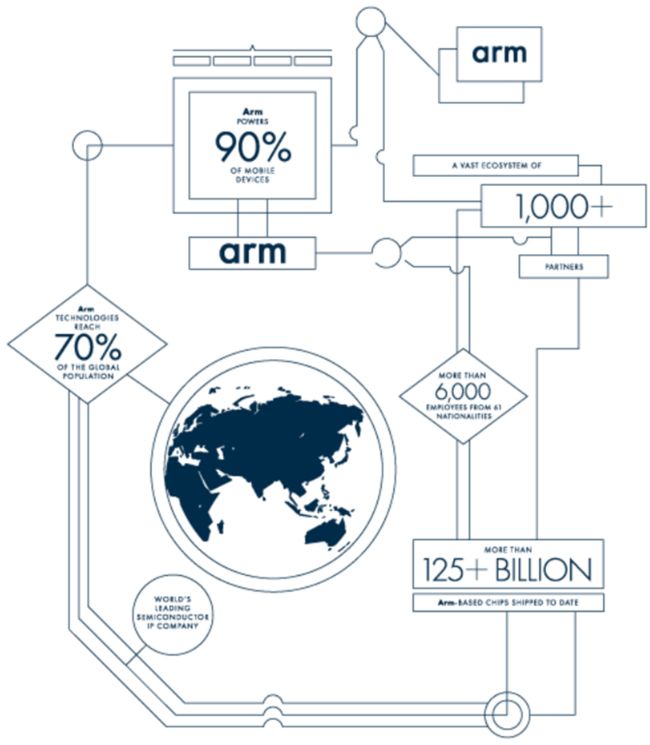

1、 ARM:全球 IP 绝对龙头,生态化深筑护城河

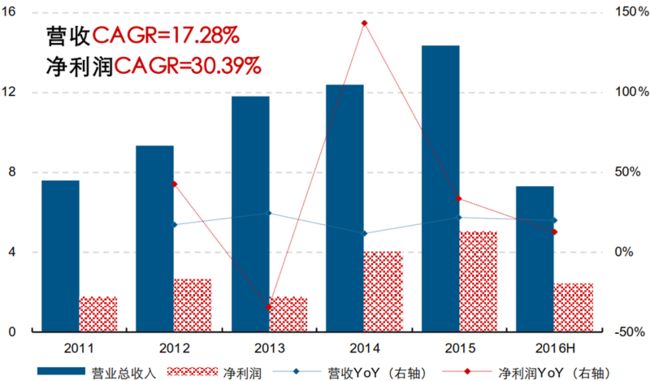

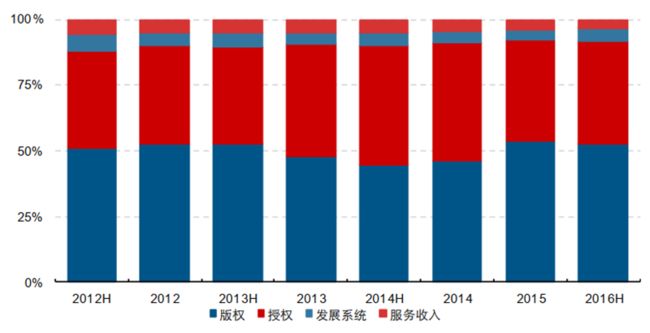

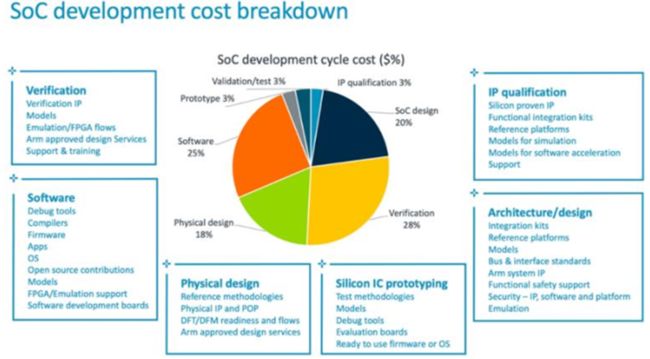

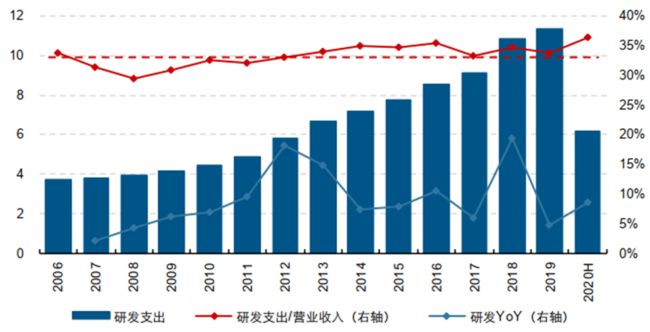

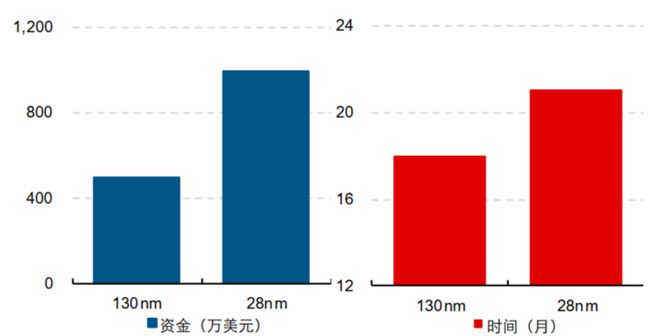

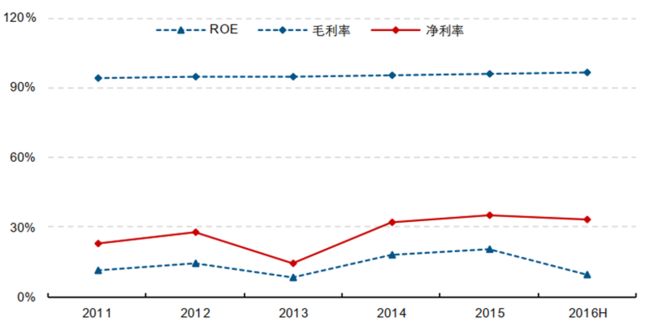

ARM 是全球最大的芯片架构(IP)供应商,成立于 1978 年,1990 年代向 RISC 指令集发展,随后迅速成长为全球低功耗、高性能芯片架构龙头,市占率长期高于 40%。ARM 目前全球芯片客户超过 500 家,生态合作伙伴遍布全球半导体产业链,已形成以Arm 为核心的全球最大的技术生态体系。 ARM 的处理器架构具有性能高、成本优和能耗低的优势,从 21 世纪开始在手机、平板电脑、嵌入控制、多媒体数字等处理器领域迅速获得主导地位。1991 年至 2017 年全球已出货超 1,000 亿颗使用 ARMIP 核的芯片,而 ARM 预计下一个千亿出货量将在 2021年实现。截至 2020 年,全球已出货超 1,600 亿颗使用 ARMIP 核的芯片。在中国市场上,目前 ARM 的中国合作伙伴超过 200 家,国产 SoC 中有 95%是基于 Arm 处理器技术,使用 Arm 处理器技术的中国客户的出货量超过 160 亿。 ARM 处理器市场覆盖率最高、发展趋势广阔,基于 ARM 技术的 32 位微处理器,市场的占有率目前已达到 80%。我国的中兴集成电路、大唐电讯、华为海思,以及国外的一些公司如德州仪器、意法半导体、Philips、Intel、Samsung 等都推出了自己设计的基于 ARM 核的处理器。ARM 在多个领域具备优势地位: 随着 2010 年以来智能手机在全球市场的高速发展,低成本、高性能、低功耗的 ARM架构受到各大厂商的欢迎,自 2011 年直到 2016 年底被 Softbank 收购前,ARM 营收实现了年复合增长 17.28%(未计算 2016 年中数据),在 2015 年达到 14.34 亿美元;净利润实现年复合增长 30.39%,达 5.03 亿美元,净利率超 30%。 IP 核授权业务是 ARM 最主要的营收来源,占比在 2012H~2016H 持续提升,从 94.78%不断增长到 96.45%,显示 IP 核授权业务在 ARM 自身技术和生态优势下盈利能力不断增长。在 IP 核授权类收入中,版权费和授权费收入分别约占总收入的 50%/40%,随着全球芯片出货量的快速增长+ARM 商业策略的调整(Arm Flexible Access for Startups,初创企业可实现 0 费用开发 ARM 芯片),版权费收入占比呈现逐步提高的趋势。 ARM 核心业务为 IP 架构研发和销售,不从事芯片实际的生产与制造,因此毛利率较高,2011~2016H 年间毛利率维持超 90%;净利率同样维持较高水平,截至 2016H 净利率达 33.36%;ROE 基本维持在 10%~20%之间。研发投入上 ARM 的研发支出/营业收入占比约为 30%。 ▲ARM 的毛利率长期高于 90%,净利率也在逐步提升至超 30%

▲ARM 的毛利率长期高于 90%,净利率也在逐步提升至超 30%

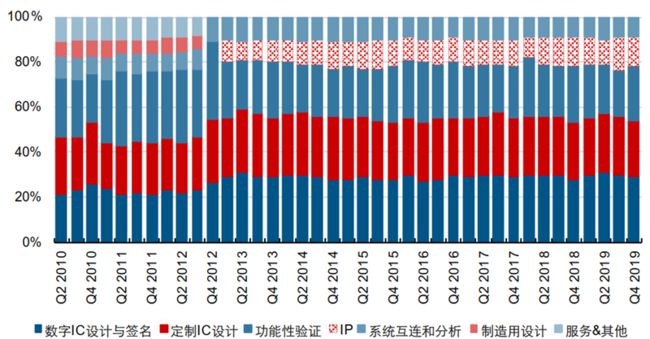

2、 Synopsys:EDA 龙头加速并购,IP 业务地位持续提升

Synopsys 成立于1986 年,总部位于美国硅谷,是全球排名第一的电子设计自动化(EDA)解决方案提供商,全球排名第二的芯片 IP 核供应商,同时还提供用于验证包含芯片的电子系统和在其上运行的软件和硬件,另外还是全球领先的软件安全供应商。Synopsys的 2019 年营业额逾 33 亿美元,拥有 3,200 多项已批准专利。Synopsys 目前拥有 14,000多名员工,分布在全球 116 个分支机构。 与 ARM 专注于 IP 核架构不同,Synopsys 主体业务为 EDA,IP 和系统集成业务约占营收的 30%,近年来 IP 核业务占比稳定提升。 Synopsys 的 DesignWare IP 系列包括逻辑库、嵌入式存储器、嵌入式测试单元、模拟IP、接口 IP、安全 IP 和嵌入式处理器等产品,整体覆盖面较广。Synopsys 的IPAccelerated 通过 IP 原型开发套件和定制的 IP 子系统扩展其广泛建立的、经过硅验证的 DesignWare IP 产品组合,从而可以帮助芯片设计公司加速原型开发、软件开发以及 IP 与 SoC 的集成。Synopsys 的 Verification IP 产品组合(属于 Verification Continuum平台)也属于 IP 产品类别。 随着 2010 年以来智能手机渗透率持续提升,可穿戴设备、IoT 等领域不断发展,全球芯片出货量稳定增加,对 IP 核的需求也不断提升。自 2010 年以来 SynopsysIP 核及系统集成的营收占比持续提升,从 2010 Q3 的 12.91%提升至 2019 Q4 的 31.86%。 ▲Synopsys 自 2010 年来 IP 业务占比持续提升,已成为 EDA 软件以外的重要业务支柱

▲Synopsys 自 2010 年来 IP 业务占比持续提升,已成为 EDA 软件以外的重要业务支柱

▲Synopsys 净利润在 2018、2019 大幅提升(单位:亿美金)

▲Synopsys 净利润在 2018、2019 大幅提升(单位:亿美金)

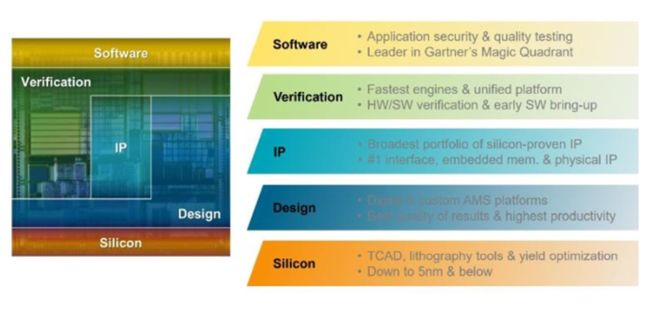

3、 Cadence:全球前三 IP 供应商,平台化打造竞争力

Cadence 是专门从事 EDA 软件服务的公司,是全球最大的 EDA、程序方案服务和设计服务供应商之一,也是全球第三的 IP 核供应商。公司产品涵盖了电子设计的整个流程,包括系统级设计,功能验证,IC 综合及布局布线,模拟、混合信号及射频 IC 设计,全定制集成电路设计,IC 物理验证,PCB 设计和硬件仿真建模等。 Cadence IP 产品组合包括经过硅验证的 Tensilica IP 内核,模拟 PHY 接口,基于标准的 IP 内核,验证 IP 和其他解决方案,以及针对当前和新兴行业标准的定制服务。IP 核产品覆盖 DDR/LPDDR、OSPI、SD/SDIO、NAND/ONFIToggle、SerDes、PCIe、CCIX等。 ▲Cadence 除 Tensilica 以外的主要 IP 核能力

▲Cadence 除 Tensilica 以外的主要 IP 核能力

▲Cadence 2013 年以来 ROE 逐渐走高,2019 年达 58.32%

▲Cadence 2013 年以来 ROE 逐渐走高,2019 年达 58.32%

![]()

国产替代浪潮

总结前文,IP核行业有以下三大特点:

1、高度集中,Synopsys、Cadence 等老牌 EDA 厂商在积极扩张 IP 核业务,新兴玩家也在持续加入;

2、不涉及实际制造环节,毛利率较高,研发费用+并购费用高;

3、竞争核心力:

对于一家IP核公司,其核心竞争力体现在以下三个方面:

IP 种类丰富度。需要技术自研能力,也需要以并购方式更快地获取技术,打造自身的技术护城河;

对制程和工艺的持续探索。随着摩尔定律演进,FinFET、FD-SOI 等新技术持续发展,SoC、Chiplet 技术也在不断完善,对于 IP 行业来说对先进技术的不断探索将会是竞争的重要环节。

生态+平台化建设。由于 IP 模块和芯片设计企业客户的研发体系是深度耦合的,IC 设计企业的技术积累,全都基于所采用的 IP,因此迁移成本较高。建立上下游生态网络可增强客户粘性,打造护城河;同时拓展多种客户群体也可增强经营韧性,寻求新的增长机遇。平台化建设则是在丰富、可靠的 IP 核基础上提供多样化的协同服务,如软件、IC 设计平台、IC 定制等设计服务,一方面提高了对设计能力较弱的初创型公司、系统厂商的服务能力,另一方面可通过业务之间的协同性增强用户粘性。

半导体国产化将为 IP 产业发展提供增长动能。目前我国绝大部分的芯片都建立在国外公司的 IP 授权或架构授权基础上,一方面国外企业具有的优势地位使得授权费用较高,增加了我国芯片设计企业的设计成本;另一方面半导体核心技术和知识产权如果受制于人对于我国的国产芯片的自主和安全而言是一个潜在的风险,因此推进 IP 和芯片底层架构国产化是市场的选择也是国家战略的需求。

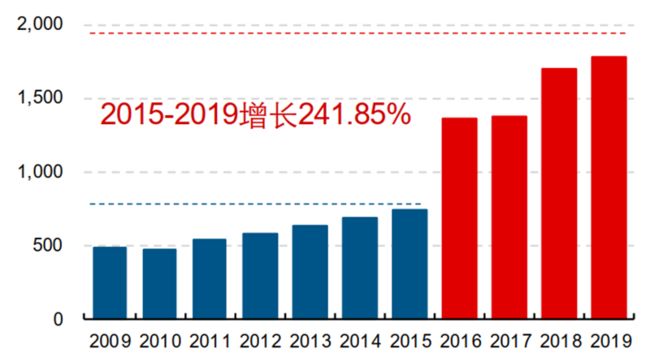

本土初创公司快速发展带来 IP用量新市场。随着中国芯片制造及相关产业的快速发展,本土产业链逐步完善,晶圆代工、封测等厂商实力日益提升,为我国初创型芯片设计公司提供了强大的下游支持,我国芯片设计公司数量快速增加。同时,由于初创芯片设计公司技术基础相对薄弱,而快速变化的市场需求对芯片设计的效率和成本有了更高的要求,IP 核可大幅提高芯片设计效率的特性将吸引大量初创芯片设计公司。ICCAD 公布的数据显示,自 2016 年以来,我国芯片设计公司数量大幅提升, 2015 年仅为 736家, 2019 年则增长至 1,780 家,年均复合增长率为 24.71%。

系统厂商和互联网公司芯片定制需求推动 IP 行业进一步发展。随着市场竞争的加剧,终端电子产品如手机、相机及平板电脑等生产厂商开始面对功能多样化挑战及成本压力,进而需要定制符合其特定应用环境下的高性能及低功耗的芯片,因此越来越多的系统厂商和互联网公司加入了定制芯片的行业,以应对产业升级、竞争加剧及核心技术国产化的挑战。例如华为、小米、苹果等系统厂商都拥有了自己的芯片设计团队或者希望依托集成电路设计服务企业帮助自己开发专用芯片,Facebook、谷歌、亚马逊、阿里巴巴等互联网公司纷纷着手开发与其业务相关的自有芯片,这种趋势为集成电路设计产业中半导体 IP 和设计服务模式的发展扩展了市场空间。国内大部分 IP 公司为初创型企业,芯原股份具备全球竞争力。

智东西认为, IP核产业自诞生以来就不断演进。最开始主要由各半导体公司内部的IP核部门来开发维护,伴随设计复杂度上升与上市时间要求缩短,第三方商业IP核开始出现,他们在成本、性能与规模效应上优势明显,很多半导体公司开始采用第三方IP核,并逐渐减少在自研IP核上的投入,IP核产业日益兴盛。经过多年发展,IP核已形成了几家巨头垄断的格局。但是,由于物联网、5G、人工智能等新兴技术的发展,半导体产品生态将会更加丰富,同时设计规模和设计难度也将进一步加大,使得客户对于IP核的种类、功能和性能都提出了更多个性化的需求。这些需求对于国内的新玩家来说是一次难得的机会, 随着中国芯片产业飞速发展,国内IP核行业相信也即将迎来其黄金发展期。

(本账号系网易新闻·网易号“各有态度”签约帐号)

![]()