9.I.MX6ULL时钟树

1.硬件原理图

1.32.768Khz的晶振,供给RTC使用

2.在6U中T16与T17IO口中接了一个24MHz的晶振

2.I.MX系统时钟分析

1.7路PLL

为了方便升成时钟,从24MHz晶振中声称7路PLL,每一路又升成PFD_PLL。

配置详见时钟树。还要学会看RM手册进行配置频率,具体看下面。

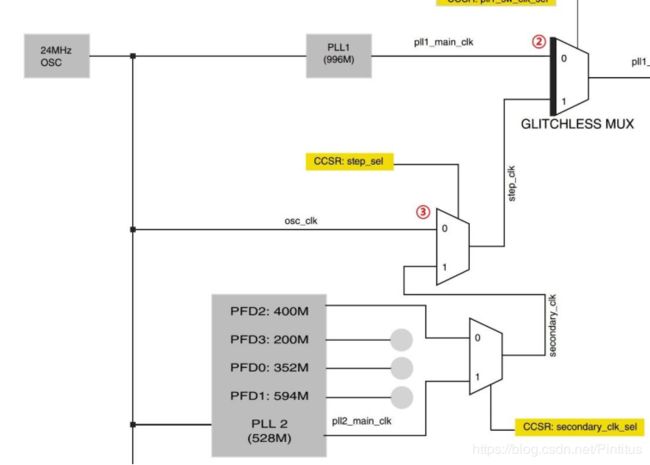

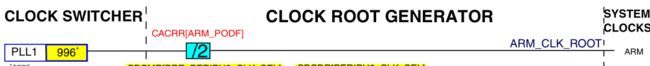

2.配置主频

我们想要配置内核主频528MHz。

我们的目标是配置ARM内核主频,首先第一步就是配置CLOCK SWITCHER的PLL1,之后进行CACRR寄存器的配置的分频配置。

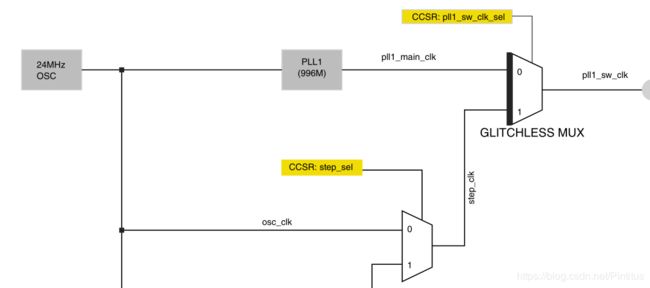

首先使用的是24M的OSC外部IO晶振,想要配置到pll1_sw_clk有两种方式,一种走,配置pll1_main_clk或者step_clk模式。但是我们第一次不能配置pll1_main_clk,因为需要配置PLL1才可以,所以我们先走osc_clk的路线,再恢复到pll1_main_clk的路线,他们都是CACRR寄存器中的模式。详见Reference manual手册。其种step_clk模式还要搭配osc_clk模式。

PLL output frequency = Fref * DIV_SEL/2(DIV_SEL在54-108区间)其中Fref=24M , 若想输出528MHz,且从手册得知PLL1介于650M-1.4GHz需要配置输出频率为1056MHz,然后进行二分频得到。故DIV_SEL=88。

最后不要忘记切换回pll1_main_clk的模式。

3.示例代码

bsp_clk.c

void imx6ull_clkinit(void)

{

/*Init pll_main_clk is 528MHz*/

/*SWITCHER */

if(( (CCM->CCSR >> 2) & 0x1) == 0)/*Currently register bit 2 is pll1_main_clk*/

{

/*Setup STEP_SEL is osc_clk mode 24MHz*/

CCM->CCSR &= ~(1<<8) ;

CCM->CCSR |= (1<<2);

}

/*Setup ANALOG_PLL_ARM Register Enable the clock output and DIV_SELECT is 88*/

CCM_ANALOG->PLL_ARM = ((88<<0) & 0x7f) | (1<<13);

/*CLOCK ROOT GENERATOR divide by 2*/

CCM->CACRR = 1;

CCM->CCSR &= ~(1<<2);/*setup pll1_main_clk*/

}

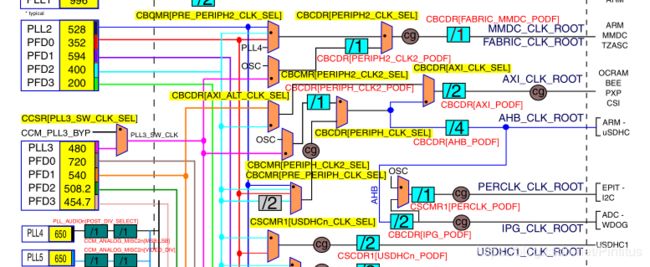

3.PLL配置

PLL2的固定频率是528MHz,PLL3的固定频率是480MHz。

1.初始化PLL2,PFD0-3 寄存器CCM_ANALOG_PFD_528用于设置四路PFD的时钟,比如PFD0=528*18/PFD_FRAC,

/*Peripheral clk setup,recommond configure*/

reg = CCM_ANALOG->PFD_528;

reg &= ~(0x3f3f3f3f);

reg |= (32<<24);/*PLL2_PFD3 = 297MHz*/

reg |= (24<<16);/*PLL2_PFD2 = 396MHz*/

reg |= (16<<8); /*PLL2_PFD1 = 594MHz*/

reg |= (27<<0); /*PLL2_PFD0 = 352MHz*/

CCM_ANALOG->PFD_528 = reg;

reg = 0 ;

reg = CCM_ANALOG->PFD_480;

reg &= ~(0x3f3f3f3f);

reg |= (19<<24);/*PLL3_PFD3 = 454.7MHz*/

reg |= (17<<16);/*PLL3_PFD2 = 508.2MHz*/

reg |= (16<<8); /*PLL3_PFD1 = 540MHz*/

reg |= (12<<0); /*PLL3_PFD0 = 720MHz*/

CCM_ANALOG->PFD_480 = reg;

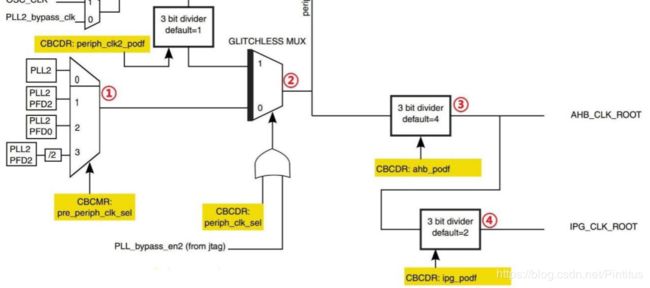

4.其他外设时钟源

配置AHB_CLK_ROOT,PERCLK_CLK_ROOT以及IPG_CLK_ROOT时钟源。

因为PERCLK_CLK_ROOT和IPG_CLK_ROOT要用到AHB_CLK_ROOT。

AHB_CLK_ROOT初始化

-->AHB_CLK_ROOT=132M

1.设置CBCMR寄存器 ,2.设置CBCDR[PERIPH_CLK_SEL]寄存器,3.再经过CBCDR[AHB_PODF]寄存器为分频。

-->IPG_CLK_ROOT=66M

1.设置IPG_PIDF = 1

-->PER_CLK_ROOT=66M

1.设置CSCMR1的PERCLK_CLK_SER=0

/*设置AHB_CLK_ROOT=132MHz*/

CCM->CBCMR &= ~(3<<18);

CCM->CBCMR |= (1<<18); /*设置为396M的PLL2_PFD2的时钟*/

CCM->CBCDR &= ~(1<<25); /*设置PERIPH_CLK_SEL=0*/

while(CCM->CDHIPR & (1<<5));/*等待握手信号*/

#if 0

内部可能会出问题,因为3分频BOOT ROOM以及帮忙设置好了

CCM->CBCDR &=~(7<<10);

CCM->CBCDR |= (2 << 10); /*3分频*/

while(CCM->CDHIPR & (1<<1));/*等待握手信号*/

#endif

/*IPG_CLK_ROOT=66M*/

CCM->CBCDR &= ~(3<<8);

CCM->CBCDR |= (1<<8);//二分频

/*PER_CLK_ROOT=66M*/

CCM->CSCMR1 &= ~(1<<6);

CCM->CSCMR1 &= ~(0x3f<<0);//一分频