XILINX SGMII千兆以太网 (1)

这篇文章将对以太网的学习过程进行简单记录和总结。

因为工程进度的原因,先采用xilinx自带的IP的形式进行开发,参考PG047。

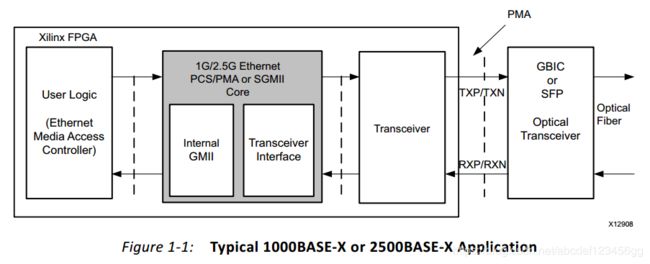

The LogiCORE™ IP 1G/2.5G Ethernet PCS/PMA or Serial Gigabit Media Independent Interface (SGMII) core provides a flexible solution for connection to an Ethernet Media Access Controller (MAC) or other custom logic.

It supports two standards: the 1000BASE-X and 2500BASE-X Physical Coding Sublayer (PCS) and Physical Medium Attachment (PMA) operation, as defined in the IEEE 802.3-2008 standard and the Gigabit Media Independent Interface (GMII) to Serial-GMII (SGMII) bridge or SGMII to GMII bridge, as defined in the Serial-GMII Specification V1.7 (CISCO SYSTEMS,

ENG-46158) [Ref 1].

Dynamic switching between 1000BASE-X and SGMII standards is also supported

1 首先扫盲

以太网芯片MAC和PHY的关系

https://www.cnblogs.com/pengdonglin137/p/3575691.html

1.1 以太网MAC是什么?

MAC即Media Access Control,即媒体访问控制子层协议。

该协议位于OSI七层协议中数据链路层的下半部分,主要负责控制与连接物理层的物理介质。

在发送数据的时候,MAC协议可以事先判断是否可以发送数据,如果可以发送将给数据加上一些控制信息,最终将数据以及控制信息以规定的格式发送到物理层。

在接收数据的时候,MAC协议首先判断输入的信息并是否发生传输错误,如果没有错误,则去掉控制信息发送至LLC层。

以太网数据链路层其实包含MAC(介质访问控制)子层和LLC(逻辑链路控制)子层。一块以太网卡MAC芯片的作用不但要实现MAC子层和LLC子层的功能,还要提供符合规范的PCI界面以实现和主机的数据交换。

MAC从PCI总线收到IP数据包(或者其他网络层协议的数据包)后,将之拆分并重新打包成最大1518Byte,最小64Byte的帧。这个帧里面包括了目标MAC地址、自己的源MAC地址和数据包里面的协议类型(比如IP数据包的类型用80表示)。最后还有一个DWORD(4Byte)的CRC 码。

可是目标的MAC地址是哪里来的呢?

这牵扯到一个ARP协议(介乎于网络层和数据链路层的一个协议)。第一次传送某个目的IP地址的数据的时候,先会发出一个ARP包,其MAC的目标地址是广播地址,里面说到:”谁是xxx.xxx.xxx.xxx这个IP地址的主人?”因为是广播包,这个局域网的所有主机接收这个ARP请求。收到请求的主机将这个IP地址和自己的相比较,如果不相同就不予理会,如果相同就发出ARP响应包。这个IP地址的主机收到这个ARP请求包后回复的ARP响应里说到:”我是这个IP地址的主人”。这个包里面就包括了他的MAC地址。以后的给这个IP地址的帧的目标MAC 地址就被确定了。(其它的协议如IPX/SPX也有相应的协议完成这些操作)。

IP地址和MAC地址之间的关联关系保存在主机系统里面,叫做ARP表,由驱动程序和操作系统完成。

在Microsoft的系统里面可以用arp- a的命令查看ARP表。收到数据帧的时候也是一样,做完CRC以后,如果没有CRC校验错误,就把帧头去掉,把数据包拿出来,通过标准的接口传递给驱动和上层的协议栈,最终正确的达到我们的应用程序。

还有一些控制帧,例如流控帧也需要MAC直接识别并执行相应的行为。

以太网MAC芯片的一端接计算机PCI总线,另外一端就接到PHY芯片上。它们之间是通过MII接口链接的。

1.2 以太网PHY是什么?

PHY是物理接口收发器,它实现物理层。IEEE-802.3标准定义了以太网PHY。

包括MII/GMII(介质独立接口)子层,PCS(物理编码)子层,PMA(物理介质附加)子层,PMD(物理介质相关)子层,MDI子层。它符合IEEE-802.3k中用于10BaseT(第14条)和 100BaseTX(第24条和第25条)的规范。

PHY在发送数据的时候,收到MAC过来的数据(对PHY来说,没有帧的概念,对它来说,都是数据而不管什么地址、数据还是CRC。对于 100BaseTX因为使用4B/5B编码,每4bit就增加1bit的检错码),然后把并行数据转化为串行流数据,再按照物理层的编码规则把数据编码。 再变为模拟信号把数据送出去。收数据时的流程反之。

PHY还有个重要的功能就是实现CSMA/CD的部分功能。

它可以检测到网络上是否有数据在传送,如果有数据在传送中就等待,一旦检测到网络空闲,再等待一个随机时间后将送数据出去。如果两个碰巧同时送出了数据,那样必将造成冲突,这时候,冲突检测机构可以检测到冲突,然后各等待一个随机的时间重新发送数据。这个随机时间很有讲究的,并不是一个常数,在不同的时刻计算出来的随机时间都是不同的,而且有多重算法来应付出现概率很低的同两台主机之间的第二次冲突。

许多网友在接入Internt宽带时,喜欢使用”抢线”强的网卡,就是因为不同的PHY碰撞后计算随机时间的方法设计上不同,使得有些网卡比较”占便宜”。不过,抢线只是对广播域的网络而言的,对于交换网络和ADSL这样点到点连接到局端设备的接入方式,没什么意义。而且”抢线”也只是相对而言的,不会有质的变化。

现在交换机的普及使得交换网络的普及,使得冲突域网络少了很多,极大地提高了网络的带宽。但是如果用HUB,或者共享带宽接入Internet的时候还是属于冲突域网络,有冲突碰撞的。交换机和HUB最大的区别就是:一个是构建点到点网络的局域网交换设备,一个是构建冲突域网络的局域网互连设备。

除此之外PHY还提供了和对端设备连接的重要功能,并通过LED灯显示出自己目前的连接的状态和工作状态让我们知道。

当我们给网卡接入网线的时候,PHY不断发出的脉冲信号检测到对端有设备,它们通过标准的”语言”交流,互相协商并确定连接速度、双工模式、是否采用流控等。通常情况下,协商的结果是两个设备中能同时支持的最大速度和最好的双工模式。这个技术被称为Auto Negotiation或者NWAY,它们是一个意思–自动协商。

具体传输过程为:

发送数据时,网卡首先侦听介质上是否有载波(载波由电压指示),如果有,则认为其他站点正在传送信息,继续侦听介质。一旦通信介质在一定时间段内(称为帧间缝隙IFG=9.6微秒)是安静的,即没有被其他站点占用,则开始进行帧数据发送,同时继续侦听通信介质,以检测冲突。在发送数据期间,如果检测到冲突,则立即停止该次发送,并向介质发送一个“阻塞”信号,告知其他站点已经发生冲突,从而丢弃那些可能一直在接收的受到损坏的帧数据,并等待一段随机时间(CSMA/CD确定等待时间的算法是二进制指数退避算法)。在等待一段随机时间后,再进行新的发送。如果重传多次后(大于16 次)仍发生冲突,就放弃发送。接收时,网卡浏览介质上传输的每个帧,如果其长度小于64字节,则认为是冲突碎片。如果接收到的帧不是冲突碎片且目的地址是本地地址,则对帧进行完整性校验,如果帧长度大于1518字节(称为超长帧,可能由错误的LAN驱动程序或干扰造成)或未能通过CRC校验,则认为该帧发生了畸变。通过校验的帧被认为是有效的,网卡将它接收下来进行本地处理。

1.3 SerDes 是什么?

SerDes,是SERializer(串行器)和DESerializer(解串器)的简称,是一种点对点的高速串行通信技术。

我觉的SerDes就是一个超级串口收发器!

最大的特点就是点对点收发、没有随路时钟,它的速率是隐含在协议里的,双方必须按照约定好的波特率进行数据的发送和接受才能正确的完成通信。

这里想说明的是:

1、串口的单双工和数据位宽都是可以配置的,按照自己的需求去设置;

2、串口协议也是有时钟的,只不过这个时钟是隐含在协议里,除了常见的9600、38400、115200,自己也可以去配置特殊模式的串口,关键是双方都要遵守相同的协议。

那么SerDes呢?

相同的,SerDes也是收发两条线,准确地说,是两组,因为它是差分形式,即tx_p、tx_n,rx_p、rx_n;在数据端也是可以配置成不同的数据位宽和单双工模式。

不同的,就是在于SerDes的时钟是隐含在数据中!这就需要额外的电路去完成数据和时钟的“融合”与“解析”,而这正是PCS和PMA的作用,其内部采用的编码技术和信号补偿技术正是为了完美的将时钟“融合”进串行数据(发送端),再将时钟从串行数据中“解析出来”(接收端)!至于内部如8b/10b、去加重、预加重等技术细节可以自行搜索哈。

Xilinx将这个SerDes硬核进行了封装,成为Gigabit Transceiver,即GT,而它在BANK里的位置和数量都是固定的,从这个角度来看这也算是它不灵活的不足所在吧。

2 进阶

2.1、MAC层功能

MAC层功能用一个词概括就是“成帧解帧”,具体来讲:

TX方向对用户侧发送来的MAC帧添加前导码和帧尾校验和,对长度过短帧会在帧尾填充0直至最小帧长,此外流控模块可以根据需要发送pause帧。

RX方向过滤掉不符合规范的数据帧并移除填充域,只有目的MAC地址与自身相符且帧尾校验和正确的数据帧才为有效数据帧,去除前导码和校验域后即发送给用户侧。接收端也会根据可能收到的pause帧做出暂停发送处理。

2.2、以太网帧结构

目前常见的是 Ethernet II 和 IEEE802.3 两种格式,总体可以归纳为:

| 类型 | 目的MAC地址 | 源MAC地址 | 长度/类型 | 有效负荷(可能有填充) | 帧校验 |

| 长度 | 6byte | 6byte | 2byte | 46~1500byte | 4byte |

区别在于 Ethernet II 帧长度/类型域解释为上层协议类型,而 IEEE802.3 同样位置是长度字段。

区分两者的标准是:

- 当该字段值小于等于1500(十六进制的0x05DC)时,为IEEE802.3格式;

- 当该字段值大于等于1536(十六进制的0x0600 )时,帧使用的是Ethernet II格式。

其中Ethernet II最为常见。

2.3 MII 接口

MII --Medium Independent Interface

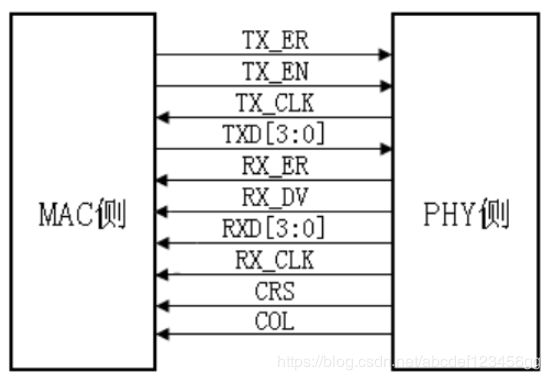

接口连线很多,使能、时钟、标志信号的error、valid等等,共16根线。

2.3.1、RMII 简介

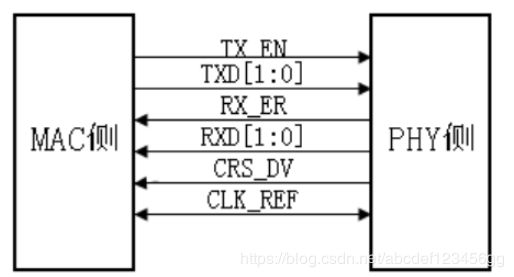

MII连线太多,怎么办,Reduce!

R MII,注意这里不仅仅是连接线数量的减少,更重要的是数据时钟的变化,这里用的是外部参考源提供的CLK_REF参考时钟,在PHY侧数据接收是由外部晶振提供,和接收到的数据处于不同的时钟域,所以需要FIFO进行缓存。

2.3.2、SMII 简介

RMII连线依然太多怎么办?继续减少?串行!

Serial MII,也衍生了SSMII Serial Sync(串行同步)SSSMII Source Sync Serial(源同步串行)。

2.3.3、GMII简介

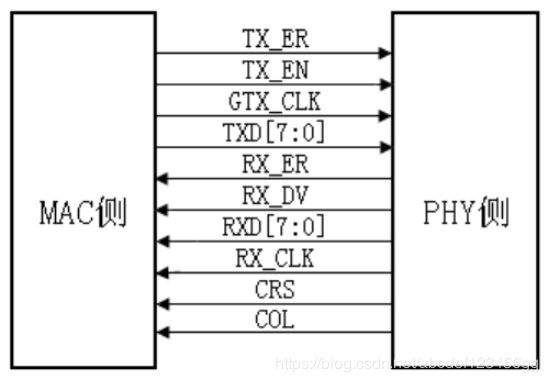

MII的进化版,Gigabit MII 位宽增加一倍,时钟均为125MHz。

值得注意的是,发送参考钟GTX_CLK的方向是由MAC发送给PHY。

GMII --Gigabit Media Independent Interface

GMII采用8位接口数据,工作时钟125MHz,因此传输速率可达1000Mbps。同时兼容MII所规定的10/100 Mbps工作方式。

GMII接口数据结构符合IEEE以太网标准。该接口定义见IEEE 802.3-2000。

发送器

◇ GTXCLK——吉比特TX..信号的时钟信号(125MHz)

◇ TXCLK——10/100M信号时钟

◇ TXD[7..0]——被发送数据

◇ TXEN——发送器使能信号

◇ TXER——发送器错误(用于破坏一个数据包)

注:在千兆速率下,向PHY提供GTXCLK信号,TXD、TXEN、TXER信号与此时钟信号同步。否则,在10/100M速率下,向PHY提供 TXCLK时钟信号,其它信号与此信号同步。其工作频率为25MHz(100M网络)或2.5MHz(10M网络)。

接收器

◇ RXCLK——接收时钟信号(从收到的数据中提取,因此与GTXCLK无关联)

◇ RXD[7..0]——接收数据

◇ RXDV——接收数据有效指示

◇ RXER——接收数据出错指示

◇ COL——冲突检测(仅用于半双工状态)

管理配置

◇ MDC——配置接口时钟

◇ MDIO——配置接口I/O

管理配置接口控制PHY的特性。该接口有32个寄存器地址,每个地址16位。其中前16个已经在“IEEE 802.3,2000-22.2.4 Management Functions”中规定了用途,其余的则由各器件自己指定。

2.3.4、XGMII

XGMII--10 Gigabit Media Independent Interface

“10Gb独立于媒体的接口”,X对应罗马数字10

2.3.5、SGMII

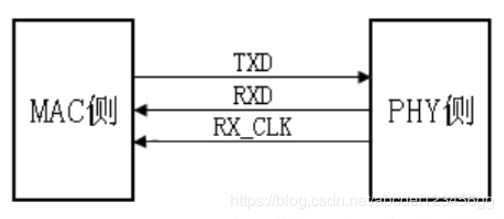

终于到了SGMII,这个RX_CLK是可选的,去掉之后是不是很像串口,MII总线中的标志信号TX_EN、TX_ER、RX_DV、RX_ER都成为串行数据的一部分,这样,人们为了提高数据吞吐,从增加数据线到增加时钟频率,再到减少总线,最终回到了串行的形式,也是非常有趣。

SGMII--Serial Gigabit Media Independent Interface

SGMII为串行吉比特媒体独立接口,用在PHY与MAC之间,SGMII 提供了速率为 10/100/1000 Mbps 的全双工 BASE-T 功能在光传输里,应用在以太网板上。 类似于GMII和RGMII,只不过GMII和RGMII都是并行的,而且需要随路时钟,PCB布线相对麻烦,而且不适应背板应用。

而SGMII是串行的,不需要提供另外的时钟,MAC和PHY都需要CDR去恢复时钟。

另外SGMII是有8B/10b编码的,速率是1.25G。

///////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

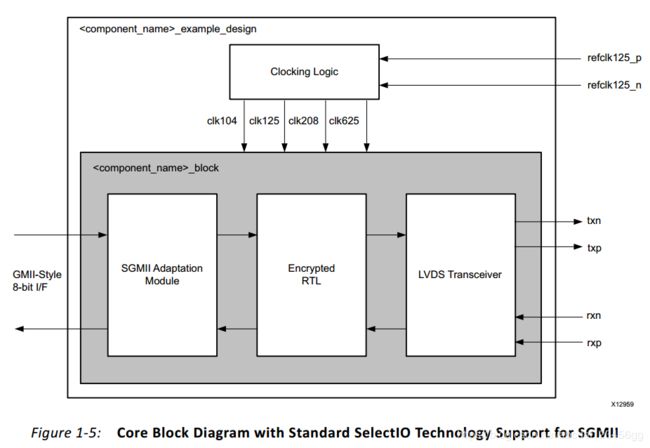

2.4、架构图

SGMII 架构框图:

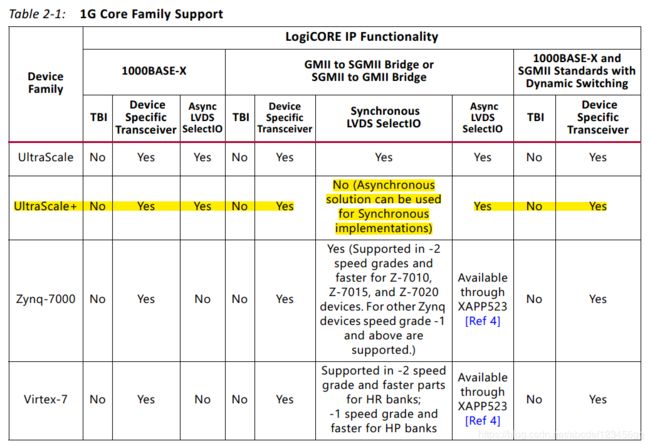

器件的支持度: