Vivado xilinx fft9.0 使用笔记:

****注 仿真实测1024点的转换需要经过1148个时钟周期才能得到转换结果;

模块配置信号含义请参考pg109文档手册(写的贼烂会看晕),不详细说明;

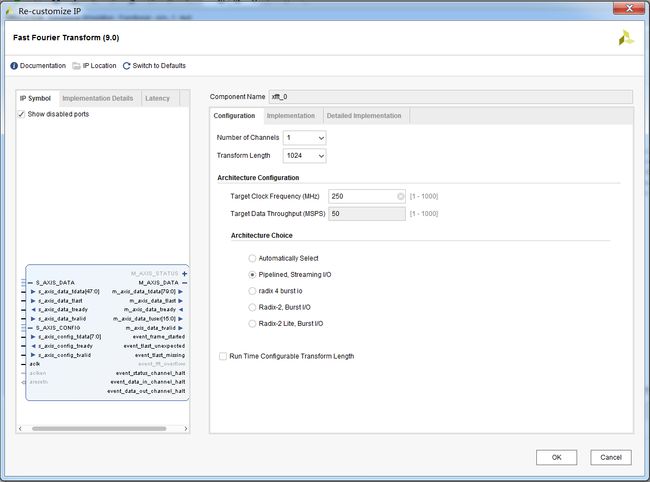

一、查找fft IP核按如下几图配置可实现正确的fft转换结果:

配置1个转换通道;转换数据长度是1024 points;选择流线型结构类型pipelined,streamingI/O,优点并行转换速度快,,缺点占用资源多。 如图1:

图1

如图2,设置数据类型为定点小数;缩减因子设置成Unscaled;RoundingModes设置成Truncation;输入位宽设置24位,精度设置16;Output Ordering 设置成Natural Order;OptionalOutputFieldds勾选XK_INDEX;

图2

如图3 此页信息基本固定配置:

图3

***注:注意图4中区域 有助于帮助你在编写testbenchs时对s_axis_config_tdata进行配置;

如图4 s_axis_config_tdata 只有1位配置fft的fwd/inv;

图4

Testbench代码如下:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: zyp

//

// Create Date: 04/21/2017 08:35:42 PM

// Design Name:

// Module Name: test

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module test();

// Inputs

reg aclk;

reg aresetn;//active low

reg s_axis_config_tvalid;

reg s_axis_data_tvalid;

reg s_axis_data_tlast;

reg m_axis_data_tready;

reg [7:0] s_axis_config_tdata;

//reg [15:0] s_axis_config_tdata;

reg [47: 0] s_axis_data_tdata;

// Outputs

wire s_axis_config_tready;

wire s_axis_data_tready;

wire m_axis_data_tvalid;

wire m_axis_data_tlast;

wire event_frame_started;

wire event_tlast_unexpected;

wire event_tlast_missing;

wire event_status_channel_halt;

wire event_data_in_channel_halt;

wire event_data_out_channel_halt;

//wire [47:0] m_axis_data_tdata;

wire [79:0] m_axis_data_tdata; //un_scaled

wire [15:0] m_axis_data_tuser;

//

//reg[23:0] XK_RE;

//reg[23:0] XK_IM;

reg[39:0] XK_RE;//config unsclaed

reg[39:0] XK_IM;//config unsclaed

reg[23:0] mem0_re[0:4095];

reg[23:0] mem1_re[0:7];

reg[23:0] mem2_re[0:7];

initial $readmemh("D:/fpga/fft1/stimulus0_24bit.dat",mem0_re);

initial $readmemh("D:/fpga/fft1/stimulus1_24bit.dat",mem1_re);

initial $readmemh("D:/fpga/fft1/stimulus2_24bit.dat",mem2_re);

reg[7:0] op_sample= 0;

reg op_sample_first = 1;

reg[7:0] ip_frame=0;

reg[7:0] op_frame=0;

integer i;

// generate clk

always #5 aclk =! aclk;

xfft_0 xfft_m0 (

.aclk(aclk), // input wire aclk

// .aresetn(aresetn),

.s_axis_config_tdata(s_axis_config_tdata), // input wire [7 : 0] s_axis_config_tdata

.s_axis_config_tvalid(s_axis_config_tvalid), // input wire s_axis_config_tvalid

.s_axis_config_tready(s_axis_config_tready), // output wire s_axis_config_tready

.s_axis_data_tdata(s_axis_data_tdata), // input wire [47 : 0] s_axis_data_tdata

.s_axis_data_tvalid(s_axis_data_tvalid), // input wire s_axis_data_tvalid

.s_axis_data_tready(s_axis_data_tready), // output wire s_axis_data_tready

.s_axis_data_tlast(s_axis_data_tlast), // input wire s_axis_data_tlast

.m_axis_data_tdata(m_axis_data_tdata), // output wire [47 : 0] m_axis_data_tdata

.m_axis_data_tvalid(m_axis_data_tvalid), // output wire m_axis_data_tvalid

.m_axis_data_tready(m_axis_data_tready), // input wire m_axis_data_tready

.m_axis_data_tlast(m_axis_data_tlast), // output wire m_axis_data_tlast

.m_axis_data_tuser(m_axis_data_tuser),//XK_INDEX

.event_frame_started(event_frame_started), // output wire event_frame_started

.event_tlast_unexpected(event_tlast_unexpected), // output wire event_tlast_unexpected

.event_tlast_missing(event_tlast_missing), // output wire event_tlast_missing

.event_status_channel_halt(event_status_channel_halt), // output wire event_status_channel_halt

.event_data_in_channel_halt(event_data_in_channel_halt), // output wire event_data_in_channel_halt

.event_data_out_channel_halt(event_data_out_channel_halt) // output wire event_data_out_channel_halt

);

initial begin

// Initialize Inputs

aclk = 0;

aresetn = 0;

s_axis_config_tvalid = 0;

s_axis_config_tdata = 0;

s_axis_data_tvalid = 0;

s_axis_data_tdata = 0;

s_axis_data_tlast = 0;

m_axis_data_tready = 0;

// Wait 150 ns for global reset to finish

#150;

aresetn = 1;

m_axis_data_tready = 1;

s_axis_config_tvalid = 1;

//s_axis_config_tdata = 16'b10110101011; // 512points bit0-9 sclae_sch bit10 fwd/ivs 这样配置不对 FFT desired (and not IFFT

//s_axis_config_tdata = 16'b01101010111; // 512points bit1-10 sclae_sch bit0 fwd/ivs 按这组数据配置结果缩小了1000倍 FFT desired (and not IFFT

//s_axis_config_tdata = 16'b00000000001; // 512points result 与下一种情况一致

s_axis_config_tdata = 1'b1; // 配置fwd 512 or 1024 points 配置unscale 情况 位宽有进位 输出位宽要对应 结果正确正确!!!!!

//s_axis_config_tdata = 16'b1101101010111;//4096points bit1-12 sclae_sch bit0 fwd/ivs

//s_axis_data_tlast = 1;

s_axis_data_tdata = 48'h000000;

s_axis_data_tvalid = 0;

#10

s_axis_config_tvalid = 0;

begin

for(i=0;i<1024;i=i+1) begin

#10

s_axis_data_tvalid <= 1;

s_axis_data_tdata <= {{24'h000000},mem0_re[i]};

$display("mem_a[%d] = %h", i, mem0_re[i]);

end

end

assign XK_RE = m_axis_data_tdata[39:0];

assign XK_IM = m_axis_data_tdata[79:40];

#10;

s_axis_data_tdata = 48'h000000;

s_axis_data_tvalid = 0;

#400000 $finish;

end

endmodule

/*test smaple 1 N=8 (?????s_axis_config_tdata = 8'b00000001);

s_axis_data_tdata =[1.1 2.1 3.1 4.1 5.1 6.1 7.1 8.1] 16位定点小数

s_axis_data_tdata =[1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a] 16位定点小数

vivado_result 00000024ccd0 09a820fc0000 040000fc0000 01a820fc0000 000000fc0000 fe57e0fc0000 fc0000fc0000 f657e0fc0000

matlab_result 36.8000+0.0000i -4.0000+9.6569i -4.0000+4.0000i -4.0000+1.6569i -4.0000+0.0000i -4.0000-1.6569i -4.0000-4.0000i -4.0000-9.6569i

s_axis_config_tdata = 8'b00000000或者不配置

vivado_result 00000024ccd0 f657e0fc0000 fc0000fc0000 fe57e0fc0000 000000fc0000 01a820fc0000 040000fc0000 09a820fc0000

compare result right!!!!!

*/

/*test sample 2 N=16 (?????s_axis_config_tdata = 8'b00000001);

s_axis_data_tdata =[1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a] 16点 16位定点小数

vivado_result 0000004999a0 000000000000 135040f80000 000000000000 080000f80000 000000000000 035040f80000 000000000000 000000f80000 000000000000 fcafc0f80000 000000000000 f80000f80000 000000000000 ecafc0f80000 000000000000

matlab_result 73.6000+0.0000i 0.0000+0.0000i -8.0000+19.3137i 0.0000+0.0000i -8.0000+8.0000i 0.0000+0.0000i -8.0000+3.3137i 0.0000+0.0000i -8.0000+0.0000i 0.0000+0.0000i -8.0000-3.3137i 0.0000+0.0000i -8.0000-8.0000i 0.0000+0.0000i -8.0000-19.3137i 0.0000+0.0000i

compare result right!!!!!

*/

/*test sample 3 N=128 (s_axis_config_tdata = 16'b0000000000000001;error )

s_axis_config_tdata = 16'b0101010101010101;error

s_axis_data_tdata =[1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a]*8 16位定点小数

*/

*****注:其中输入数据"D:/fpga/fft1/stimulus0_24bit.dat"为16位定点小数如下:

1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a

1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a

1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a

1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a

1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a

1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a

1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a

1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a 1199a 2199a 3199a 4199a 5199a 6199a 7199a 8199a

Vivado simulation result 如图所示:

图5

将上述输入数据转换成16为定点小数为a=[1.1 2.1 3.1 4.1 5.1 6.1 7.1 8.1……..] b=fft(a) MATLAB仿真结果如图:

图6

对比图5、图6可知结果保持一致。

二、配置IP核实现ifft转换

Testbench 代码如下:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: zyp

//

// Create Date: 04/21/2017 08:35:42 PM

// Design Name:

// Module Name: test

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

// 对512点做ifft变换

// 512样本数据来自【1.1 2.1 3.1 4.1 5.1 6.1 7.1 8.1......】的fft转换结果

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module testbench_ifft();

//ifft_0信号

// Inputs

reg aclk;

reg aresetn;//active low

reg rst;

reg s_axis_config_tvalid;

reg s_axis_data_tvalid;

reg s_axis_data_tlast;

reg m_axis_data_tready;

reg [7:0] s_axis_config_tdata;

reg [63: 0] s_axis_data_tdata;

// Outputs

wire s_axis_config_tready;

wire s_axis_data_tready;

wire m_axis_data_tvalid;

wire m_axis_data_tlast;

wire event_frame_started;

wire event_tlast_unexpected;

wire event_tlast_missing;

wire event_status_channel_halt;

wire event_data_in_channel_halt;

wire event_data_out_channel_halt;

wire [95:0] m_axis_data_tdata; //un_scaled

wire [15:0] m_axis_data_tuser;

reg[47:0] XK_RE;//ceshi xianshi

reg[47:0] XK_IM;//ceshi xianshi

reg[23:0] mem0_re[0:4095];

reg[63:0] mem3_re[0:511];//高40位是虚部 34位为有效 低40位是实部 34位有效 16位定点小数

reg[23:0] mem1_re[0:7];

reg[23:0] mem2_re[0:7];

initial $readmemh("D:/fpga/fft1/stimulus0_24bit.dat",mem0_re);

initial $readmemh("D:/fpga/fft1/stimulus1_24bit.dat",mem1_re);

initial $readmemh("D:/fpga/fft1/stimulus2_24bit.dat",mem2_re);

initial $readmemh("D:/fpga/fft1/stimulus3_80bit.dat",mem3_re);

reg[7:0] op_sample= 0;

reg op_sample_first = 1;

reg[7:0] ip_frame=0;

reg[7:0] op_frame=0;

integer i;

reg[11:0] cnt;

// generate clk

always #5 aclk =! aclk;

ifft_0 ifft_m0 (

.aclk(aclk), // input wire aclk

// .aresetn(aresetn),

.s_axis_config_tdata(s_axis_config_tdata), // input wire [7 : 0] s_axis_config_tdata

.s_axis_config_tvalid(s_axis_config_tvalid), // input wire s_axis_config_tvalid

.s_axis_config_tready(s_axis_config_tready), // output wire s_axis_config_tready

.s_axis_data_tdata(s_axis_data_tdata), // input wire [47 : 0] s_axis_data_tdata

.s_axis_data_tvalid(s_axis_data_tvalid), // input wire s_axis_data_tvalid

.s_axis_data_tready(s_axis_data_tready), // output wire s_axis_data_tready

.s_axis_data_tlast(s_axis_data_tlast), // input wire s_axis_data_tlast

.m_axis_data_tdata(m_axis_data_tdata), // output wire [47 : 0] m_axis_data_tdata

.m_axis_data_tvalid(m_axis_data_tvalid), // output wire m_axis_data_tvalid

.m_axis_data_tready(m_axis_data_tready), // input wire m_axis_data_tready

.m_axis_data_tlast(m_axis_data_tlast), // output wire m_axis_data_tlast

.m_axis_data_tuser(m_axis_data_tuser), //XK_INDEX

.event_frame_started(event_frame_started), // output wire event_frame_started

.event_tlast_unexpected(event_tlast_unexpected), // output wire event_tlast_unexpected

.event_tlast_missing(event_tlast_missing), // output wire event_tlast_missing

.event_status_channel_halt(event_status_channel_halt), // output wire event_status_channel_halt

.event_data_in_channel_halt(event_data_in_channel_halt), // output wire event_data_in_channel_halt

.event_data_out_channel_halt(event_data_out_channel_halt) // output wire event_data_out_channel_halt

);

initial begin

// Initialize Inputs

aclk = 0;

rst = 1;

s_axis_config_tvalid = 0;

s_axis_config_tdata = 0;

s_axis_data_tvalid = 0;

s_axis_data_tdata = 0;

s_axis_data_tlast = 0;

m_axis_data_tready = 0;

#150;

rst = 0;

m_axis_data_tready = 1;

s_axis_config_tvalid = 1;

s_axis_config_tdata = 1'b0; // 配置invs 512 or 1024 points 配置unscale 情况 位宽有进位 输出位宽要对应 结果正确正确!!!!!

s_axis_data_tdata = 64'h000000;

s_axis_data_tvalid = 0;

//#10

//s_axis_config_tvalid = 0;

begin

for(i=0;i<512;i=i+1) begin

#10

s_axis_data_tvalid <= 1;

s_axis_data_tdata <= {mem3_re[i]};

$display("mem_a[%d] = %h", i, mem3_re[i]);

end

end

assign XK_RE = m_axis_data_tdata[31:0];

assign XK_IM = m_axis_data_tdata[79:48];

#10;

s_axis_data_tdata = 64'h000000;

s_axis_data_tvalid = 0;

/*

#100;

begin

for(i=0;i<512;i=i+1) begin

#10

s_axis_data_tvalid <= 1;

s_axis_data_tdata <= {mem2_re[i]};

$display("mem_a[%d] = %h", i, mem2_re[i]);

end

#10;

s_axis_data_tdata = 64'h000000;

s_axis_data_tvalid = 0;

end

*/

#20000 $finish;

end

endmodule

样本文件是

0000000009333400 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 026a0800ff000000 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 01000000ff000000 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 006a0800ff000000 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 00000000ff000000 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 ff95f800ff000000 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 ff000000ff000000 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 fd95f800ff000000 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

(以上是1.1 1.2.....1.8的512个数据的fft转换结果)

0000000000e66680 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 003dcdb6ffe66680 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 00199980ffe66680 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 000a9ab6ffe66680 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 00000000ffe66680 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 fff5654affe66680 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 ffe66680ffe66680 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 ffc2324affe66680 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

(以上是0.1 0.2.....0.8的512个数据的fft转换结果)

****注:ifft的转换结果需要除以转换长度N才能得到正确的结果;

注:在配置时output order要勾选nature order 不然输出结果时序是乱掉的;