FPGA+DSP的高速AD采集处理开发详解

1

案例说明

1. Kintex-7 FPGA使用SRIO IP核作为Initiator,通过AD9613模块采集AD数据。AD9613采样率为250MSPS,双通道12bit,12bit按照16bit发送,因此数据量为16bit * 2 * 250M = 8Gbps;

2. AD数据通过SRIO由Kintex-7发送到C6678 DSP(Target)的0x0C3F0000~0x0C3F7FFF的地址空间,数据量为32KByte,使用SWRITE方式,期间每传16KByte数据后就发送一个DOORBELL信息,让C6678做乒乓处理。Kintex-7通过SRIO与C6678连接,共4个lane,每个lane的通信速率为5Gbps,数据有效带宽为20Gbps * 80% = 16Gbps;

3. 采集到的AD数据可分别通过Xilinx Vivado和TI CCS软件查看波形,并在C6678做FFT处理。

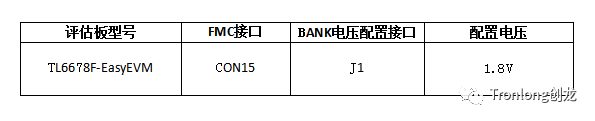

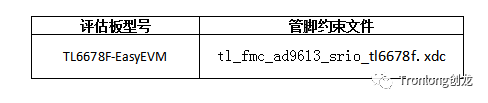

此开发案例基于创龙Kintex-7+C6678评估板TL6678F-EasyEVM展开。

AD采集处理案例视频

2

案例框图

3

案例演示

硬件连接

(1) 将创龙AD9613高速AD模块TL9613/9706F(此模块集成高速DA,DA芯片为AD9706)通过FMC接口与评估板连接。

(2) 信号发生器设置成两路正弦波输出,幅度设置:1.5Vpp以及无直流偏置,频率设置:1MHz。

(3) 信号发生器的两路输出分别连接到模块的ADC_CHA、ADC_CHB。

1.FPGA端

参考TL6678F-EasyEVM评估板光盘用户手册《基于下载器的程序固化与加载》文档中“Vivado下bit文件加载步骤”章节,将tl_fmc_ad9613_srio_tl6678f_xc7k325t.bit文件烧录到FPGA。烧写bit文件时,指定调试文件tl_fmc_ad9613_srio_tl6678f_xc7k325t.ltx,可以观察到ILA调试信号,查看ADC采样波形。

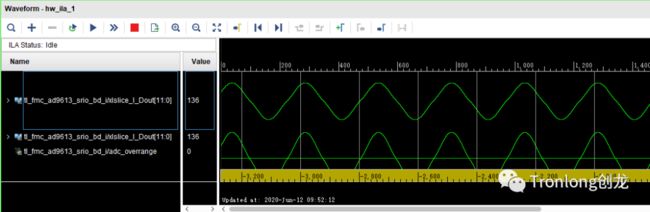

ADC两路信号在ILA内嵌逻辑分析仪中均设置为有符号数、模拟波形显示,如下图所示:

ILA触发抓取两路ADC采样波形,如下图所示(两路正弦波形):

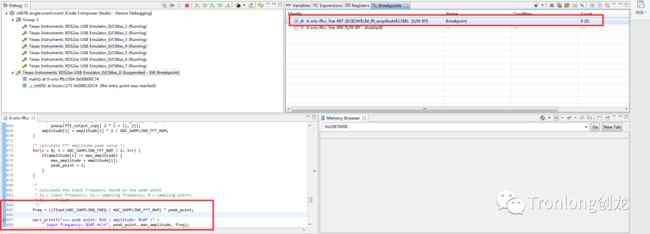

2.DSP端

参考TL6678F-EasyEVM评估板光盘用户手册《CCS工程的生成与加载》文档,在“tl-fmc-ad9613-srio/DSP/src”目录下建立CCS工程并导入到CCS软件中编译生成tl-srio-fft.out文件,通过仿真器加载tl-srio-fft.out文件到DSP端。将tl-srio-fft.out下载到C6678 Core0 ~ Core7核中,在tl-srio-fft.c窗口中红色框标注的地方创建breakpoint,使DSP程序运行后能暂停,如下图所示:

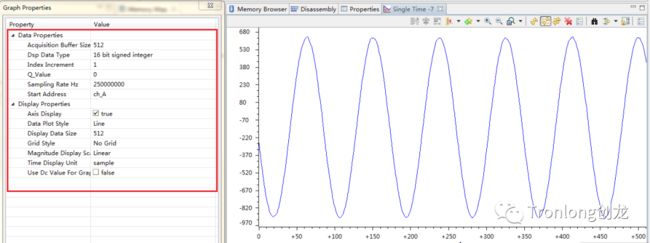

因为Core0负责系统初始化,为确保其他核跟Core0是同步开始传输,所以Core0核最后运行(Core0核可查看原始波形以及振幅波形,其他核仅可查看原始波形)。运行程序,DSP程序正常暂停,可通过图像波形形式查看数据,使用Graph工具,输入下述配置,查看Channel A波形数据。

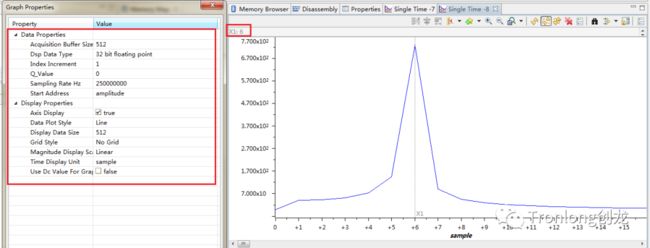

输入下图配置,查看Channel A经过FFT振幅波形。

若出现波形显示不正常或没有波形产生,请参考以下操作:

1.请确保已正常加载GEL文件。

2.请确保Breakpoint设置成功,DSP程序能够暂停。

3.请硬件断电重启后重新烧写FPGA和DSP程序。

频率计算

FFT变换点数N=512,AD采样率Fs为250MSPS。某点n所表示的频率为:Fn=n*(Fs/N) (n >=0)。当n=0时,Fn为0,因为第一点表示的是直流分量,所以频率为0,幅值也为0,因为该正弦波没有直流分量。

从上面的FFT振幅波形图中可以看出,Channel A在第6个点处有信号,所以对应的频率为Fn = 6 * (Fs/N) = 6 * 250MHz / 512 = 2.9296875 MHz。对应原始信号3MHz。

此处存在误差,目前采样点为512个,一个点表示Fs/N= 488.281KHZ,所以如果需要提高精度,用户可以提高采样点。

通过查看串口输入数据,也可查看处理结果。其中peak point代表振幅图峰值点横坐标;amplitude代表振幅图幅值;input frequency根据振幅图计算的输入频率。

4

关键代码说明

1.管脚约束

例程管脚约束文件位于Vivado工程“src\constraints”目录下。

2.FPGA端的代码

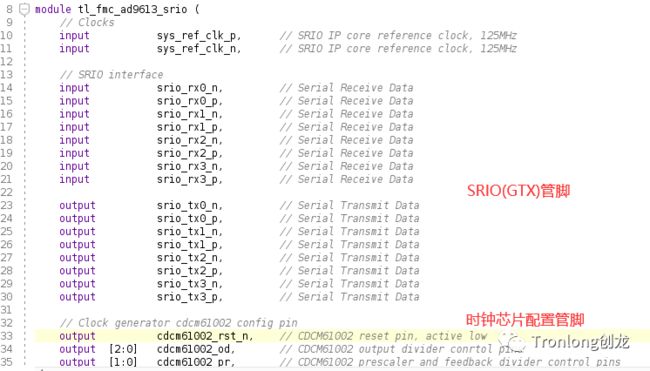

顶层文件tl_fmc_ad9613_srio.v的主要功能:

(1)端口定义。

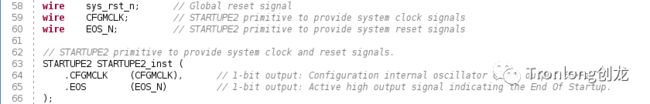

(2)使用STARTUPE2原语提供的EOS作为系统复位信号,使用STARTUPE2原语提供的内部65MHz时钟CFGMCLK作为系统时钟。

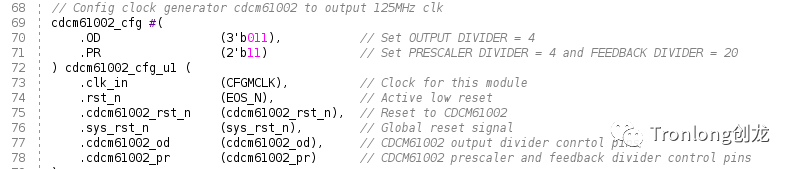

(3)配置时钟芯片,输出125MHz的参考时钟为SRIO IP核。

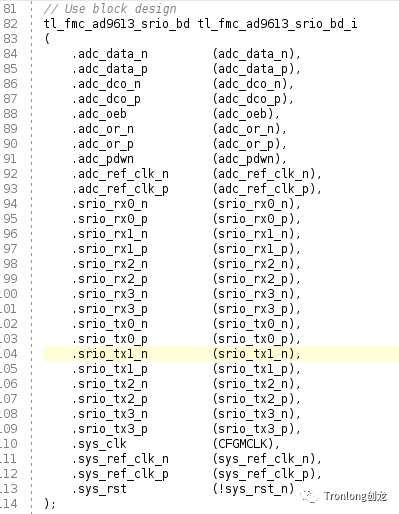

(4)调试Block design。

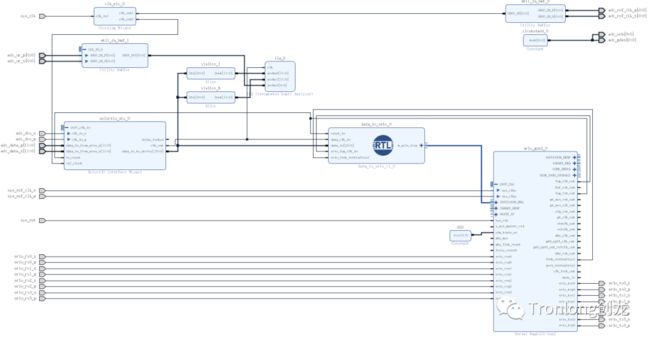

可以查看生成的RTL原理图:

3.DSP端的代码

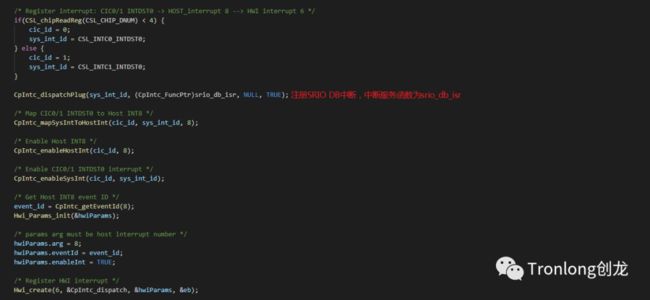

(1)main函数初始化srio子系统,hwi中断注册。

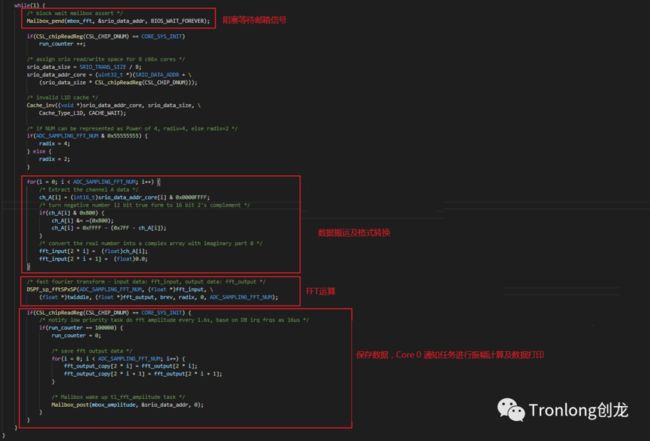

(2)srio_db_isr响应srio doorbell中断,以邮箱方式通知Core0 ~ Core7核同时进行FFT运算。

(3)tl_srio_fft任务等待邮箱信号,Core0 ~ Core7核同时进行FFT运算。

(4)tl_fft_amplitude任务等待信号量置位,Core0核进行FFT振幅运算,通过串口打印数据处理结果。

5

Block Design说明

Block Design如下

1.Select IO IP核配置说明

参考TL6678F-EasyEVM评估板光盘tl-fmc-ad9613例程的IP核与模块介绍章节。

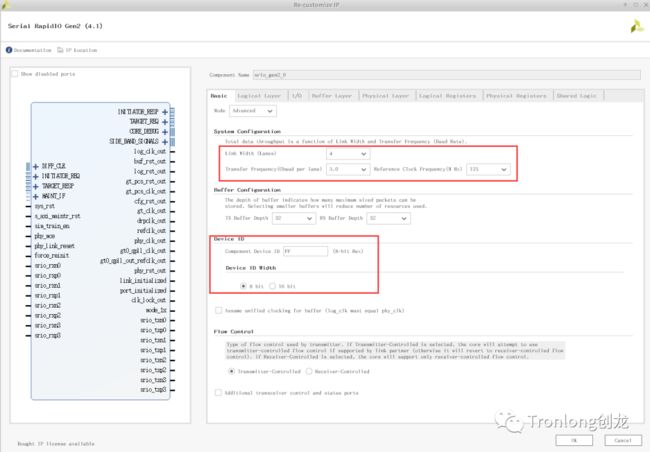

2.SRIO IP配置说明

SRIO链路宽度设置为4个lane,通信频率为5Gbps(即每个lane均为5Gbps),参考时钟为125MHz;设置8bit位宽的ID,且ID=0xFF。

Port I/O Style选择为Initiator/Target模式,其中Condensed I/O接收和发送均使用一个AXI4-Stream通道,Initiator/Target接收和发送采用不同的AXI4-Stream通道。

I/O Format:I/O端口配置使用HELLO格式包。

其他参数保持保持默认值即可。

更详细说明请查阅IP核手册:《pg007_srio_gen2.pdf》。

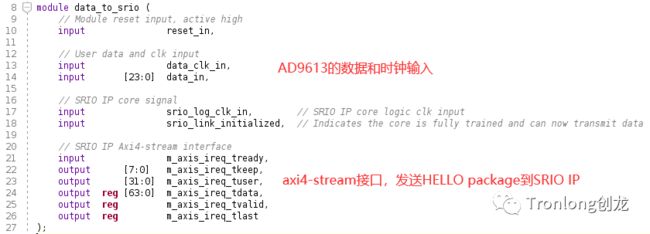

3.data_to_srio RTL模块功能

(1)连续不停地将AD9613采集的数据写入FIFO。

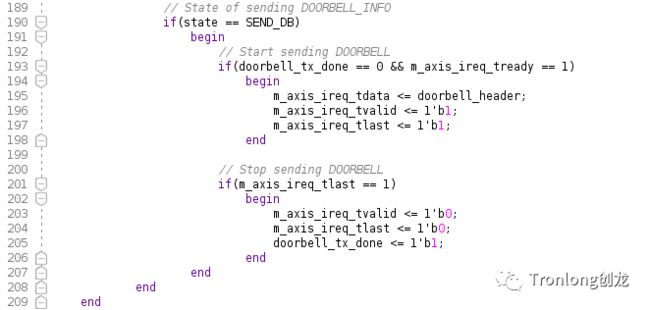

(2)控制FIFO读操作,每次从FIFO读取完指定的数据并通过AXI4-stream接口传输到SRIO IP。其中本例程每发送16KByte的数据就发送一个DOORBELL信息,通知Target(DSP)对数据做处理。

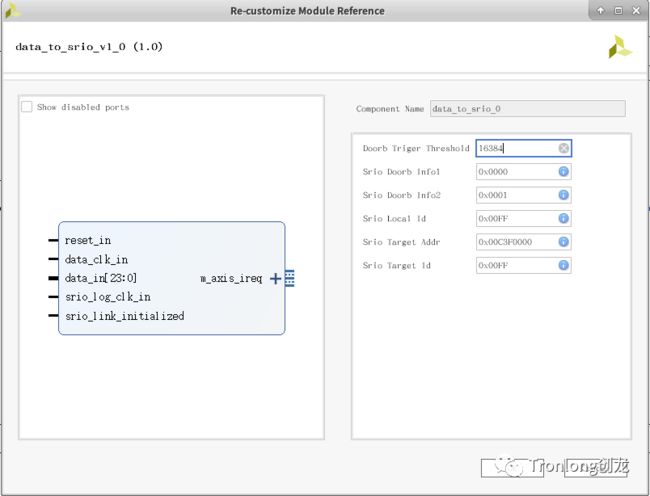

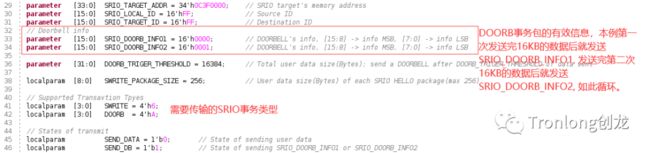

双击block degin中的模块,可配置:

Doorb Triger Threshold: 门铃触发阈值,本例设置为16384Bytes = 16KB,即通过SRIO发送16KB的数据后就发送一个DOORBELL信息。

Srio Doorb info1:发送完Doorb Triger Threshold个字节的数据之后发送的门铃信息。

Srio Doorb info2:发送完2倍的Doorb Triger Threshold个数据之后发送的门铃信息。

Srio Target Addr:SRIO Target的内存地址。(本例设置的为DSP的MSMC地址0x0C3F0000)

Srio Target Id:SRIO Target的ID。

Srio Local Id:SRIO Iitiator的ID。

代码解释

(1)端口定义

(2)FIFO原语

配置FIFO大小为36 Byte,读写数据的位宽为64bit(FIFO深度为512)。

ALMOST_EMPTY_OFFSET和ALMOST_FULL_OFFSET配置为0x20,即32;即当FIFO写入数据个数大于32个,ALMOST_FULL输出高电平。

本例FIFO设置位宽为64bit,所以64bit * 32 / 8 = 256 Byte,即当FIFO写入数据大于256 Byte,ALMOST_FULL会输出高电平。

因为SRIO的package最大有效数据为256 Byte,为了确保SRIO能传输完整的数据包,所以设置FIFO的门限值为256Byte.

FIFO原语详细说明请查阅:《ug473_7Series_Memory_Resources.pdf》。

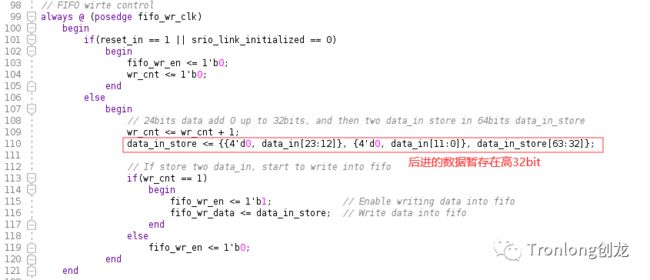

(3)FIFO写控制

因为AD9613输出的AD数据为双通道的24bit,所以分别将两个通道的数据补成16bit。然后保存到data_in_store中。

因为FIFO的位宽64bit,而上个步骤将AD的双通道数据补成了32bit,所以每存够两个32bit的AD数据,凑成64bit的data_in_store,再使能fifo_wr_en信号,把64bit的数据写入FIFO。

后写入的数据存在高32位,发送到SRIO Target端(DSP),方便其按顺序处理数据。

其中wr_cnt为一个1bit,计数只有0和1两个值。

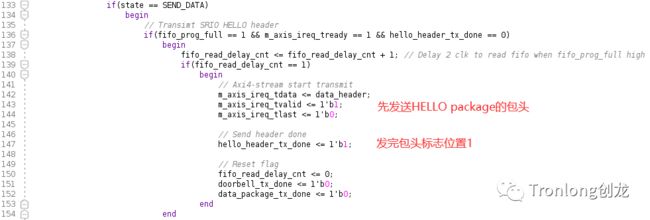

(4)读取FIFO数据并打包HELLO格式发送数据

HELLO包头拼接:

(6)状态切换

本例设置的TOTAL_DATA_SIZE为32KByte,即每发送16KByte的数据包之后发送一个门铃信息。

6

资料下载

点击以下链接或扫描二维码,获取本案例源码及TL6678F-EasyEVM评估板详细资料。

http://site.tronlong.com/pfdownload

TL6678F-EasyEVM评估板

更多推荐

想更多地了解创龙,欢迎与我们联系:

销售邮箱:[email protected]

技术邮箱:[email protected]

创龙总机:020-8998-6280

技术热线:020-3893-9734

创龙官网:www.tronlong.com

技术论坛:www.51ele.net

官方商城:https://tronlong.taobao.com

创龙官网

创龙微信公众号

【长按识别二维码关注我们】