SPI(Serial Peripheral Interface)总线是一种高速、串行、全双工通信总线,由Motorola公司设计并推广。

优点是支持全双工通信,传输速率快,SCLK时钟频率最高可以达到50MHz左右。

缺点是没有流控制机制,不像I2C有应答机制,也不像UART有数据帧校验机制。

总线引脚

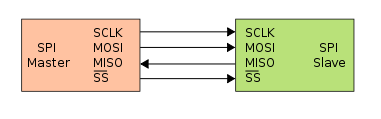

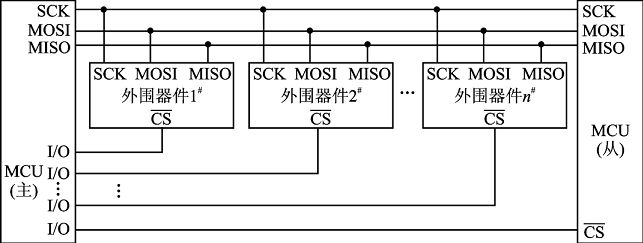

SPI总线以主从方式工作,支持多主多从、单主多从、单主单从模式,拥有四个信号线:

MISO – Master Input Slave Output,主设备数据输入,从设备数据输出;

MOSI – Master Output Slave Input,主设备数据输出,从设备数据输入;

SCLK – Serial Clock,时钟信号,由主设备产生;

需要注意的是,SCLK只有才数据传输的过程中产生时钟周期,不进行数据传输时保持高电平或者低电平;

CS – Chip Select,从设备使能信号,由主设备控制。

其中CS信号线主要用于片选,实际通信使用MISO/MOSI/SCLK三根信号线。

单主单从模式如下:

单主多从模式如下:(每个SPI设备由一根独立的CS片选信号进行片选)

总线时序

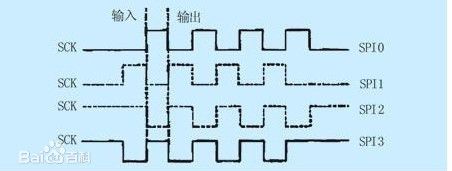

根据CPOL(时钟极性)和CPHA(时钟相位)的组合区分,SPI总线时序有四种模式。SPI通信的双方必须同时工作在其中一种模式下,往往是主控制器匹配SPI设备的工作模式。

Mode0:CPOL=0,CPHA=0

Mode1:CPOL=0,CPHA=1

Mode2:CPOL=1,CPHA=0

Mode3:CPOL=1,CPHA=1

其中SPI 0和SPI 3两种模式最常用。

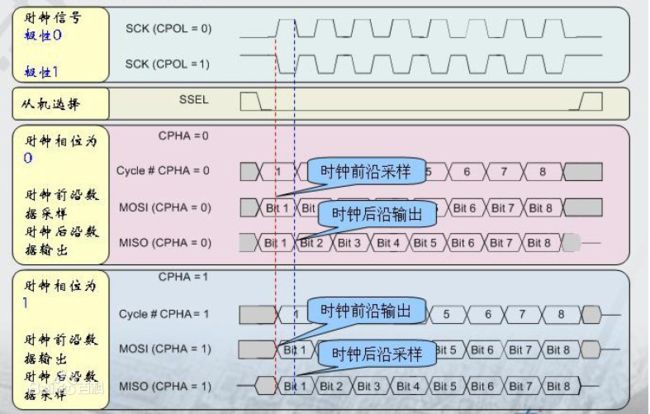

CPOL用来控制SCLK信号的Active状态是高电平还是低电平。

0 - SCLK高电平为Active状态

1 - SCLK低电平为Active状态

CPHA用来控制MOSI和MISO在第几个SCLK边沿进行数据采样。

0 - 第一个SCLK边沿采样,第二个边沿发送

1 - 第一个SCLK边沿发送,第二个边沿采样

总结:

SPI总线协议本身并不复杂,这就意味着复杂性在SPI设备驱动的软件编码上,具体体现在:

1)SPI总线协议没有数据校验机制,因此,必须根据SPI设备支持的SCLK时钟频率范围设置SPI时钟频率;

2)SPI控制器的发送是直接将数据写入一个移位寄存器中,该移位寄存器跟随SCLK时钟发送数据;SPI控制器的接收与发送同步进行,也就是说发送数据的同时,也在接收数据,而接收数据是写入一个缓存寄存器中,如果缓存寄存器的值不及时读取的话,后续接收的数据会直接丢弃而不是覆盖到该缓存寄存器中,因此,每一次写数据之后,一定要读取数据,即使读取的数据无意义。

3)SPI设备往往不会主动发送数据,而是被动应答;而SPI总线只有在主机发送数据的时候才会产生SCLK时钟周期信号,因此,往往读数据时,需要主机往SPI总线上发送任意数据;

4)SPI设备往往需要特定的时序进行操作,而不能像RAM一样随机读写,比如MMC/SDCard;