armv8 ARM64 AARCH64

在除夕之前,想写点东西给各位参考,呵呵~

最近在制作iOS版的CPU Dasher64,针对64位ARMv8架构。ARMv8架构与ARMv7架构比起来,变化非常大。Intel IA-32与Intel64的差别其实不大,基本上就是每条指令多了REX前缀而已~

从可用寄存器角度来说,程序员可以完全使用31个通用寄存器(X0-X30或W0-W30),而堆栈指针寄存器(SP或WSP)以及指令指针寄存器IP都是独立的,这个与32位的不同(R13为堆栈指针寄存器,R15作为指令指针寄存器)。对于ARM官方提供的调用约定,参数可以用8个寄存器(X0-X7或W0-W7)。这意味着64位下,即便传8个参数都能进寄存器,呵呵。而需要被当前例程所保护的通用寄存器是从X18到X30。不过少了原来的push/pop指令,原来的push能一次将几乎所有通用寄存器保存到栈上。现在如果要保存通用寄存器到栈上的话一般使用LDP/STP指令对SP操作,这样可以同时加载/存储两个64位寄存器。用这对指令同时也能确保栈地址始终能16字节对齐。

而对于SIMD寄存器以及浮点寄存器来说,除了标量单精度与双精度寄存器的数量不变以为(它俩仍然与SIMD寄存器共享),SIMD寄存器由原先32位下的16个扩充到了32个。在32位下,需要被保护的SIMD寄存器是Q4-Q7这四个,而64位下,需要被当前例程所保护的SIMD寄存器是V8-V15。

从ISA角度上来说,原本32位下有很强悍的几乎每条指令都带条件操作的特性完全木有了~留下几条含有前缀C的比较简单常用的操作,比如CCMP、CSEL、CINC、CINV等。不过像算术逻辑操作仍然有不改变当前标志位与改变当前标志位两种版本,这点还是很不错的。在64位下,Thumb指令集全都木有了,所有指令都是32位宽。因此立即数与ARMv7比起来,除了移位还算正常,其它的都显得有些奇葩。

不过ARMv8在存储器控制器上下了不少功夫,增加了x86下的类似于MOVNT这种指令,Non-temporal load/store——LDNP/STNP。这就使得像原先的Memory Barrier系操作有了用武之地了~ARMv8中除了原有的ISB(Instruction Synchronization Barrier)与DMB(Data Memory Barrier)之外,还引入了LDAR/STLR(Load-Acquire/Store-Release)指令集。这套指令具有Memory Barrier的作用。如果你在某一点需要做Memory Barrier,而此时正好想读取或写入某个数据,那么直接用LDAR/STLR即可,可以省去一条DMB的指令。而在多核多线程同步中,又引入了LDXP/STXP操作,由原先的单寄存器扩展到了双寄存器~这堪比CAS2啊~~( http://en.wikipedia.org/wiki/Non-blocking_algorithm)

对于执行状态,现在引入了EL0到EL3,EL表示Exception Level。通常,用户模式为EL0。

不过最后想吐槽的是,ARMv8编程手册似乎是写给外星人看的~很多指令介绍不详细,而且写得很容易让人误解……最后,比较可惜的是Apple A7对ARMv8的实现中,没有将CRC32放进去~而且汇编器压根不识别这系列指令~

《中无通讯》第67期 文︰ 世界网络 www.linkwan.com 林和安 小洛夫

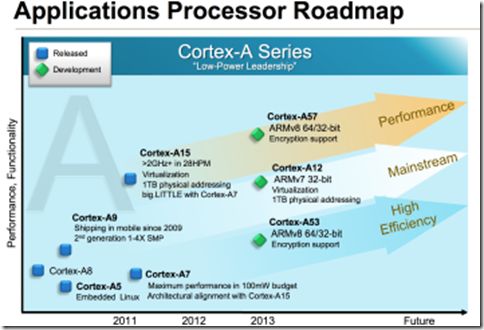

64bit CPU并不是甚么新的事物,服务器/工作站早已是64bit的天下,即使桌面计算机也纷纷升级64bit CPU及64bit操作系统。作为移动设备市场的领导者,ARM也决定在2014年推出64bit ARM CPU架构,实现智能手机、平板计算机的一次性能飞跃,又会为市场带来多大的影响呢?

走向64bit的主因—支持更多内存

ARM架构一向以低功耗作主打,为此不惜把CPU架构尽量作出精简,取消作用不大的单元。早期ARMv4指令为求低功耗,没有FP浮点、复杂math指令及SIMD,十分简陋。随后ARM陆续加上以上的功能,而自Cortex-A9以后,用户要求更高性能的处理器,满足高清影片播放、浏览网页以至多任务工作环境,即在智能手机上同时打开3-4项应 用,占用大量的CPU及内存资源,尤以内存为甚。因为智能手机没有硬盘,大部份的数据都需要从内存中读取,使4GB的寻址上限显得足襟见肘,而且智能手机因为空间有限需要GPU及CPU共享地址空间,与PC的GPU及CPU拥有不同的地址空间不同,无形中增加内存资源的占用。在Cortex-A15发布时,ARM尝试引入Physical Address Extensions技术,把CPU可寻址的空间从32bit扩充至40bit,最大内存寻址从4GB扩充至1TB,暂缓了内存上限问题。不过引入Physical Address Extensions的做法治标不治本,因为Physical Address Extensions是以4KB page mapping即映像的方式支持4GB以上的内存,不但较为复杂而且不能支持单个4GB以上的应用,需把数据拆分处理。另一方面,ARM在引入Cortex-A15的同时加入Virtualization虚拟功能,这又增加对内存的需求,最终步x86后尘走上64bit之路,也十分合理。

在ARM架构的演进中,ARMv8A最大的改变是支持64bit。

并未真正64bit?

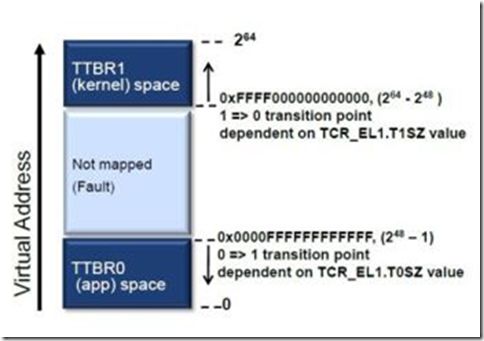

在IT的世界,功能是要付出成本的,所以厂商普遍采用能省便省的做法。ARM引入64bit主要目的是要支持更多内存,为进军服务器、工作站市场作准备。不过ARM也意识到用户未必需要用到64bit上限的16EB内存,所以选择了x86-64的做法,仅支持至48bit Virtual Memory,相当于256TB内存。对于ARM的做法,作为一名计算机爱好者难免有所失望,但考虑到目前主流内存容量在8-16GB左右,加上操作系统如Windows 7 Ultimate也仅支持至192GB,ARM的做法也无可厚非。

全新设计的A64指令集

ARM在2007年已着手设计工作,并于2011年11月公报ARMv8A 64bit指令集架构,耗用了4年的研发时间,时间可谓不过不失。

ARMv8A分为A64及A32两个部分,A64顾名思义属于64bit的部份,主要存在于AARCH64的状态。而A32又称AARCH32状态,用作支持现有A32 ARM指令集。ARM并没有采用AMD x86-64及Intel EM64T扩充32bit指令做法,而是选择全新开发专用的64bit指令。据ARM方面表示,这一做法与省电的考虑有关,当运行64bit ISA时,ARMv7电路可处于闲置状态,节省功耗。同A64 ISA也移除了作用不大的LDM/STM(load/store multiple)指令,改为LD/ST ’P’指令,以降低复杂性及功耗,与此同时,32bit到64bit状态转换采用Inter-processing的做法,确保32bit到64bit指令皆可顺利执行。

新增Registers及支援DP浮点

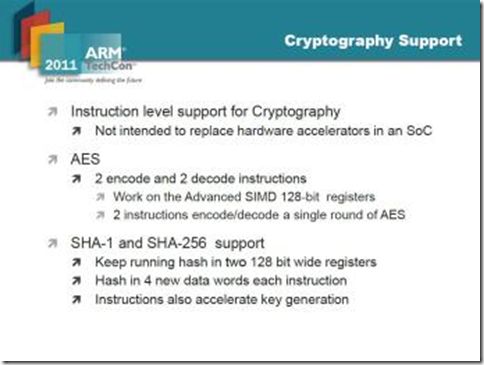

ARMv8A架构新增了31个64bit通用寄存器(General Purpose Registers),改进排程选项以针对复杂软件。同时,还新增32个128bit Registers,用作执行SIMD。ARMv8A除了可执行单精度(Single Precision)FP数据外,新增支持双精度(Double Precision)FP数据,而且新增了IEEE754-2008 FP指令,如MaxNum/MinNum等等。此外ARMv8A还把FPU及SIMD变成常设功能,软件不用检测是否有相关功能。提供Cryptography加密指令,而且是以128bit SIMD Registers执行,可在每周期同时执行2个AES encode/decode指令,或4个SHA-1/SHA-256 Hash。

最后,虽然ARMv8A以64bit为主,但对于32bit的AArch32状态也有所加强。如新增的Cryptography及IEEE754-2008 FP指令,Load acquire/store release`等等皆有帮提供32bit下的性能。

新增的31个64bit General Purpose Registers及32个128bit SIMD Registers。

提供Cryptography加密指令,且是在128bit SIMD Registers内进行。

ARMv8A强化了内存管理,Virtual Address及Physical Address从40bit增至48bit,支持更大容量内存