- 有必要获得WHQL测试认证吗,有什么好处?

什么是WHQL认证?WHQL是MicrosoftWindowsHardwareQualityLab的缩写,中文意思是Windows硬件设备质量实验室,主要是对Windows操作系统的兼容性测试,检验硬件产品和驱动程序在windows系统下的兼容性和稳定性。当某一硬件或软件通过WHQL测试时,制造商可以在其产品包装和广告上使用“DesignedforWindows”标志。该标志可以证明硬件或软件已经

- FPGA小白到项目实战:Verilog+Vivado全流程通关指南(附光学类岗位技能映射)

阿牛的药铺

算法移植部署fpga开发verilog

FPGA小白到项目实战:Verilog+Vivado全流程通关指南(附光学类岗位技能映射)引言:为什么这个FPGA入门路线能帮你快速上岗?本文设计了一条**"Verilog语法→工具链操作→光学项目实战→岗位技能对标"的阶梯式学习路径。不同于泛泛而谈的FPGA教程,我们聚焦光学类产品开发**核心能力(时序接口设计、图像处理算法移植、高速接口应用),通过3个递进式项目(从LED闪烁到图像边缘检测),

- PyTorch & TensorFlow速成复习:从基础语法到模型部署实战(附FPGA移植衔接)

阿牛的药铺

算法移植部署pytorchtensorflowfpga开发

PyTorch&TensorFlow速成复习:从基础语法到模型部署实战(附FPGA移植衔接)引言:为什么算法移植工程师必须掌握框架基础?针对光学类产品算法FPGA移植岗位需求(如可见光/红外图像处理),深度学习框架是算法落地的"桥梁"——既要用PyTorch/TensorFlow验证算法可行性,又要将训练好的模型(如CNN、目标检测)转换为FPGA可部署的格式(ONNX、TFLite)。本文采用"

- windows安装pnpm后报错:pnpm : 无法将“pnpm”项识别为 cmdlet、函数、脚本文件或可运行程序的名称。

Ithao2

Vuenpm前端node.js

使用npm方式安装pnpm,命令如下:npminstall-gpnpm安装完以后,执行pnpm-v查看版本号:pnpm-v执行完发现报错:pnpm:无法将“pnpm”项识别为cmdlet、函数、脚本文件或可运行程序的名称。尝试配置环境变量,重启后均不生效。解决方案:使用PowerShell进行安装1.以管理员用户打开PowerShell,执行如下命令:iwrhttps://get.pnpm.io/

- 【AI大模型学习路线】第三阶段之RAG与LangChain——第十六章(Advanced RAG[1])基于历史对话重新生成Query?

985小水博一枚呀

AI大模型学习路线人工智能学习langchainRAG

【AI大模型学习路线】第三阶段之RAG与LangChain——第十六章(AdvancedRAG[1])基于历史对话重新生成Query?【AI大模型学习路线】第三阶段之RAG与LangChain——第十六章(AdvancedRAG[1])基于历史对话重新生成Query?文章目录【AI大模型学习路线】第三阶段之RAG与LangChain——第十六章(AdvancedRAG[1])基于历史对话重新生成Q

- 【AI大模型学习路线】第三阶段之RAG与LangChain——第十六章(Advanced RAG[1])其他Query优化相关策略?

985小水博一枚呀

AI大模型学习路线人工智能学习langchain

【AI大模型学习路线】第三阶段之RAG与LangChain——第十六章(AdvancedRAG[1])其他Query优化相关策略?【AI大模型学习路线】第三阶段之RAG与LangChain——第十六章(AdvancedRAG[1])其他Query优化相关策略?文章目录【AI大模型学习路线】第三阶段之RAG与LangChain——第十六章(AdvancedRAG[1])其他Query优化相关策略?一

- FPGA 设计中的 “Create HDL Wrapper“ 和 “Generating Output Products“ 的区别

行者..................

fpga开发

CreateHDLWrapper(创建HDL包装器)目的:为顶层设计模块(通常是BlockDesign/IPIntegrator设计)创建一个HDL包装文件功能:将图形化/框图设计的BlockDesign转换为可综合的HDL代码(Verilog或VHDL)创建一个顶层模块,将所有IP核和连接实例化使用场景:当使用IPIntegrator创建BlockDesign后需要将图形化设计转换为HDL代码以

- CMD,PowerShell、Linux/MAC设置环境变量

sky丶Mamba

零基础转大模型应用开发linuxmacos运维

以下是CMD(Windows)、PowerShell(Windows)、Linux/Mac在临时/永久环境变量操作上的对比表格:环境变量操作对照表(CMDvsPowerShellvsLinux/Mac)操作CMD(Windows)PowerShell(Windows)Linux/Mac(Bash/Zsh)设置临时变量setVAR=value$env:VAR="value"exportVAR=val

- RabbitMQ 消息队列:从入门到Spring Boot实战

无糖星轨

rabbitmqspringbootjava

RabbitMQ作为一款开源的、基于AMQP(AdvancedMessageQueuingProtocol)协议实现的消息代理,凭借其强大的功能、灵活的路由机制以及出色的性能,在业界得到了广泛的应用。无论是处理高并发订单、异步通知、日志收集还是系统解耦,RabbitMQ都能发挥其独特的作用。1.RabbitMQ核心概念RabbitMQ的强大功能离不开其背后一系列精心设计的核心概念。理解这些概念是掌

- 使用Adb wifi Android真机运行Uni-app

pony1688

adbuni-appandroid

1、手机安装Adbwifi,我的用是这个:ADBWiFi(com.rair.adbwifi)-5.1.5-应用-酷安2、手机上运行ADB,运行后点击开始后界面如下3、如果手机已root,在电脑上运行adbconnect192.168.200.33:5555就可以连上了(注意:(1)不要进PowerShell,否则报错:无法将“adb”项识别为cmdlet、函数、脚本文件或可运行程序的名称。...(

- STM32与FPGA用FMC进行通讯

weixin_43554366

单片机stm32fpga物联网人工智能

stm32正常按读写SDRAM进行配置,FPGA进行信号采集。FPGA信号采集发现SDWNE是高但H7手册上时序显示是低,造成无法像FPGA模拟的SDRAM无法写入数据FPGA采集信号应该在时钟下降沿,上升沿采集,数据会发生错误。

- Xilinx Vivado开发环境快速导出hdf文件(bat批处理)

XilinxFPGA使用Vivado开发环境创建MicroBlaze软核或ZYNQPS侧SDK逻辑工程时,需要FPGA侧搭建的硬件平台文件,即hdf文件,常规方式是编译完成生成bit流文件后,通过File->Export->ExportHardware菜单来导出,在弹出的菜单再选择要导出的路径和文件名称等,这个过程比较繁琐,通过观察TCL终端窗口:update_compile_order-file

- Xilinx系FPGA学习笔记(三)Vivado的仿真及ILA使用

贾saisai

FPGA学习fpga开发学习笔记

系列文章目录文章目录系列文章目录前言仿真验证(类似modelsim)ILA在线调试工具添加ILAILA的例化ILA的使用前言接着学习vivado的使用方法仿真验证(类似modelsim)首先类似添加.v文件的方法,在File-AddSource中选择Addorcreatesimulationsources或者直接在Sources里面选就行然后就编写testbench,类似之前介绍的modelsim

- 突破传统:Dell R730服务器RAID 5配置与智能监控全解析

芯作者

D2:ubuntu服务器linuxubuntu

在现代数据中心运维中,合理的存储配置是保障业务连续性的基石。今天,我们将深入探索DellPowerEdgeR730服务器的RAID5配置技巧,并结合热备盘策略、自动化监控脚本以及性能调优方案,为您呈现一份别开生面的技术指南。一、为什么RAID5+热备盘是企业级存储的黄金组合?RAID5通过分布式奇偶校验实现数据冗余,允许单块硬盘故障时不丢失数据。其存储效率公式为:Efficiency=\frac{

- Type-C双向C转DP和C转DP带反向供电的解决方案

legendary_螺蛳粉

硬件工程

LDR6500D如何通过Type-C接口实现手机到DP接口的单向视频传输在当今数字化浪潮中,投屏技术作为连接设备、共享视觉内容的桥梁,其重要性日益凸显。PD(PowerDelivery)芯片,特别是集成了Type-C接口与DisplayPort(DP)转换功能的型号,为手机至外设的单向视频传输提供了创新方案。本文将聚焦于LDR6500D如何借助Type-C接口,将手机转变为DP信号源,以连接并驱动

- 什么是ARM架构和Cortex内核?

cykaw2590

单片机MCUarm开发架构

ARM(AdvancedRISCMachine)架构是一种基于精简指令集(RISC,ReducedInstructionSetComputing)的计算机处理器架构,广泛应用于移动设备、嵌入式系统、物联网设备等领域。ARM架构的处理器以其高效的功耗和较低的发热量著称,是目前移动设备中最主流的处理器架构之一。ARM架构的特点高效的功耗:ARM架构设计旨在减少功耗,这对于需要长时间续航的设备非常重要,

- 【AI大模型学习路线】第三阶段之RAG与LangChain——第十六章(Advanced RAG[1])MultiQuery retriever详解?

985小水博一枚呀

AI大模型学习路线人工智能学习langchain

【AI大模型学习路线】第三阶段之RAG与LangChain——第十六章(AdvancedRAG[1])MultiQueryretriever详解?【AI大模型学习路线】第三阶段之RAG与LangChain——第十六章(AdvancedRAG[1])MultiQueryretriever详解?文章目录【AI大模型学习路线】第三阶段之RAG与LangChain——第十六章(AdvancedRAG[1]

- 无需插件就能实现异构数据库的互联互通?(powershell妙用)

潇湘秦

数据库powershelloraclemysqlpostgresql

欢迎关注作者,更多数据库相关安装配置,troubleshooting,调优,备份恢复等资源墨天伦:潇湘秦的个人主页-墨天轮CSDN:潇湘秦-CSDN博客公众号:潇湘秦---------------------------------------------------------------------------------------------前两天在DBA群里有大佬分享了利用OracleD

- 新型BERT勒索软件肆虐:多线程攻击同时针对Windows、Linux及ESXi系统

趋势科技安全分析师发现,一个代号为BERT(内部追踪名WaterPombero)的新型勒索软件组织正在亚洲、欧洲和美国展开多线程攻击。该组织主要针对医疗保健、科技和会展服务行业,其活动范围显示其正成为勒索软件生态中的新兴威胁力量。攻击技术分析在Windows系统中,BERT通过PowerShell加载器(start.ps1)实施攻击,该脚本会执行以下操作:禁用WindowsDefender防火墙和

- 混合云工具沦为隐蔽的远程代码执行与权限提升载体

FreeBuf-

flaskpython后端

通过WAC执行命令时分配的令牌权限|图片来源:IBM混合云管理工具的安全隐患IBMX-Force团队近日对微软AzureArc进行深入研究,发现这款旨在统一本地与云环境的混合云管理工具,可能成为代码执行、权限提升和隐蔽驻留的潜在攻击载体。这项研究始于IBM红队在一次渗透测试中,偶然发现PowerShell脚本中硬编码的Azure服务主体(ServicePrincipal)密钥,进而触发对Azure

- PPT处理控件Aspose.Slides教程:在 C# 中将 ODP 转换为 PPTX

CodeCraft Studio

控件文档管理powerpointc#开发语言AsposePPTodp

您是否正在寻找可靠的PowerPointSDK来以编程方式开发ODP到PPTX转换器?本篇博文演示了如何使用C#将ODP转换为PPTX。ODP是一种基于XML的演示文稿文件,可能包含图像、视频、文本等。但是,将打开的文档演示文稿转换为PowerPoint格式可以提供更好的格式并与MicrosoftPowerPoint兼容。因此,Aspose.Slidesfor.NET提供了丰富的ODP格式到PPT

- Advanced REST Client (ARC) 项目贡献指南与技术架构解析

井章博Church

AdvancedRESTClient(ARC)项目贡献指南与技术架构解析arc-electronAdvancedRESTClient-Desktopapplication项目地址:https://gitcode.com/gh_mirrors/ar/arc-electron项目概述AdvancedRESTClient(ARC)是一个基于Electron构建的开源RESTAPI测试工具,它提供了直观的

- 【FR801xH】富芮坤FR801xH系统函数

沧海一笑-dj

物联网专栏FR801xH富芮坤系统函数富芮坤系统函数FreqchipBLESDK

00.目录文章目录00.目录01.FR801xH概述02.FR801xH功能框图03.Version相关函数3.1get_SDK_compile_date_time04.系统函数4.1system_power_off4.2system_sleep_enable4.3system_sleep_disable4.4system_get_curr_time05.程序示例06.附录01.FR801xH概述

- 在 Windows 系统中,你可以通过以下命令或工具查询占用 8080 端口的程序

青春不流名

eclipse

在Windows系统中,你可以通过以下命令或工具查询占用8080端口的程序:1.使用命令行工具(推荐)打开命令提示符(CMD)或PowerShell,执行以下命令:netstat-ano|findstr:8080输出示例:TCP0.0.0.0:80800.0.0.0:0LISTENING12345UDP[::]:8080[::]:012345其中,12345是进程ID(PID)。2.通过PID查找

- FPGA 47 ,MIG 内存接口生成器深度解析( FPGA 中的 MIG 技术 )

北城笑笑

fpga开发fpga

目录前言一、基础理论1.1MIG介绍1.2结构框架1.2.1主要模块①用户接口层(UserInterfaceLayer)②控制逻辑层(ControLogicLayer)③校准逻辑(CalibrationLogic)④初始化与时序控制(Initialization&TimingControl)⑤物理层接口(PHY–PhysicalLayer)⑥IO引脚驱动(引脚分配与IO配置:Pinout&IOSt

- 缺乏项目进度可视化手段,如何提升展示效果

要提升项目进度的展示效果,需聚焦于选择合适的可视化工具、构建标准化的展示模板、结合数据进行动态更新、明确受众与场景匹配展示内容、推动进度展示与管理系统集成。其中,选择合适的可视化工具最为关键。项目展示效果的好坏,很大程度上取决于所使用工具的表达能力与交互性。选择具备图表支持、实时协作、数据集成能力的工具(如PowerBI、JiraDashboard、ClickUp等),能显著提升项目可视化水平和数

- 基于FPGA的数字密码锁

阿智605

fpga开发notepad++

基于FPGA的数字密码锁顶层文件modulelock(inputclk,//时钟inputrst_n,//复位input[3:0]number_in,//输入inputkey_open1,inputkey_lock1,//inputkey_reset1,outputbeep,//蜂鸣器outputlock_flag,//锁标志位output[3:0]dtube_cs_n,//7段数码管位选信号ou

- 基于FPGA的设计:简易电子密码锁嵌入式实现

程序员杨弋

嵌入式开发fpga开发嵌入式

简介:本文介绍了如何使用FPGA(现场可编程逻辑门阵列)来设计和实现一款简易的电子密码锁。电子密码锁是一种常见的安全访问控制系统,通过输入正确的密码来解锁。嵌入式系统采用FPGA作为核心处理器,结合适当的外设和编程逻辑,能够实现密码输入、验证和控制功能。本文将详细介绍电子密码锁的设计和源代码。设计原理:输入设备:本设计采用数字键盘作为密码输入设备。数字键盘通过FPGA的GPIO(通用输入输出)引脚

- 多通路fpga 通信_FMC与FPGA双口ram通讯

weixin_39796752

多通路fpga通信

硬件环境:ARM+FPGA通过FMC互联,STM32F767和EP4CE15F23I7FMC设置,STM的系统时钟HCLK为216MHz1/*FMCinitializationfunction*/2voidMX_FMC_Init(void)3{4FMC_NORSRAM_TimingTypeDefTiming;56/**PerformtheNOR1memoryinitializationsequen

- [硬件接口]HDMI和DP 区别

DisplayPort和HDMI在FPGA应用场景的实现使用与区别概述DisplayPort(DP)和HDMI是两种主流的数字音视频接口,广泛应用于视频传输场景。在FPGA(现场可编程门阵列)应用中,DP和HDMI常用于视频处理、显示驱动和高带宽数据传输。本文档比较两者在FPGA实现中的使用方式、应用场景及主要区别,并以Markdown格式呈现。1.FPGA实现概述1.1DisplayPort在F

- 对股票分析时要注意哪些主要因素?

会飞的奇葩猪

股票 分析 云掌股吧

众所周知,对散户投资者来说,股票技术分析是应战股市的核心武器,想学好股票的技术分析一定要知道哪些是重点学习的,其实非常简单,我们只要记住三个要素:成交量、价格趋势、振荡指标。

一、成交量

大盘的成交量状态。成交量大说明市场的获利机会较多,成交量小说明市场的获利机会较少。当沪市的成交量超过150亿时是强市市场状态,运用技术找综合买点较准;

- 【Scala十八】视图界定与上下文界定

bit1129

scala

Context Bound,上下文界定,是Scala为隐式参数引入的一种语法糖,使得隐式转换的编码更加简洁。

隐式参数

首先引入一个泛型函数max,用于取a和b的最大值

def max[T](a: T, b: T) = {

if (a > b) a else b

}

因为T是未知类型,只有运行时才会代入真正的类型,因此调用a >

- C语言的分支——Object-C程序设计阅读有感

darkblue086

applec框架cocoa

自从1972年贝尔实验室Dennis Ritchie开发了C语言,C语言已经有了很多版本和实现,从Borland到microsoft还是GNU、Apple都提供了不同时代的多种选择,我们知道C语言是基于Thompson开发的B语言的,Object-C是以SmallTalk-80为基础的。和C++不同的是,Object C并不是C的超集,因为有很多特性与C是不同的。

Object-C程序设计这本书

- 去除浏览器对表单值的记忆

周凡杨

html记忆autocompleteform浏览

&n

- java的树形通讯录

g21121

java

最近用到企业通讯录,虽然以前也开发过,但是用的是jsf,拼成的树形,及其笨重和难维护。后来就想到直接生成json格式字符串,页面上也好展现。

// 首先取出每个部门的联系人

for (int i = 0; i < depList.size(); i++) {

List<Contacts> list = getContactList(depList.get(i

- Nginx安装部署

510888780

nginxlinux

Nginx ("engine x") 是一个高性能的 HTTP 和 反向代理 服务器,也是一个 IMAP/POP3/SMTP 代理服务器。 Nginx 是由 Igor Sysoev 为俄罗斯访问量第二的 Rambler.ru 站点开发的,第一个公开版本0.1.0发布于2004年10月4日。其将源代码以类BSD许可证的形式发布,因它的稳定性、丰富的功能集、示例配置文件和低系统资源

- java servelet异步处理请求

墙头上一根草

java异步返回servlet

servlet3.0以后支持异步处理请求,具体是使用AsyncContext ,包装httpservletRequest以及httpservletResponse具有异步的功能,

final AsyncContext ac = request.startAsync(request, response);

ac.s

- 我的spring学习笔记8-Spring中Bean的实例化

aijuans

Spring 3

在Spring中要实例化一个Bean有几种方法:

1、最常用的(普通方法)

<bean id="myBean" class="www.6e6.org.MyBean" />

使用这样方法,按Spring就会使用Bean的默认构造方法,也就是把没有参数的构造方法来建立Bean实例。

(有构造方法的下个文细说)

2、还

- 为Mysql创建最优的索引

annan211

mysql索引

索引对于良好的性能非常关键,尤其是当数据规模越来越大的时候,索引的对性能的影响越发重要。

索引经常会被误解甚至忽略,而且经常被糟糕的设计。

索引优化应该是对查询性能优化最有效的手段了,索引能够轻易将查询性能提高几个数量级,最优的索引会比

较好的索引性能要好2个数量级。

1 索引的类型

(1) B-Tree

不出意外,这里提到的索引都是指 B-

- 日期函数

百合不是茶

oraclesql日期函数查询

ORACLE日期时间函数大全

TO_DATE格式(以时间:2007-11-02 13:45:25为例)

Year:

yy two digits 两位年 显示值:07

yyy three digits 三位年 显示值:007

- 线程优先级

bijian1013

javathread多线程java多线程

多线程运行时需要定义线程运行的先后顺序。

线程优先级是用数字表示,数字越大线程优先级越高,取值在1到10,默认优先级为5。

实例:

package com.bijian.study;

/**

* 因为在代码段当中把线程B的优先级设置高于线程A,所以运行结果先执行线程B的run()方法后再执行线程A的run()方法

* 但在实际中,JAVA的优先级不准,强烈不建议用此方法来控制执

- 适配器模式和代理模式的区别

bijian1013

java设计模式

一.简介 适配器模式:适配器模式(英语:adapter pattern)有时候也称包装样式或者包装。将一个类的接口转接成用户所期待的。一个适配使得因接口不兼容而不能在一起工作的类工作在一起,做法是将类别自己的接口包裹在一个已存在的类中。 &nbs

- 【持久化框架MyBatis3三】MyBatis3 SQL映射配置文件

bit1129

Mybatis3

SQL映射配置文件一方面类似于Hibernate的映射配置文件,通过定义实体与关系表的列之间的对应关系。另一方面使用<select>,<insert>,<delete>,<update>元素定义增删改查的SQL语句,

这些元素包含三方面内容

1. 要执行的SQL语句

2. SQL语句的入参,比如查询条件

3. SQL语句的返回结果

- oracle大数据表复制备份个人经验

bitcarter

oracle大表备份大表数据复制

前提:

数据库仓库A(就拿oracle11g为例)中有两个用户user1和user2,现在有user1中有表ldm_table1,且表ldm_table1有数据5千万以上,ldm_table1中的数据是从其他库B(数据源)中抽取过来的,前期业务理解不够或者需求有变,数据有变动需要重新从B中抽取数据到A库表ldm_table1中。

- HTTP加速器varnish安装小记

ronin47

http varnish 加速

上午共享的那个varnish安装手册,个人看了下,有点不知所云,好吧~看来还是先安装玩玩!

苦逼公司服务器没法连外网,不能用什么wget或yum命令直接下载安装,每每看到别人博客贴出的在线安装代码时,总有一股羡慕嫉妒“恨”冒了出来。。。好吧,既然没法上外网,那只能麻烦点通过下载源码来编译安装了!

Varnish 3.0.4下载地址: http://repo.varnish-cache.org/

- java-73-输入一个字符串,输出该字符串中对称的子字符串的最大长度

bylijinnan

java

public class LongestSymmtricalLength {

/*

* Q75题目:输入一个字符串,输出该字符串中对称的子字符串的最大长度。

* 比如输入字符串“google”,由于该字符串里最长的对称子字符串是“goog”,因此输出4。

*/

public static void main(String[] args) {

Str

- 学习编程的一点感想

Cb123456

编程感想Gis

写点感想,总结一些,也顺便激励一些自己.现在就是复习阶段,也做做项目.

本专业是GIS专业,当初觉得本专业太水,靠这个会活不下去的,所以就报了培训班。学习的时候,进入状态很慢,而且当初进去的时候,已经上到Java高级阶段了,所以.....,呵呵,之后有点感觉了,不过,还是不好好写代码,还眼高手低的,有

- [能源与安全]美国与中国

comsci

能源

现在有一个局面:地球上的石油只剩下N桶,这些油只够让中国和美国这两个国家中的一个顺利过渡到宇宙时代,但是如果这两个国家为争夺这些石油而发生战争,其结果是两个国家都无法平稳过渡到宇宙时代。。。。而且在战争中,剩下的石油也会被快速消耗在战争中,结果是两败俱伤。。。

在这个大

- SEMI-JOIN执行计划突然变成HASH JOIN了 的原因分析

cwqcwqmax9

oracle

甲说:

A B两个表总数据量都很大,在百万以上。

idx1 idx2字段表示是索引字段

A B 两表上都有

col1字段表示普通字段

select xxx from A

where A.idx1 between mmm and nnn

and exists (select 1 from B where B.idx2 =

- SpringMVC-ajax返回值乱码解决方案

dashuaifu

AjaxspringMVCresponse中文乱码

SpringMVC-ajax返回值乱码解决方案

一:(自己总结,测试过可行)

ajax返回如果含有中文汉字,则使用:(如下例:)

@RequestMapping(value="/xxx.do") public @ResponseBody void getPunishReasonB

- Linux系统中查看日志的常用命令

dcj3sjt126com

OS

因为在日常的工作中,出问题的时候查看日志是每个管理员的习惯,作为初学者,为了以后的需要,我今天将下面这些查看命令共享给各位

cat

tail -f

日 志 文 件 说 明

/var/log/message 系统启动后的信息和错误日志,是Red Hat Linux中最常用的日志之一

/var/log/secure 与安全相关的日志信息

/var/log/maillog 与邮件相关的日志信

- [应用结构]应用

dcj3sjt126com

PHPyii2

应用主体

应用主体是管理 Yii 应用系统整体结构和生命周期的对象。 每个Yii应用系统只能包含一个应用主体,应用主体在 入口脚本中创建并能通过表达式 \Yii::$app 全局范围内访问。

补充: 当我们说"一个应用",它可能是一个应用主体对象,也可能是一个应用系统,是根据上下文来决定[译:中文为避免歧义,Application翻译为应

- assertThat用法

eksliang

JUnitassertThat

junit4.0 assertThat用法

一般匹配符1、assertThat( testedNumber, allOf( greaterThan(8), lessThan(16) ) );

注释: allOf匹配符表明如果接下来的所有条件必须都成立测试才通过,相当于“与”(&&)

2、assertThat( testedNumber, anyOf( g

- android点滴2

gundumw100

应用服务器android网络应用OSHTC

如何让Drawable绕着中心旋转?

Animation a = new RotateAnimation(0.0f, 360.0f,

Animation.RELATIVE_TO_SELF, 0.5f, Animation.RELATIVE_TO_SELF,0.5f);

a.setRepeatCount(-1);

a.setDuration(1000);

如何控制Andro

- 超简洁的CSS下拉菜单

ini

htmlWeb工作html5css

效果体验:http://hovertree.com/texiao/css/3.htmHTML文件:

<!DOCTYPE html>

<html xmlns="http://www.w3.org/1999/xhtml">

<head>

<title>简洁的HTML+CSS下拉菜单-HoverTree</title>

- kafka consumer防止数据丢失

kane_xie

kafkaoffset commit

kafka最初是被LinkedIn设计用来处理log的分布式消息系统,因此它的着眼点不在数据的安全性(log偶尔丢几条无所谓),换句话说kafka并不能完全保证数据不丢失。

尽管kafka官网声称能够保证at-least-once,但如果consumer进程数小于partition_num,这个结论不一定成立。

考虑这样一个case,partiton_num=2

- @Repository、@Service、@Controller 和 @Component

mhtbbx

DAOspringbeanprototype

@Repository、@Service、@Controller 和 @Component 将类标识为Bean

Spring 自 2.0 版本开始,陆续引入了一些注解用于简化 Spring 的开发。@Repository注解便属于最先引入的一批,它用于将数据访问层 (DAO 层 ) 的类标识为 Spring Bean。具体只需将该注解标注在 DAO类上即可。同时,为了让 Spring 能够扫描类

- java 多线程高并发读写控制 误区

qifeifei

java thread

先看一下下面的错误代码,对写加了synchronized控制,保证了写的安全,但是问题在哪里呢?

public class testTh7 {

private String data;

public String read(){

System.out.println(Thread.currentThread().getName() + "read data "

- mongodb replica set(副本集)设置步骤

tcrct

javamongodb

网上已经有一大堆的设置步骤的了,根据我遇到的问题,整理一下,如下:

首先先去下载一个mongodb最新版,目前最新版应该是2.6

cd /usr/local/bin

wget http://fastdl.mongodb.org/linux/mongodb-linux-x86_64-2.6.0.tgz

tar -zxvf mongodb-linux-x86_64-2.6.0.t

- rust学习笔记

wudixiaotie

学习笔记

1.rust里绑定变量是let,默认绑定了的变量是不可更改的,所以如果想让变量可变就要加上mut。

let x = 1; let mut y = 2;

2.match 相当于erlang中的case,但是case的每一项后都是分号,但是rust的match却是逗号。

3.match 的每一项最后都要加逗号,但是最后一项不加也不会报错,所有结尾加逗号的用法都是类似。

4.每个语句结尾都要加分

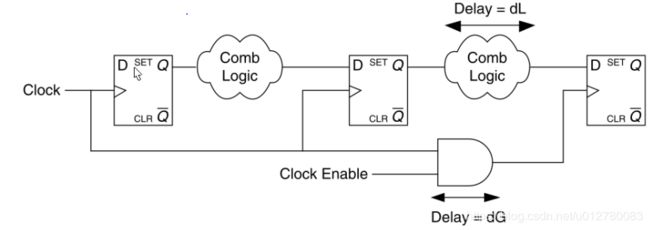

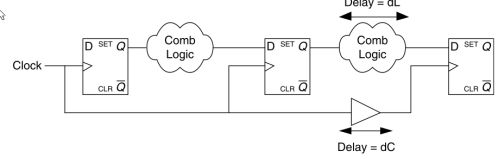

如图组合逻辑中的延迟定义为dL,时钟线上的延迟定义为dC。若dL

如图组合逻辑中的延迟定义为dL,时钟线上的延迟定义为dC。若dL