单片机笔记(1)--单片机概述

目录

一.单片机概述

二.单片机结构原理

三.单片机硬件系统结构

1.运算部件

2.控制部件

四.存储器结构

1.程序存储器

2.数据存储器

1.程序计数器PC

2.累加器A

3.B寄存器

4.程序状态字寄存器PSW

5.堆栈指针SP

6.数据指针DPTR

7.端口P0-P3

8.串行数据缓冲器SBUF

9.定时器

3.外部数据存储器

4.I/O端口

5.I/O 口的读一修改—写特性

6.复位电路

7.复位时片内各寄存器的状态

8.时序(未搞清楚,待更新)

9.MCS-51 单片机引脚功能

1.端口线(4×8 = 32 条)

2.电源线(2条)

3.控制线(6条)

一.单片机概述

单片机即单片机微型单片机,是将单片机主机(CPU、内存和I/O接口)集成在一小块硅片上的微型机。单片机为工业测控而设计,又称微控制器(MCU)。

单片机是一种集成电路芯片,是采用超大规模集成电路技术把

具有数据处理能力的中央处理器CPU

、

随机存储器 RAM、只读存储器 ROM、多种 I/O 口和中断系统、定时器/计数器

等功能集成到一块硅片上

构成的一个小而完善的微型计算机系统。因此,单片机只需要有适当的软件和外部设备,便可组成为一

个单片机控制系统。

二.单片机结构原理

8051

系列单片机的主要功能如图:

1

.数据存储器

(RAM)

:片内为

128B

字节的

RAM

,片外最多可外扩至

64KB

。

2

.程序存储器

(ROM

/

EPROM)

:

8031

无此部件;

8051

为

4K ROM

;

8751

则为

4K EPROM

。片外

最多可外扩至

64K

字节。

3

.中断系统:具有

5

个中断源(其中内部

3

个,外部

2

个),

2

级中断优先权。

4

.定时器

/

计数器:

2

个

16

位的定时器/计数器,具有四种工作方式。

5

.串行口:

1

个全双工的串行口,具有四种工作方式。

6

.

P1

口、

P2

口、

P3

口、

P0

口:为

4

个并行

8

位

I

/

O

口。

7

.特殊功能寄存器

(SFR)

:

8051

有

128

个特殊功能寄存器寻址空间,有

21

个

SFR

,用于对片内各

功能模块进行管理、控制、监视。实际上是一些控制寄存器和状态寄存器,是一个特殊功能的

RAM

区。

8

.微处理器

(CPU)

:为

8

位的

CPU

,且内含一个

1

位

CPU(

位处理器

)

,不仅可处理字节数据,还可

以进行位变量的处理。

三.单片机硬件系统结构

MCS-51

系列单片机主要包括

算术/逻辑部件 ALU

、

累加器 A(有时也称 ACC)

、

只读存储器 ROM

、

随机存储器 RAM

、

指令寄存器 IR

、

程序计数器 PC

、

定时器/计数器

、

I/O 接口电路

、

程序状态寄存器

PSW

、

寄存器组

,此外,还有

堆栈寄存器 SP

,

数据指针寄存器 DPTR

等部件。这些部件集成在一块芯片

上,

通过内部总线连接

,构成完整的微型计算机。如下图所示:

1.运算部件

运算部件包括

算术逻辑部件 ALU、位处理器、累加器 A、寄存器 B、暂存器以及程序状态字 PSW 寄

存器

等。该模块的功能是实现数据的算术、逻辑运算、位变量处理和数据传送等操作。

ALU 的功能

十分强,它不仅可对

8

位变量进行逻辑“与”“或”、“异或”、循环、求补和清零等基本

操作,还可以进行加、减、乘、除等基本运算。

ALU

还具有一般微处理器的

ALU

所不具备的功能,即

位处理操作,它可对位

(bit)

变量进行位处理,如置位、清零、求补、测试转移及逻辑“与”、“或”等操作。

累加器 A

是一个

8

位的累加器:从功能上看,它与一般微处理器的累加器相比没什么特别之处,但

需要说明的是

A

的进位标志

Cy

是特殊的,因为它同时又是位处理器的一位累加器。

寄存器 B

是为执行乘法和除法操作设置的,在不执行乘、除法操作的一般情况下可把它当作一个普

通寄存器使用。

MCS-51

系列单片机的

程序状态寄存器 PSW

,是一个

8

位可读写的寄存器,它的不同位包含了程序

状态的不同信息。

CY (PSW.7)进位标志位

,在执行算术和逻辑指令时,可以被硬件或软件置位或清除,在位处理器中,

它是位累加器。

AC (PSW.6)辅助进位标志位

,当进行加法或减法操作而产生由低

4

位数向高

4

位进位或借位时,

AC

将被硬件置

1

,否则就被清除。

F0 (PSW.5)标志位

,它是由用户使用的一个状态标志位,可用软件来使它置位或清除,也可以靠软

件测试

FO

以控制程序的流向。编程时,该标志位特别有用。

RS1、RS0 (PSW.4、PSW.3)寄存器区

选择控制位

1

和

0

,这两位用来选择

4

组工作寄存器区

OV (PSW.2)溢出标志位

。当执行算术指令时,由硬件置

1

或清

0

,以指示溢出状态。

PSW.1 是保留位

,未用。

P (PSW.0)奇偶标志位

。每个指令周期都由硬件来置位或清除,以表示累加器

A

中值为

1

的位数的奇

偶数。若为奇数,则

P=l

,否则

P=0

。此标志位对串行口通讯中的数据传输有重要的意义,常用奇偶

检验的方法来检验数据传输的可靠性。

2.控制部件

控制部件是单片机的神经中枢,

以主振频率为基准(每个主振周期称为振荡周期)

,控制器控制 CPU

的时序,对指令进行译码,然后发出各种控制信号,它将各个硬件环节组织在一起。

四.存储器结构

程序存储器和数据存储器具有各自独立的寻址方式、寻址空间和控制信号。

MCS-51

的存储器结构如图

所示

(内部数据 RAM 的高 128B 仅为 52 子

系列单片机拥有,51 子系列无)

MCS-51

系列(

8031

和

8032

除外)有

4

个物理上相互独立的存储器空间,即内、外程序存储器和

内、外数据存储器。逻辑上分为三个存储空间,即

片内外统一编址的 64K 字节的程序存储器地址空间

、

256B 字节的片内数据存储器

以及

64K 字节的片外数据存储器地址空间

(可扩展数据

RAM

或

I/O

接口)。

1.程序存储器

程序存储器用于存放编好的程序和表格常数。

在

MCS-51

系列的指令系统中,同外部程序存储器打交道的指令仅有两条:

MCS-51

复位后,

程序计数器 PC 的内容为 0000H

,故系统必须从

0000H

单元开始取指令,执行程

序。程序存储器中的

0000H 地址是系统程序的启动地址。

一般在该单元存放

一条跳转指令,跳向用户设计的主程序的起始地址。

通常在这些入口地址处都放一条跳转指令。加跳转指令的目的是,由于两个中断入口间隔仅有八个

单元,存放中断服务程序往往是不够用的。

2.数据存储器

数据存储器用以存放和读取数据,它不能存放和执行程序指令。

数据存储器在物理上和逻辑上都分

为两个地址空间;

内部数据存储器(简称内部 RAM)

和

外部数据存储器(外部 RAM)

。内部

RAM 的地址空间为 00H-7FH,128B (8052 为 00H~0FFH 为 256B),外部 RAM 地址空间为 0000H~0FFFFH 的 64KB,

两者是由不同指令来访问的:

访问内部 RAM 用 MOV 类指令

;

访问外部 RAM 用 MOVX 指令。

8051

内部

RAM

的

128B

单元,可按功能分为三个区域:

(1)

从 00H~1FH 的 32B 单元是 4 个工作寄存器组

。前面已介绍每一组包括

8

个工作寄存器,

寄存器

名用 R0、R1、R2、R3、R4、R5、R6、R7 表示

,

单片机执行程序时同时只能选用其中的一组,具体使用

哪一组是通过对 PSW 的 RS1、RS0 两位的设置来实现的

。设置四组工作寄存器,给程序设计带来了好

处,很容易实现子程序嵌套、中断嵌套时的现场保护,如果在用户程序中只使用了一组内部

RAM

单元

作为工作寄存器,则其他三组

RAM

单元可作为一般的内部

RAM

作用,

MCS-51 在复位后,RS1、RS0都为 0,即指定 00H—07H 单元为 R0—R7。

(2

)地址 20H 一 2FH 的 16B 共 128 位,是可位寻址的内部 RAM 区,它们既可字节寻址,亦可位寻

址。

这些位寻址单元构成了布尔处理器的数据存储器空间。它们的位地址定义为

00H

—

7FH。

(3)

其他 80B 是只能按字节寻址的内部 RAM 区,为用户区。

MCS-51 单片机的堆栈安排在内部 RAM 内

,

堆栈的深度以不超过内部 RAM 的空间为限。

对

8051

类芯片最多为

128B

,对

8052

类芯片最多为

256B

。

1.程序计数器PC

程序计数器

PC

用于存放下—条要执行的指令地址,是一个

16

位专用寄存器,可寻址范围为

0

—

65535(64K)

,

PC

在物理上是独立的,不属于

SFR

,但它与

SFR

有密切联系,故放在此处介绍。

2.累加器A

累加器

A

是一个最常用的专用的寄存器,它属于

SFR

,大部分单操作数指令的操作数取自累加器,

很多双操作数指令的一个操作数取自累加器,加、减、乘、除算术运算指令的运算结果都存放在累加器

A

或

A

、

B

寄存器中。

3.B寄存器

在乘、除指令中,用到了

B

寄存器。乘法指令的两个操作数分别取自

A

和

B

,其结果存放在

A

、

B

寄存器对中。除法指令中,被除数取自 A,除数取自 B,运算后商数存放于 A,余数存放于 B。

4.程序状态字寄存器PSW

PSW

是一个

8

位寄存器,它包含了程序状态信息。

5.堆栈指针SP

堆栈指针 SP 是一个 8 位专用寄存器

。它指示出堆栈顶部在内部

RAM

块中的位置。

系统复位后,SP

初始化为 07H,使得堆栈事实上由 08H 单元开始

,考虑到

0BH

—

1FH

单元分别属于工作寄存器区

1

~

3

,

若在程序设计中要用到这些区,则最好把

SP

值改置为

1FH

或更大的值。单片机的堆栈是向上生成的。

例如 SP=60H,CPU 执行一条调用指令或响应中断后,PC 进栈,PC 的低 8 位送入到 61H,PC 高 8 位送

入到 62H,(SP)=62H。

6.数据指针DPTR

数据指针

DPTR

是一个

16

位的

SFR

,

其高位字节寄存器用 DPH 表示,低位字节寄存器用 DPL 表

示

。

DPTR

即可以作为一个

16

位寄存器

DPTR

来用,也可以作为两个独立的

8

位寄存器

DPH

和

DPL

来

用。

7.端口P0-P3

特殊功能寄存器 P0-P3 分别为 I/O 端口 P0-P3 的锁存器

。即每一个

8

位

I/O

口都对应

SFR

的一个地

址(

8

位)。在

MCS-51

中,

I/O

和

RAM

统一编址,使用起来较为方便,访问

I/O

端口可用访问

RAM

的

指令。

8.串行数据缓冲器SBUF

串行数据缓冲器 SBUF 用于存放欲发送或已接收的数据

,它在

SFR

块中只有一个字节地址,但在物

理上是由两个独立的寄存器组成,

一个是发送缓冲器 SBUF,另一个是接收缓冲器 SBUF

,当要发送的数

据传送到

SBUF

时,进的是发送缓冲器

SBUF

;接收时,外部来的数据存入接收缓冲器

SBUF

。

9.定时器

MCS-51 单片机有两个 16 位定时器/计数器 T0 和 T1

,它们各由两个独立的

8

位寄存器组成,共为

4

个独立的寄存器:

TH0

、

TL0

、

THL

、

TL1

。可以对这

4

个寄存器寻址,但不能把

T0

或

T1

当作一个

16

位寄存器来对待。

3.外部数据存储器

MCS-51 外部数据存储器寻址空间为 64KB

,这对多数应用领域已足够使用。对外部数据存储器可用

R0,R1 及 DPTR 间接寻址寄存器。R0,R1 为 8 位寄存器,寻址范围为 256B,DPTR 为 16 位的数据指针,

寻址范围为 64KB。在

MCS-51

的指令系统中,

同外部数据存储器打交道的指令有 4 条:

4.I/O端口

MCS-51 单片机有 4 个双向的 8 位并行 I/O 口:P0~P3,每一个口都有一个 8 位的锁存器,复位后

它们的初始状态为全“1”。

P0 口是三态双向口,既可作为并行 I/O

口,也可作为数据总线口。当外部扩展了存储器或

I/O

端口,

则只能作数据总线和地址总线低

8

位。当作为数据总线口时是分时使用的,即先输出低

8

位地址,后用

作数据总线,故应在外部加锁存器将先送出的低

8

位地址锁存,地址锁信号用

ALE

。

P1 口是专门供用户使用的 I/O 口,是准双向接口。

P2 口是准双向接口,既可作为并行 I/O 口,也可作为地址总线高 8

位口。当外部扩展了存储器或

I/O

端口,则只能作地址总线高

8

位。

5.I/O 口的读一修改—写特性

每个 I/O

端口均有两种读入方法,即读锁存器和读引脚,并有相应的指令,那么如何

区分读端口的指令是读锁存器还是读引脚呢?

读锁存器指令是从锁存器中读取数据,进行处理,并把处理以后的数据重新写入锁存器中,这类指

令称为“读一修改一写”批令

。当目前操作数是一个

I/O 端口或 I/O 端口的某一位时,这些指令是读锁存

器而不是读引脚,即为“读一修改一写”指令,下面列出的是一些“读一修改一写”指令。

ANL (逻辑与,例如 ANL P1,A)

ORL (逻辑或,例如 ORL P2,A)

XRL (逻辑异或,例如 XRL P3,A)

JBC (若位=1,则转移并清零,例如 JBC P1.1,LABEL)

CPL (取反位,例如 CPL P3.0)

INC (递增,例如 INC P2)

DEC (递减,例如 DEC P2)

DJNZ (递减,若不等于 0 则转移,例如 DJNZ P3,LABEL)

MOV P1.7,C (进位位送到端口 P1 的位 7)

CLR P1.4 (清零端口 P1 的位 4)

SETB P1.2 (置位端口 P1 的位 2)

读引脚指令一般都是以 I/O 端口为原操作数的指令,执行读引脚指令时,打开三态门,输入口状态。

例如,读 P1 口的输入状态时,读引脚指令为:MOV A,P1。

读—修改—写指令指向锁存器而不是引脚,其理由是为了避免可能误解引脚上的电平。

6.复位电路

MCS-51

的复位输入引脚

RST(

即

RESET)

为

MCS-51

提供了初始化的手段。有了它可以使程序从指

定处开始执行,

即从程序存储器中的 0000H 地址单元开始执行程序。

只要

RST

保持高电平。则

MCS-

51

循环复位。只有当

RST 由高电平变低电平以后,MCS-51 才从 0000H

地址开始执行程序。

7.复位时片内各寄存器的状态

程序运行直接受程序计数器(PC)指挥。

复位后

PC

值为

0000H

,

故复位后的程序入口地址为 0000H;

复位后 PSW=00H,使片内存储器中选择 0 区工作寄存器

,用户标志为

F0

为

0

状态;

复位后 SP=07H,设定推栈栈底为 07H;

TH1、TL1、TH0 、TL0 都为 00H,表明定时/计数器复位后皆清零;

TMOD=00H 都处于方式 0 工作状态,并设定 T1、T0 为内部定时器方式,定时器不受外部引脚

控制;

TCON=00H,禁止计数器计数,并表明定时/计数器无溢出中断请求

,并禁止外部中断源的中断

请求,外部中断源的中断请求为电平触发方式;

SCON=00H 使串行口工作在移位寄存器方式(方式 0)

,并且设定允许串行移位接收或发送;

复位后

IE

的各位均为零,表明在中断系统

CPU

被禁止响应中断,而且每个中断源也被禁止中

断;

复位后

IP

的各位均为零,表明在断断系统的

5

个中断源都设置为低优先级中断状态;

复位后的

P1

,

P2

,

P3

口锁存器全为

1

状态,使这些准双向口皆处于输入状态。

在复位有效期间(即高电平),MCS-51 的 ALE 引脚和引脚均为高电平,且内部 RAM 不受复

位的影响。

8.时序(未搞清楚,待更新)

9.MCS-51 单片机引脚功能

MCS-51 单片机 DIP 封装有 40 条引脚,共分为端口线、电源线和控制线三类。

1.端口线(4×8 = 32 条)

MCS-51 共有四个并行 I/O 端口,每个端口都有 8 条端口线,用于传送数据/地址或其它信息。

P0.0-P0.7 :

这组引脚共有 8 条,为 P0 口专用,其中 P0.7 为最高位

,

P0.0 为最低位。这

8

条引脚共有两种不同

功能,分别使用于两种不同情况之下。

第一种情况是 MCS-51 不带片外存储器的型号,P0 口可以作为通

用 I/O 口使用,P0.7~P0.0 用于传送 CPU 的输入/输出数据。

输出数据可以得到锁存,不需外接 专用锁存器,输入数据可以得到缓冲,增加了数据输入的可靠性。

第二种情况是带片外程序存储器,P0.7~

P0.0 在 CPU 访问片外存储器时先是用于传送片外存储器的低 8 位地址,然后传送 CPU 对片外存储器的读

或写数据。

P1.0-P1.7 :

这 8 条引脚和 P0 口的 8 条引脚类似,P1.7 为最高位

,

P1.0 为最低位。当 P1 口作为通用 I/O 使用时,

P1.0-P1.7 的功能和 P0 口的第一功能相同,也用于传送用户的输入/输出数据。

P2.0-P2.7 :

第一功能和上述两组引脚的第一功能相同,即它可以作为通用 I/O 使用。它的第二功能

和 P0 口引脚的第二功能相配合,用于输出片外存储器的高 8 位地址,共同选中片外存储器单元,但并不

能像 P0 口那样还可以传送存储器的读写数据。

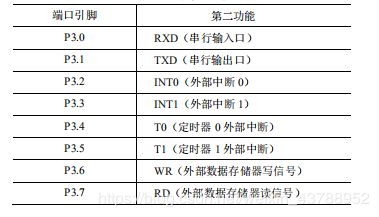

P3.0-P3.7 :

这组引脚的第一功能和其余三个端口的第一功能相同,第二功能作控制用,每个引脚并不完全相同。

2.电源线(2条)

VCC

为

+5V

电源线,

VSS

为地线。

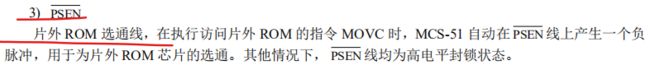

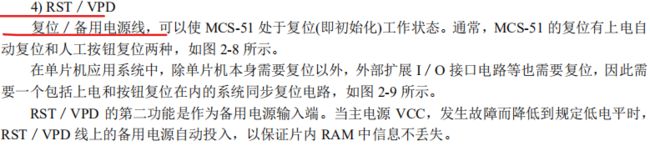

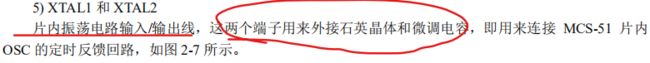

3.控制线(6条)

1.

2.

3.

4.

5.