IC芯片制造过程简介

转:http://news.hexun.com/2018-04-22/192880330.html

注:台湾话

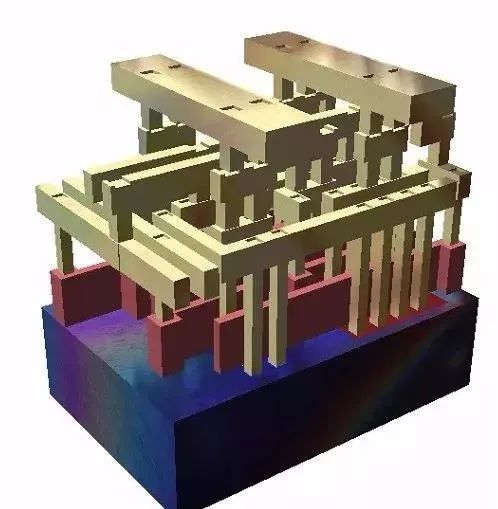

在开始前,我们要先认识 IC 芯片是什么。IC,全名积体电路(Integrated Circuit),由它的命名可知它是将设计好的电路,以堆叠的方式组合起来。藉由这个方法,我们可以减少连接电路时所需耗费的面积。下图为 IC 电路的 3D 图?????从图中可以看出它的结构就像房子的樑和柱,一层一层堆叠,这也就是为何会将 IC 制造比拟成盖房子。

从上图中 IC 芯片的 3D 剖面图来看,底部深蓝色的部分就是晶圆,从这张图可以更明确的知道,晶圆基板在芯片中扮演的角色是何等重要。至于红色以及土黄色的部分,则是于 IC 制作时要完成的地方。

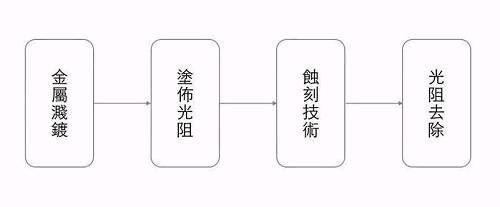

知道 IC 的构造后,接下来要介绍该如何制作。试想一下,如果要以油漆喷罐做精细作图时,我们需先割出图形的遮盖板,盖在纸上。接着再将油漆均匀地喷在纸上,待油漆乾后,再将遮板拿开。不断的重复这个步骤后,便可完成整齐且复杂的图形。制造 IC 就是以类似的方式,藉由遮盖的方式一层一层的堆叠起来。

金属溅镀:将欲使用的金属材料均匀洒在晶圆片上,形成一薄膜。

涂布光阻:先将光阻材料放在晶圆片上,透过光罩(光罩原理留待下次说明),将光束打在不要的部分上,破坏光阻材料结构。接着,再以化学药剂将被破坏的材料洗去。

蚀刻技术:将没有受光阻保护的硅晶圆,以离子束蚀刻。

光阻去除:使用去光阻液皆剩下的光阻溶解掉,如此便完成一次流程。

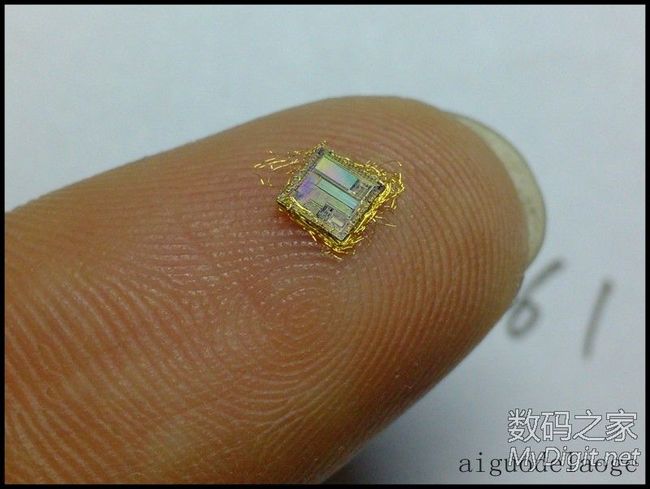

最后便会在一整片晶圆上完成很多 IC 芯片,接下来只要将完成的方形 IC 芯片剪下,便可送到封装厂做封装(DIP、BGA)。

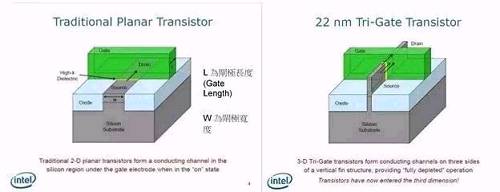

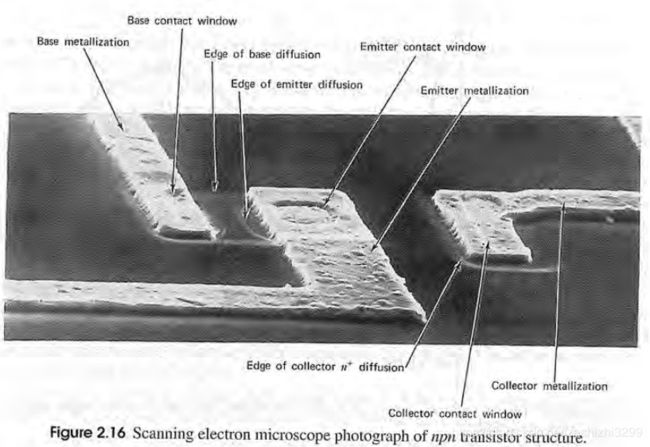

14纳米芯片概念,纳米制程是指在芯片中,线???最小可以做到 14 纳米的尺寸,下图为传统电晶体的长相,以此作为例子。缩小电晶体的最主要目的就是为了要减少耗电量,然而要缩小哪个部分才能达到这个目的?左下图中的 L 就是我们期望缩小的部分。藉由缩小闸极长度,电流可以用更短的路径从 Drain 端到 Source 端(有兴趣的话可以利用 Google 以 MOSFET 搜寻,会有更详细的解释)。

不过,制程并不能无限制的缩小,当我们将电晶体缩小到 20 纳米左右时,就会遇到量子物理中的问题,让电晶体有漏电的现象,抵销缩小 L 时获得的效益。作为改善方式,就是导入 FinFET(Tri-Gate)这个概念,如右上图。在 Intel 以前所做的解释中,可以知道藉由导入这个技术,能减少因物理现象所导致的漏电现象。

更重要的是,藉由这个方法可以增加 Gate 端和下层的接触面积。在传统的做法中(左上图),接触面只有一个平面,但是采用 FinFET(Tri-Gate)这个技术后,接触面将变成立体,可以轻易的增加接触面积,这样就可以在保持一样的接触面积下让 Source-Drain 端变得更小,对缩小尺寸有相当大的帮助。

为什么会有人说各大厂进入 10 纳米制程将面临相当严峻的挑战,主因是 1 颗原子的大小大约为 0.1 纳米,在 10 纳米的情况下,一条线只有不到 100 颗原子,在制作上相当困难,而且只要有一个原子的缺陷,像是在制作过程中有原子掉出或是有杂质,就会产生不知名的现象,影响产品的良率。

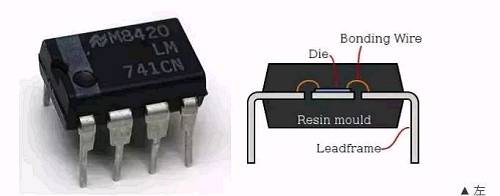

目前常见的封装有两种,一种黑色长得像蜈蚣的 DIP 封装,另一为购买盒装 CPU 时常见的 BGA 封装。

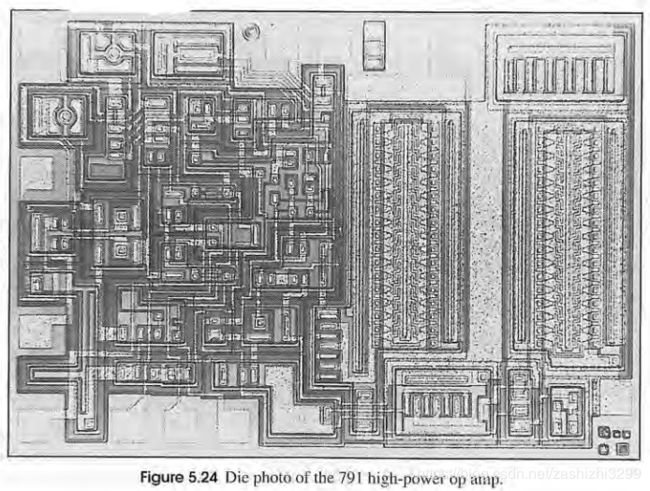

首先要介绍的是双排直立式封装(Dual Inline Package;DIP),从下图可以看到采用此封装的 IC 芯片在双排接脚下,看起来会像条黑色蜈蚣,让人印象深刻,此封装法为最早采用的 IC 封装技术,具有成本低廉的优势,适合小型且不需接太多线的芯片。但是,因为大多采用的是塑料,散热效果较差,无法满足现行高速芯片的要求。因此使用此封装的大多是历久不衰的芯片,如下图中的电压放大器OP741及其冲模照片,或是对运作速度没那么要求且芯片较小、接孔较少的 IC 芯片。

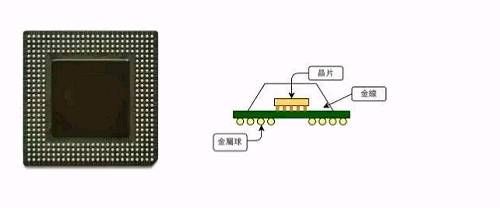

球格阵列(Ball Grid Array,BGA)封装,和 DIP 相比封装体积较小,可轻易的放入体积较小的装置中。此外,因为接脚位在芯片下方,和 DIP 相比,可容纳更多的金属接脚。适合需要较多接点的芯片。然而,采用这种封装法成本较高且连接的方法较复杂,因此大多用在高单价的产品上。

然而,如果各个元件都独立封装,组合起来将耗费非常大的空间,因此目前有两种方法,可满足缩小体积的要求,分别为 SoC(System On Chip)以及 SiP(System In Packet)。

在智慧型手机刚兴起时SoC 这个名词,就是将不同 IC整合在一颗芯片中。不单可以缩小体积,还可以缩小 IC 间的距离,提升芯片的计算速度。至于制作方法,便是在 IC 设计阶段时,将各个不同的 IC 放在一起,制作成一张光罩。

然而信号干扰,像是通讯芯片的高频讯号可能会影响其他功能的 IC 等情形。

此外,SoC 还需要获得其他厂商的 IP(intellectual property)授权,增加了 SoC 的设计成本。

折衷方案,SiP 现身

作为替代方案,SiP 跃上整合芯片的舞台。和 SoC 不同,它是购买各家的 IC,在最后一次封装这些 IC,如此便少了 IP 授权这一步,大幅减少设计成本。此外,因为它们是各自独立的 IC,彼此的干扰程度大幅下降??????举例:apple watch

【60FPS】 60帧的Intel芯片制作过程!!!_哔哩哔哩 (゜-゜)つロ 干杯~-bilibili

https://www.bilibili.com/video/av19382074/?spm_id_from=333.788.videocard.12

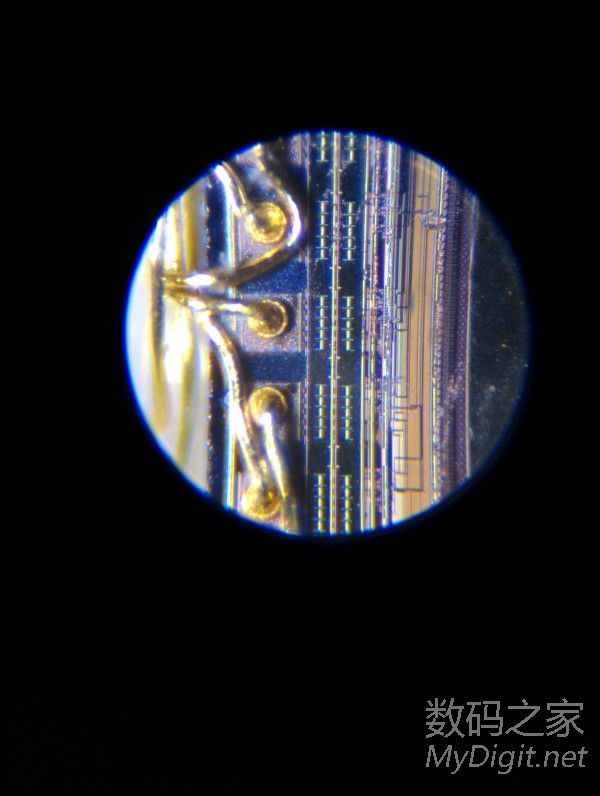

显微镜下的集成电路,人类工艺的巅峰!_哔哩哔哩 (゜-゜)つロ 干杯~-bilibili

https://www.bilibili.com/video/av12652893/?spm_id_from=333.788.videocard.6

级别:1微米(1000纳米)

单片机

https://www.bilibili.com/video/av7515293/?spm_id_from=333.788.videocard.12

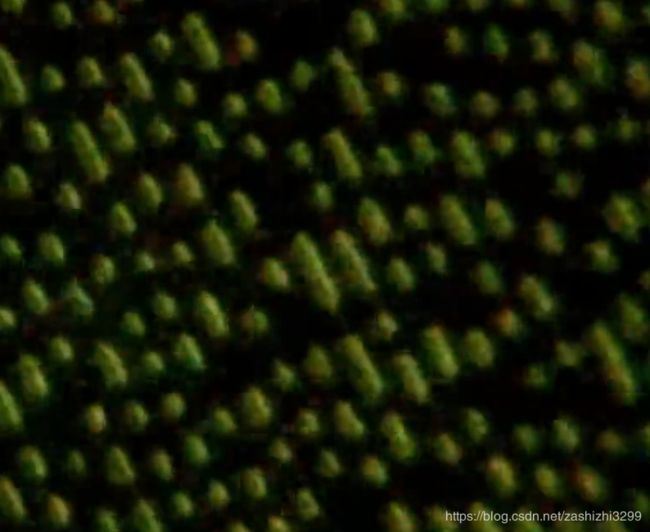

显微镜下的CD光盘 [2000倍]

https://www.bilibili.com/video/av34555351/?spm_id_from=333.788.videocard.4

数量级:???

电脑科技: 电脑CPU芯片放大14万倍后,内部构造复杂到不可思议!_哔哩哔哩 (゜-゜)つロ 干杯~-bilibili https://www.bilibili.com/video/av22251521/?spm_id_from=333.788.videocard.2

机械硬盘,不管多大,结构都差不多。

《硬盘三连拆》第三章:昆腾大脚机械硬盘_哔哩哔哩 (゜-゜)つロ 干杯~-bilibili https://www.bilibili.com/video/av55809051

芯片的制程

原文链接:https://blog.csdn.net/chauncey_wu/article/details/81352706

此文以MOS管为例。

1 CMOS管的基本构造

![]()

N沟道增强型MOS管的结构示意见上图。它是在P型衬底上,用扩散法制作两个高掺杂度的N区。然后在P型硅表面生长一层很薄的二氧化硅绝缘层,并在二氧化硅表面及两个N型区各安置一个电极,形成栅极g,源级s和漏级d。

2 晶体管栅极g是什么作用?

晶体管栅极是晶体管的控制端。晶体管(这里只考虑MOSFET,不考虑BJT啥的)有四个电极:栅、源、漏、衬底。其中衬底电压一般是固定的,也不会有电流流入,可以忽略。栅极是控制极,栅极和源极之间的的电压差,控制了漏极和源极之间的电流大小。(就是个跨导啦)简单地说栅极就是一个开关,当Vgs为高时导通(简称高导)。

3 xx制程的含义

晶体管结构中,电流从Source(源极)流入Drain(漏级),Gate(栅极)相当于闸门,主要负责控制两端源极和漏级的通断。电流会损耗,而栅极的宽度则决定了电流通过时的损耗,表现出来就是手机常见的发热和功耗,宽度越窄,功耗越低。而栅极的最小宽度(栅长),就是XX nm工艺中的数值。对于芯片制造商而言,主要就要不断升级技术,力求栅极宽度越窄越好。不过当宽度逼近20nm时,栅极对电流控制能力急剧下降,会出现“电流泄露”问题。为了在CPU上集成更多的晶体管,二氧化硅绝缘层会变得更薄,容易导致电流泄漏。一方面,电流泄露将直接增加芯片的功耗,为晶体管带来额外的发热量;另一方面,电流泄露导致电路错误,信号模糊。为了解决信号模糊问题,芯片又不得不提高核心电压,功耗增加,陷入死循环。因而,漏电率如果不能降低,CPU整体性能和功耗控制将十分不理想。

参考文献

1、模电,Paul R. Gray - Analysis and Design of Analog Integrated Circuits, 5th edition (2009, John Wiley & Sons Inc)

2、模电,Allen P.E., Holberg D.R. - CMOS Analog Circuit Design

3、https://mp.weixin.qq.com/s/4pM6kaTojr-x97jczRsGHA

4、【转载】芯片级拆解51、AVR、MSP430、凌阳61、PIC,5种单片机,多张显微照片 - 编程浪子_ - 博客园 https://www.cnblogs.com/zyqgold/p/3296277.html

5、《计算机体系结构—量化研究方法(第5版)》

6、芯片制造22nm制程是什么含义 - Chauncey_wu的博客 - CSDN博客 https://blog.csdn.net/chauncey_wu/article/details/81352706