VR与平板电脑高速PCB设计实战攻略

第一章

存在一种带触摸识别或电磁输入的液晶LCD显示屏

平板电脑按其触摸屏的不同,一般分为电阻式触摸屏和电容式触摸屏

根据其功能的不同分为,WIFI版和3G版

3G版其实就是在SIM卡模块中插入支持3G高速无线网络的SIM卡,通过3G信号接入运营商的信号基站,从而实现通信的目的。3G信号技术分别有CDMA、WCDMA、TD-CDMA

平板电脑的常见的操作系统有Windows操作系统 Android操作系统 ISO操作系统,还有像Windows CE操作系统等

Windows7有基础版、家庭版、旗舰版等多个版本,都是基于X86架构开发的,后期增加了Windows8和Windows10两个版本的操作系统

Windows CE属于嵌入式操作系统,使用标准的win32 API子集,应用程序的兼容性非常好。但是其体积大,导致系统的资源占用较大,而且由于通过虚拟地址映射,导致其运行的速度和效率都低于同类的嵌入式操作系统

平板电脑的架构一般是X86架构(特定微处理器指令集)或arm架构(特定微处理器指令集)

平板电脑的主要电路

CPU电路

DDR存储电路 EMMC/Flash

图像处理显示/照相机GPU电路

音频Audio处理

触控TP电路

电源PMU管理电路

WLAN蓝牙电路

4G电路

逻辑电路是平板电脑的核心部分。一般有微处理电路和存储器电路组成,微处理器电路和存储器电路通过总线和控制线连接,从而实现数据传输和通道的控制,如片选、复位、看门狗和读写信号的处理

目前国内平板电脑市场上使用的最多的芯片主要集中在 三星 瑞芯微 全志 炬力和华为海思

国外主流芯片 高通 英伟达 三星Exynos

国内主流芯片 瑞芯微 全志 炬力 海思

高通 芯片主攻智能手机市场,是HTC、索尼、诺基亚、LG等智能手机的主要芯片供应商

英伟达 Tegra3 Tegra4、Icera i500等

三星 三星的Exynos4412芯片近几年在国内平板电脑市场异常火爆

瑞芯微 RK3188和RK3288是目前国内平板厂商应用较广的一款芯片

全志 A31、 H8(28nm制造工艺、8个ARM Cortex-A7内核、支持八核心、2.0GHz、搭配强劲的PowerVR SGX544图像处理架构700M工作频率)、 A64等多用于平板电脑、智能手机、智能电视领域

海思 由华为公司自主研发的一款A9架构的四核处理器,主频分别为1.2G和1.5G,是华为自主设计的,采用ARM架构35nm、64位内存总线

炬力 四核cortex A9架构,主频为1.5GHz

硬件电路原理性知识,电子元器件特性,熟悉SI、PI、EMC、热设计及工艺设计、产品可制造性等多方面知识

ARM处理器系列

ARM7系列 ARM9系列 ARM9E系列 ARM10E系列 ARM11系列

Cortex系列 Securcore系列 OptimoDE Data Engines系列 Xscale系列 StrongARM ARM11系列

Cortex-M系列

cortex-M0 cortex-M0+ cortex-M3 cortex-M4

Cortex-R系列

Cortex-R4 Cortex-R5 Cortex-R7

Cortex-A系列

Cortex-A5 Cortex-A7 Cortex-A9 Cortex-A15 Cortex-A17 Cortex-A50 Cortex-A53 Cortex-A57

第二章

在平板领域中,ARM的CPU分为单核、双核、四核、八核等

按位数可分为16位、32位和64位

CUP按型号可分为ARM9/ARM11/cortexA8/cortexA9/cortexA15/cortexA50/cortexA53/cortexA57

其中cortexA53和cortexA57是64位CPU

主流厂商:三星、联发科、瑞芯微、全志、苹果、高通、华为、晶晨

CPU运行原理分为四个步骤 提取 解码 执行 写回

CPU从存储器或者高速缓存中提取数据

放入指令寄存器内

对指令寄存器内的数据进行译码,执行指令

GPU图像处理器

显卡的核心,决定了显卡的性能。2D显卡在处理3D图像时主要依赖CPU的处理能力,称为软加速。3D显卡芯片将三维图像处理和特效处理集成在显卡内实现了硬加速

CUP的主频越高,单位时间内执行的指令越多,运算速度越大,功耗越大

Cache缓存是CPU和内存交换数据时的数据缓冲区

制程:制造工艺,线路宽度越小,功耗和发热量越低,可以工作在更高的频率,如45nm,32nm,28nm等

PMU分为两种 一种是上电后即可输出电压的BUCK和LDO电源模块

一种是上电不输出电压,需要使用I2C进行配置后才输出电压的BUCK和LDO电源模块

动态电源管理能在系统和电池充电之间共享交流适配器电流,在系统负载上升时,自动减少充电电路电流,调整充电电流和系统的电流分配,最大限度的保证系统的正常工作,当USB端口充电时,如果输入电压降低到防止USB端口崩溃的阈值以下,基于输入电压的动态管理便能减少输入的电流

一般PMU和主芯片绑定定制的,因为要配合CUP的上电时序

PMU其实是带有掩膜程序的专用电源控制器,要用32.768KHz和24MHz的晶体,待机状态是32.768K,正常工作时是24M的主晶体工作

由两个能可逆地嵌入和脱嵌锂离子的化合物作为正负极构成的二次电池

锂离子电池的主要参数

电池容量1000mAh(一般以0.5C-1C的电流充电)

标称电压(单节锂离子电池的标称电压为3.7V)

充电终止电压(锂离子电池通常为4.2V-4.3V)

放电终止电压(锂离子电池一般放电到3V截止,继续下去会对电芯造成不可挽回的伤害,而且3V到2.7V的能量只占总能量的3%)

电池内阻(一般小于110毫欧,固有属性,与电池容量无关)

自放电率(锂离子电池一般5%-8%/月)

一般电池过放时(电压低于3V,内部保护电路工作关断电池输出,电池无输出电压,测量为0V)

充电过程一般分为四个步骤:预充电、恒流充电、恒压充电、涓流充电/脉冲充电

预充 电池电压低于设定门限电压时,以小电流保护性充电。过放电池充电初期,因为锂离子电池电芯材料的原因,若用大电流充电,容易导致电芯极化现象,缩短电池寿命,所以必须用小电流预充电一段时间

恒流充电 当电池电压达到门限电压后,以恒定的大电流对电池进行充电,电池电压迅速上升

恒压充电 当恒流充电结束时,充电电路将电池电压维持在4.2V,电池电量接近90%,但是并未完全充满,所以充电电路将电池电压维持在4.2V的状态,进行恒压充电。此时充电电压保持不变,充电电流随时间增加而减小

涓流/脉冲充电 对电池的自放电进行补充,由此产生了脉冲方式的补充充电

有时电池还带有ID脚检测,判断电池的种类

锂离子电池具有放电电流大,内阻小,寿命长,无记忆效应等特点

锂离子电池使用要防止过充 过放 电芯极化

钜大锂电测试电池电压于电池容量的对应关系

100%----4.20v 90%-----4.06v

80%-----3.98v 70%-----3.92v

60%-----3.87v 50%-----3.82v

40%-----3.79v 30%-----3.77v

20%-----3.74v 10%-----3.68v

5%------3.45v 0%------3.00v

过放电池,一般指电压低于3V左右时,电池内部保护电路启控后会自动关闭电池的输出,实际测量电压为0,此时需要充电激活

电量计(Fuel Gauge) 对时间和电流的积分来计算当前电池的容量,使用前需要校准(进行一次或多次的完整充放电循环),搭配实时时钟管理电路后,具备实时性(RTC)

存储器分为RAM和ROM两种

ROM基本全是Flash型ROM,而RAM基本由SDRAM和DDR SDRAM组成

DDR有2代和3代的区别,3代的速度更快,工作电压是1.5V,而2代是1.8V,3代上面新增加了RSET和ZQ脚,单纯的从外观上分辨不出来是2代还是3代内存

DDR2 DDR3 DDR3L LPDDR

Core voltage 1.8V 1.5V 1.35V 1.25V

Data frequence 400/533/667/800M 800/1333/1600/2133M

DDR芯片的数据总线有8位16位和32位,如果是8位,则64位的数据总线需要8片DDR芯片

DDR芯片引脚介绍

CK,CK# 差分时钟信号 所有的控制和地址输入信号在CK的上升和CK#的下降沿采样,输出数据(DQS,DQS#)参考CK和CK#的交叉

CKE 时钟使能

CS# 片选信号,为输入信号,低电平有效

RAS# 行地址选通信号

CAS# 列地址选通信号

WE# 写使能信号,为输入信号,低电平有效

BA{0-2} BANK地址信号,低电平有效

DQM{0-1}数据掩膜,为输入/输出双向信号,方向和数据总线方向相同,高电平有效

ODT 终结电阻,用于提高信号的传输性能,类似于终端电阻,可以降低干扰,改善信号传输波形

ZQ 外接一个240欧的高精度电阻,可以提高数据总线的信号传输质量,从而提高传输速度

RSET 复位信号,低电平有效

DQ{0-15} 数据信号,为输入/输出双向信号

A{0-15}地址信号,为输入信号

DQS DQS# 数据选通信号,数据可以通过DQS的上升沿与下降沿传输

VERF CA/VERF DQ 基准电压等于VDD电压一半,VERF CA 为命令和地址部分电路提供基准电压,VERF DQ 为数据部分的电路提供基准电压

VDD(5%精度) 主要给芯片内部地址/控制信号接口和主要的逻辑控制单元供电 例:

VDDQ(同VDD) 主要给数据及锁存信号接口及逻辑电路供电 例:LPDDR3 1.25V

VDLL(同VDD)给内存芯片内部的延时锁相环电路供电

VSS 芯片内部地址/控制信号接口和主要的逻辑控制单元提供地回路

VSSQ 数据及锁存信号接口及逻辑电路提供地回路

VSSDL 给内存芯片内部的延时锁相环电路提供地回路

目前DDR3内存基本采用8个BANK的设计,寻址的过程先指定BANK地址,然后再指定行地址和列地址,最终确定寻址单元

DDR布线中经常使用的有T型拓扑结构和菊花链、Fly-by拓扑结构

T型拓扑结构 保证每个分支接收端负载同时接受到信号,每条分支上一般都需要终端电阻,终端电阻的阻值应该和连线的特性阻抗相匹配

菊花链拓扑结构 这种结构确保每个驱动端的信号主干道的长度尽量短,牺牲了时钟、地址和控制信号的同步,尽可能的降低各负载分支走线的长度,避免分支信号对主干信号的反射干扰

Fly-by拓扑结构 在信号频率低于800MHz的时候,上述两种拓扑结构均可以满足系统性能的要求。但是当信号速率到达1000MHz以上时,T型拓扑结构就不能满足需要了。是由于T型结构的各分支走线太长,在不添加终端电阻的情况下很难实现和主干道的阻抗匹配,但是为每个支路添加终端匹配电阻,又加大了电路设计的工作量和成本。因此高速信号使用T型结构,特别是分支大于4的时候,支路对主干信号的干扰是非常严重的。

菊花链结构可以减小分支信号的长度,降低对主干信号的干扰,所以对于高速的DDR3芯片,应该采用菊花链结构。

当信号速率在1600MHz以上时,只能采用菊花链结构的改进形式,Fly-by结构。Fly-by结构要求无分支,所有的DDR芯片串联到电路中,最后接匹配电阻

DDR一般电流都较大,所以需要有一个完整的电源平面供电,并且在电源的入口加上大电容,和10-100nF(0.01u-0.1u)(10M-200MHz)的小电容滤波

Vref=1/2VDD 这个VREFCA主要是为命令和地址信号服务,VREFDQ主要是为数据总线服务。这个电压既可以由电压芯片提供,也可以从VDD分压得到,一般大小为几个mA到几十个mA。一般采用VDD分压得到,分压电阻在100到10K均可,需要使用1%精度的电阻,而且每一个VREF引脚都需要添加10nF的电容滤波,并且分压电阻上也需要并联电容

VREF和端接电压VTT尽量远离,不要走到一起,建议间距在4mm以上

VTT和VREF的电压其实是相等的,都为VDD的一半,但是VREF消耗的电流很小,VTT的电流较大,能达到百毫安级,需要使用电源芯片单独产生

当DDR芯片数量为1片或2片的时候,总线上需要的电流不是特别大,这个时候可以不进行VTT端接,当DDR芯片数量在4片或以上的时候,此时地址线和数据线的负载都比较重,这时需要芯片来产生VTT电压。如果使用VTT,则VTT端接电流会比较大(2-3.5A),所以也需要铜皮敷过去,一般由专门为DDR设计的电源芯片来满足要求。VTT要求电源既可以提供电流又可以灌电流(吸收电流)

串行端接电阻主要应用在DDR芯片不大于4片的情况,对于双向数据线来说,串行端接电阻需要放置在走线的中间,用来抑制振铃、过冲和下冲。对于单向的地址线、控制线来说,串行端接电阻放置在中间或者信号的发生端处,串接电阻值一般10-33欧,具体值要通过仿真或者经验积累

并行端接电阻主要是DDR芯片大于4片的情况,走线长度大于2000mil

Flash Memory即是闪存,目前的Flash芯片有NOR和NAND两种规格

NOR的特点是芯片内执行,应用程序直接在Flash上运行,不必读到RAM中,NOR的传输效率高,在1-4MB的小容量时具备很高的成本效益,但是很低的写入和擦除速度影响了它的性能

NAND通常用于存储处理器的代码数据和用户数据,NAND Flash基本上是系统的硬盘。它结构单元紧密,可以达到很高的存储密度,并且擦除和写入速度也很快,难点是Flash的管理需要特殊的系统接口支持

NAND Flash的引脚功能介绍

I/O(0-7)用于输入地址/数据/命令,输出数据,可能为16位,但高八位只用于数据

CLE 命令锁存使能,输入命令前需要先在模式寄存器中设置CLE使能

ALE 地址锁存使能,输入地址前需要先在模式寄存器中设置ALE使能

CE# 芯片使能

RE# 读使能,在读取数据前,要先使RE#有效

WE# 写保护,在写取数据前,要先使WE#有效

WP# 写保护

R/B 就绪或者忙检测脚

VCC 电源

VSS 接地

NC 未定义引脚

EMMC由闪存和闪存控制器组成,方便与CPU更快更好的通信

MMC接口速度高达52MB/s ,其接口电压为1.8V或3.3V

eMMCFlash存储的容量大,市场上有32GB、42GB容量等

平板电脑中常见液晶屏的尺寸有5寸、7寸、8寸、8.9寸、9寸、9.7寸、10.1寸等多种规格

从材料上划分为TFT和ISP屏

从分辨率上有800*480、1024*768、1280*800、1920*1080、1920*1200、2048*1536、2560*1600等

TFT屏只能识别TTL(RGB)信号

差分信号在终端两差分信号间跨接一个电阻,平衡差分信号,其阻值通常为100-120欧

EDP是基于DP接口的架构和协议的一种内部数字接口(无单独时钟线),未来会取代LVDS接口

LVDS数据传输数字在1G一下,而DP接口的数据传输速度有1.6Gbps,2.7Gbps,5.4Gbps,且内容保护(HDCP)

EDP信号分为三类:Main Link AUX HPD

Main Link:四对数据差分信号线 ,无时钟线,特定数据编码格式,用于传输各类视频数据

AUX:辅助通道,采用特定数据编码格式传输,低延时特性,用于小带宽的数据传输,链路管理和设备控制

HPD:热插拔检测通道,用于检测上层设备和下层设备是否连接,进而进行线路的连接和中断

LCD背光有两种:CCFL背光和LED背光

LED背光电压之所以较高,是因为多个LED二极管串联使用,通常的背光电压有16V、19.8V、23.1V、25.6V等,所以都需要背光Boost升压电路

触摸屏驱动芯片类似于矩阵键盘一样,通过XY轴间不断的扫描,判断具体位置有无触摸发生,分为自容式和互容式

X轴发送,Y轴检测高频电压电流有无变化,若有变动,IC将变化的电信号转化为位置信息,向CPU发送中断请求

然后通过I2C去中断传输位置信息,进行后续操作,多点触控是触摸驱动芯片能一次保存多个触摸点位置进行传输

摄像头模组(CCM):OV2640/OV3640(200万像素) 0V5640/美光科技MT9P(500万像素) MP9E103/OV8825(800万像素)

OV12830/OV16820(1300万像素)

摄像头组件:镜头、传感器、DSP等 (关键技术门槛是:光学设计技术、非球面镜制作技术、光学镀膜技术)

镜头:通过透镜合理的聚光

传感器:将光信号转换为电信号RAW DATA(单色RGB信号)

ISP/DSP:转换为RGB、YUV格式的图像信号给CPU处理

图像采集流程为:感光、模拟信号放大、AD转换、增益控制 白平衡控制 噪点纠正、ISP、通信输出、

摄像头接口:SPI (串口低端摄像头) DVP(并口,普通常用)

MIPI(成立之初是想将摄像头、显示屏、视频/基带接口统一,减少设计的复杂度提高设计的灵活性,现在用的较多的是MIPI的摄像头标准MIPI CSI和显示标准MIPI DSI)(每个通道可传输500-1000Mbps的数据)

摄像头引脚说明

PWDN 睡眠模式控制线,当传感器不工作时,可以通过这个引脚进入Standby模式,降低功耗

RESET 复位引脚,只有在XCLK开启后,将RESET拉低,才能进行硬复位

XCLK 工作时钟引脚,此引脚为CPU提供给摄像头的工作时钟

SDA/SCL 为I2C信号

DATA{0-9} 输入数据信号线,如果采用YUV或8位RAW输出则只用到{2-9},才有10位的RAW则全部用到

VSYNC/HSYNC帧同步和行同步信号,表示数据输出完毕

PCLK 像素同步信号引脚,输出的时钟信号由传感器产生,PCLK是从MCLK通过PLL处理后得到的,为后端DSP或MCU采集Y{0:9}数据提供同步信号,PCLK信号结束表示一个数据已经传输完毕

AVDD 模拟电压{2.6-3V}用于传感器感光区的工作,是采集信号的工作电压,必须干净,否则降低成像的质量

DOVDD 数字电压{1.7-3V}用于数据Y{0:9}等I/O

DVDD 核工作电压1.5V,用于传感器内部电路的工作

一旦给摄像头提供了MCLK,并且RESET信号有效,那么摄像头就开始工作,通过HREF、VSYNC和PCLK同步传输数字图像信号,数据通过{0:9}数据线并行送出给CPU处理

G sensor加速度传感器(三轴加速度传感器)(SPI或I2C接口)

L sensor光感 通过传感器调整LCD背光强度

P sensor距离传感器 通过发送非常短的光脉冲,并检测反射回来的时间,测量物体之间的距离

NFC(近场通信技术)由RFID(非接触射频识别技术)演变而来的,能短距离进行无线数据识别数据交换。工作在13.56MHz频率范围,作用距离大约在10cm,通信传输速度为106Kbps到848Kbps,设备无需配对,无需发现,多以被动连接方式,几乎不损耗电量

目前主流芯片有NXP和博通,其中NXP的PN547使用最为广泛

NFC天线是一种近场耦合天线,耦合方式是线圈磁场耦合,主要通过电磁耦合来交换数据,与手机的射频天线原理(电磁辐射)不同

感应强度与两个线圈的半径,线圈之间的距离,线圈的数量等有关

NFC电路一般有天线匹配电路,NFC芯片,CPU接口部分组成

NFC由接受电路,匹配电路,EMC滤波电路,天线回路组成

蓝牙采用分散式网络结构及快跳频和短包技术,支持点对点及点对多通信,工作在2.4G频段,数据传输速度(1Mbps--60Mbps)

按照通信距离分为Class A和Class B两大类

目前流行的为Class B制式,基于802.11协议

WIFI用2.4GHz和5GHz两个频谱,目前最高为802.11n标准,传输速率达到320Mbps

WIFI模块一般采用USB或SDIO接口与CPU通讯,但是天线端都相同,包括天线和π形匹配网络,走线要求50欧

WIFI和BT共享2.4G频段,所以可以共享滤波和天线结构,仅仅是通讯协议的不同,现在越来越多的平台或芯片把WIFI和BT集中到一颗芯片内,以降低成本

单,双模蓝牙解释

蓝牙无线通讯技术从4.0开始包含两个蓝牙标准,准确来讲,是蓝牙史上第一个双模标准的开始。那么什么是蓝牙双模标准呢?它包含传统蓝牙部分(称为经典蓝牙Classic Bluetooth)和低功耗蓝牙两个部分(Bluetooth Low Energy)。这两个部分分别适用于不同的应用或者应用条件。传统蓝牙(也称之为经典蓝牙)是在之前的1.0.1.2,2.0+EDR,2.1+EDR,3.0+EDR等基础上发展和完善起来的,而低功耗蓝牙是Nokia的Wibree标准上发展起来的。

经典蓝牙可以用数据量比较大的传输,如:图像、视频、音乐等。低功耗蓝牙的数据传输用于实时性要求比较高但数据速率比较低的产品,如智能穿戴设备、遥控类的,鼠标,键盘,遥控鼠标(Air Mouse),还有传感设备的数据发送,如心跳带,血压计,温度传感器等等、其应用的行业和方向也比较广泛。

从蓝牙4.0到蓝牙的最高版本5.0,双模标准一直在延续,所以在这里我要申明的是蓝牙从4.0开始就集成了经典蓝牙和低功耗蓝牙两个标准,并不只是低功耗蓝牙。

GPS的天线要远离干扰源,其中摄像头时钟信号倍频后会在1.5GHz左右,所以天线距离摄像头至少在2cm以上,BT、WIFI、3G等信号源至少1cm以上喇叭、麦克风、LCD屏线至少在2cm以上,天线附近的壳料没有任何金属材料,附近的外壳也不要电镀和喷金属导电漆

GPS卫星信号为L1和L2,频率分别为1575.42MHz和1228MHz

3G通信

移动TD-SCDMA

联通 WCDMA

电信 CDMA2000 1xEV-DO

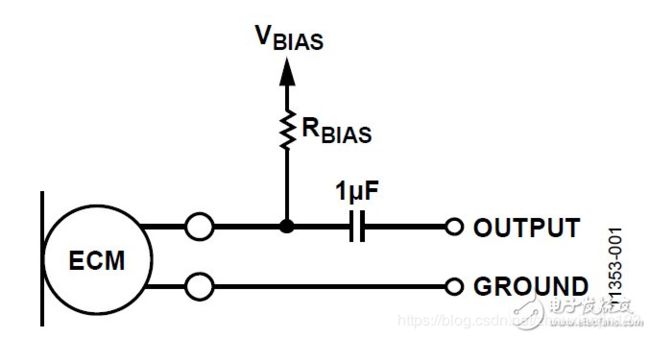

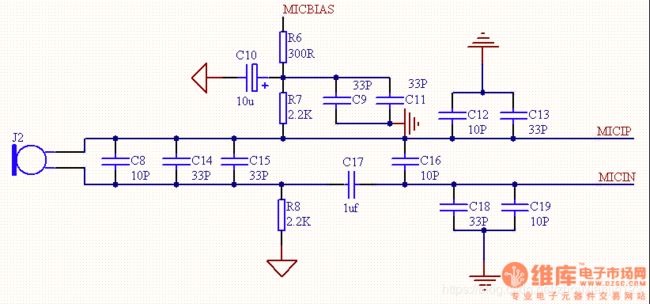

麦克风分为数字和模拟两种

数字式的采用硅工艺,一致性和抗燥性都比较好,但是价格昂贵,是模拟式的3倍以上

实质上是一种电声转换元件,将声音的机械振动转换为电信号和扬声器的作用刚好相反

Vbias偏置电压一般为2--3V,偏执电阻一般为2.2K

单端输出音频

差分输出音频

音频功率放大器分为模拟和数字两大类,模拟功放AB类,数字的有D类

AB类模拟功放能有效的消除交越失真问题,理论效率在50%到70%之间

BTL(桥式负载)能使负载得到单端输出的2倍电压,单端输出4倍的功率

POP噪声问题:音频器件在上电或下电过程中,由于电源对输入输出电容、偏置电容充电引起的音爆,由于电容的瞬态充电

带来的尖峰电压,当该电压加在扬声器负载两端时,就会产生POP噪声,因此应当减小电压的突变,消除噪声

D类数字功放,效率极高90%以上,产生的热量低,未来功放的主流应用

数字功放先将模拟输入信号进行数字化PWM调制,然后进行放大滤波,驱动扬声器

功放参数性能指标:电源纹波抑制比PSRR 总谐波失真度+噪声 最大输出功率 转换效率

I2S音频总线接口信号线

SCLK(也称BCLK),即数字音频的每一位数据都有一个脉冲

LRCK帧时钟,用于切换左右声道的

SDATA用二进制补码表示音频数据

IIS_MCLK(可以由自己产生或主控提供) IIS_BCLK IIS_LRCLK IIS_SDO IIS_SDI

SIM卡在使用的时候最少需要5根连线

Vcc GND RST CLK Data

SIM卡的供电有5V、5V与3V兼容、3V、1.8V

Vcc在SIM卡工作时,提供的电流小于10mA

Clock的工作频率为1-5MHz,典型的为3.25MHz

SIM卡目前有3种,分别为标准卡,小卡Micro SIM卡和微型卡Nano卡

SIM卡检测电路一般要同时支持3V和1.8V卡,因此SIM卡通信引脚必须能兼容这两种电平

TF卡又叫MiscroSD卡,即微型的SD卡,TF卡和SD卡的信号基本相同,只是TF卡体积更小

VCC GND CLK CMD DET DATA{D0:D3}(上拉)

HDMI高清晰多媒体接口

三对数据差分信号,一对差分时钟信号 1.65Gbit X 3=4.96Gbps

HPD 中断检测脚,判断是否插拔

CEC 可以通过遥控器对所连接的HDMI线缆上的设备进行控制

阻抗控制在100欧,ESD结电容小于5pF

等长设计,参考时钟线,四对差分线对间误差小于10Mil,对内误差小于5Mil,

如果是3.4Gbps时,对内保持绝对的等长,尽量采用弧形走线

USB OTG接口(on-the-go),是在没有Host的情况下实现设备之间的数据传送

在传统的基础上增加了一个ID引脚,通过ID引脚电平的控制,设备既可以作主机又可以作外设

ID引脚接GND时,默认作为Host

ID引脚悬空时或默认上拉,初始状态为Device

移动设备如需支持OTG,内部ID引脚需要默认上拉为高

以太网的接口实质是MAC控制器通过MII总线控制PHY芯片的过程

网卡芯片和CPU的连接方式大概分为三种:

MII接口(RTL8201):CPU内置的MII接口的MAC控制器,直接与PHY芯片通信

USB接口(AX88772):CPU直接通过USB接口将网络层协议数据发送给网卡芯片(包含MAC和PHY芯片)

总线接口(W5100):CUP直接和网卡芯片通信(该网卡芯片集成了网络协议和数据链路层MAC控制器以及PHY物理层芯片)

CPU MAC芯片(数据链路层) PHY芯片(物理层)

第三章

FR4板材与高TG FR4板材

Tg值:玻璃态转化温度

一般板材的Tg值为130℃以上,高Tg一般大于170℃,基板的Tg值的提高,则印制板的耐热性、耐潮湿性、化学稳定性等特征都会相应的提高,在无铅制程中高Tg板材应用比较多

PCB表面处理技术:

喷锡(热风平整):最常见工艺,具备良好的可焊接性,成本低廉,不足之处是大面积开窗后表面锡不平整

沉金:无铅,一般用于金手指、按键板等,经常插拔的部件要镀金,沉金是沉镍金

OSP:利用药水与焊接铜皮反应,产生可焊接性,好处是生产快,成本低廉,但可焊接性能差,易氧化,一般用的比较少

镀金:用于经常插拔的部件,硬度高,但是其焊接性差

设计线宽线距往往由于实际的工艺,会存在偏差的现象,计算阻抗的时候需要考虑进去

一般不允许4张及以上的PP片叠压,因为压合时容易发生滑片

7628的PP片不允许放在外层,因为其表面比较粗糙

3张1080的PP片也不允许放置在外层,易发生滑片现象

残铜率的概念

1OZ=0.035mm=1.38mil 铜厚

当钻孔深度超过钻孔直径的6倍时,将无法保证孔壁镀铜的均匀性

BGA在0.65及以上的盘距不推荐使用盲埋孔

过孔不能放置在0402器件的焊盘上,否则生产时锡膏容易进入过孔中,造成锡膏不均匀,器件立起来的现象,

一般推荐过孔到焊盘在4-8mil间距

过孔与过孔的间距不宜过近,否则钻孔时容易引起破孔,一般要求过孔间距在0.5mm及以上

过孔之间保持一定的间距,不破坏平面的完整性为宜

邮票孔链条规范:

链条板宽在2-4mm 链条板长在4-5mm 孔大小为0.3-0.5mm 孔中心间距在1mm左右

通孔器件的焊盘开孔的尺寸一般需要比实际单边略大8mil,方便装配的时候器件插入

为了能在板上清晰的看到器件的位置,一般丝印位置在原基础上外扩0.25mm,丝印尺寸不小于5mil

丝印与焊盘间隙在6mil以上,丝印不要上焊盘,以免引起焊接不良

阻焊开窗设计时,一般单边需略大2.5mil为宜

Wifi与蓝牙天线放置在板子的边缘空旷处,因为其工作时会产生强烈的高频电磁扰动

PCB边缘的元器件离板边距离一般不小于2mm

多层PCB的电源层一般相对于GND层内缩20H,20H一般为2mm

第四章

ESD器件距离接插件最好在1.5mm以上,以便于手工焊接

差分对与对之间尽量包地处理,间隔100mil打地过孔,打孔换层时,需要在过孔附近打两个回流地过孔,用于信号回流

空间紧张时,尽量拉开距离,线边到线边距离在15-20mil左右,四组同时包地处理

尽可能使用小的信号线过孔降低阻抗变动带来的影响,推荐使用8/16mil或8/18mil过孔

网络变压器下方需要完全净空,防止高频干扰信号耦合到GND上

RJ45的金属地和数字地通过一个1M电阻和0.1uF去耦电容隔离连接,隔离宽度在1.5mm以上为宜

麦克输入走类差分形式,走线宽度在12-15mil,并作包地处理,包地线每隔100mil打GND过孔

耳机接口示意

第五章

双面SMT时,要求先过回流焊的一面无太重的器件,因为需要二次过炉,已经焊接好器件的一面的焊点再次融化,仅仅依靠焊料的表面张力附着在PCB下面,较大较重的元器件容易掉落

PCB板上的器件的焊盘与V-CUT的间距应大于或等于1mm为宜

第六章

GND相对于板框内缩20mil,VCC相对于GND内缩40mil

DDR数据线同组同层,差分误差5mil,组内误差控制10mil 组间无需等长,但尽量靠近,误差小于120mil

地址线和控制线都参考时钟线,线长误差控制在100mil以内

注意各CPU模块和相应的模组的电平域的配合

电源走线通用标准:表层20mil=1A 内存40mil=1A 8/16过孔电流负载能力300mA

敏感信号包地处理时,需要50-100mil打上GND过孔

一说0.1uF 0402电容在20-300MHz范围内非常有效