基于FPGA视频图像处理系统设计

摘 要

本报告给出一个基于FPGA+两片DDR2组成的核心板、带有4路视频输入和VGA接口的开发板进行的视频图像采集和处理系统的设计。使用TW2867进行视频输入信号的编码,存储到DDR2中,通过FPGA和ARM的联合控制,通过I2C总线进行通信,进行数字图像处理,实现了单通道视频信号输入屏幕显示、4通过视频信号输入4分屏显示、边沿检测算法,将处理结果通过VGA接口连接到LCD显示器上进行显示。本报告从硬件设计和软件设计两个方面对该基于FPGA的视频图像处理系统的工作过程做了详尽描述。

关键词:视频图像处理、FPGA、边沿检测、4分屏显示

1、设计目的

图像处理技术和机器视觉作为一门前沿的技术,为人们的生活和工作带来了极大的便利和愉悦。由于视频信号的数据量大,信号较为复杂,这就要求视频信号处理系统具有实时采集、大容量存储和实时处理的特点。本报告提出基于现场可编程门阵列FPGA的视频图像采集与处理系统设计方案,利用FPGA并行处理快速的特点,辅以图像处理算法,用以获得不同需求的视频图像,并通过VGA显示器进行实时显示。

2、设计任务与性能指标

本系统中主要是通过AV接口实现视频图像采集,将采集到的4路模拟电视信号进行格式编码转换成数字信号,存储在DDR2中作为缓存,供FPGA处理器进行数字图像的处理,处理的结果再通过视频编码芯片转换为模拟电视信号通过VGA接口完成基于LCD显示器的4分屏视频图像显示功能,在图像处理中完成边缘检测算法的实现。

3、系统总体设计与工作原理

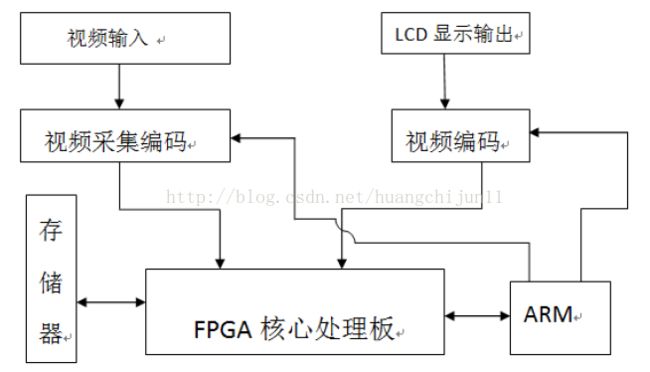

本系统由视频图像采集模块、存储模块、显示模块以及相关配置电路模块组成。采集模块通过视频通过解码芯片TW2867将通过AV接口连接的摄像头拍摄到的视频模拟信号转变为ITU-RBT656格式的数字视频信号;存储模块选取解码后的一帧图像数据的有效大小存入DDR2存储器中,在处理进行前和处理进行中,作为未得到处理的图像数据信息的缓存;显示模块从存储器中读出图像数据,再通过视频编码芯片ADV7123视频D/A转换芯片进行格式转换输出模拟信号,通过VGA接口在LCD液晶显示器上进行显示处理后的效果和采集显示的视频信息。

在原理框图1中可以看到有4路视频输入信号,选择4路输入信号是因为要实现4分屏分割显示4路摄像头采集到的信息,因为摄像头硬件资源的欠缺,只使用了两个摄像头但是原理是完成实现了,只要安装够4个视频输入就一定可以显示4路视频信息。

图1系统设计原理

3 . 1 系统硬件设计

因为本系统设计是基于黑金动力社区的FPGA视频处理开发平台实验板进行的,因此所使用的硬件电路也是该开发板上搭载的实验器件,均是已经较为成熟的视频图像采集与处理硬件设备。实验板型号为ALINX822 REV3.0,在该实验板上整个开发板的结构继承了一贯的核心板和扩展板的模式进行设计的。核心板主要由FPGA+两片DDR2构成,承担视频图像处理的核心算法,充分利用了FPGA并行处理的能力,加上两片DDR2构成32bit总线,整个系统的带宽高达10Gb/s,两片DDR2容量高达2Gbit,满足视频处理过程中对高缓冲区的需求。该实验板选用的FPGA为ALTERA公司CYCLONE IV系列中速度级别最高的C6级别,可以实现FPGA和DDR2之间的时钟频率达到200M,DDR2内部400M,充分满足了四路1080P视频处理的需求。

图2开发板实物图

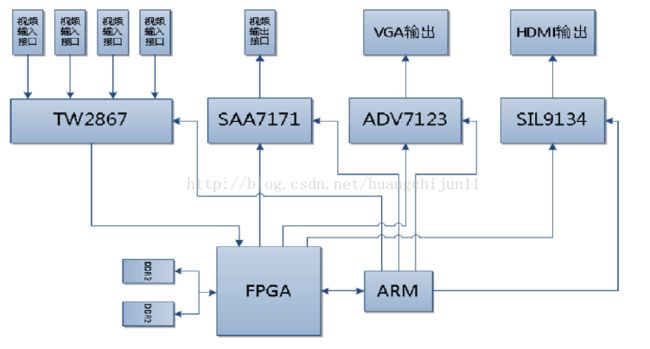

上图2是使用的开发板的实物图,从上面可以看到其实验板的型号,搭载的器件的一些型号信息,中间的即为核心板,核心板下面则是一块更大面积的扩展板,扩展板上则分布着VGA接口、HDMI接口、视频输出接口、视频输入接口、ARM控制器、扩展口、SD卡槽等器件。从下图3中可以看到整个开发板的系统结构图。

图3开发板结构图

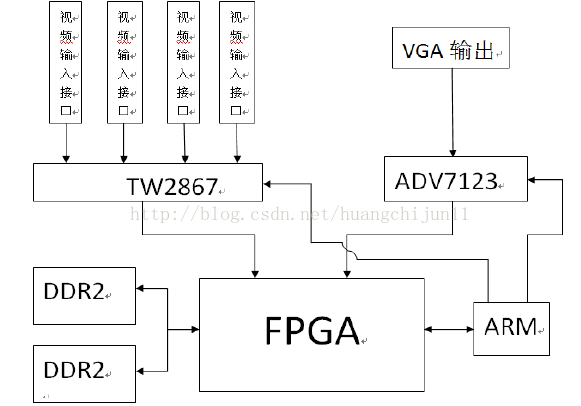

本系统所使用到的器件框架结构图在图4中可以清晰地看到,跟整个开发板结构图相比,没有使用到视频输出接口和HDMI接口,其他则都用到了。TW2867是为了将视频输入接口采集到的视频信号进行编码成数字信号,ADV7123是将经过处理后的数字信号转为模拟电视信号,以供VGA接口连接显示器进行LCD屏的显示。

图4 硬件设计原理框图

3.2单元电路设计

1,采集模块

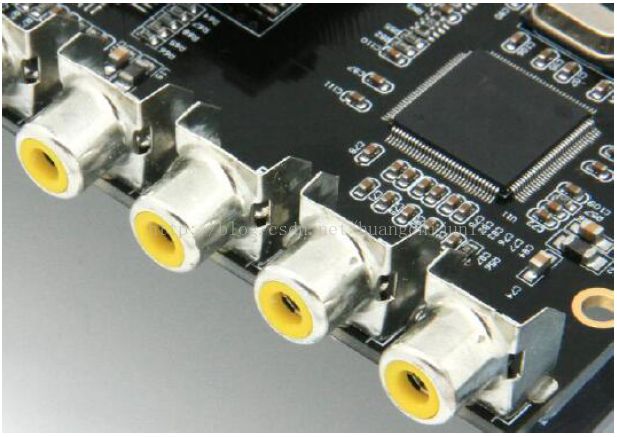

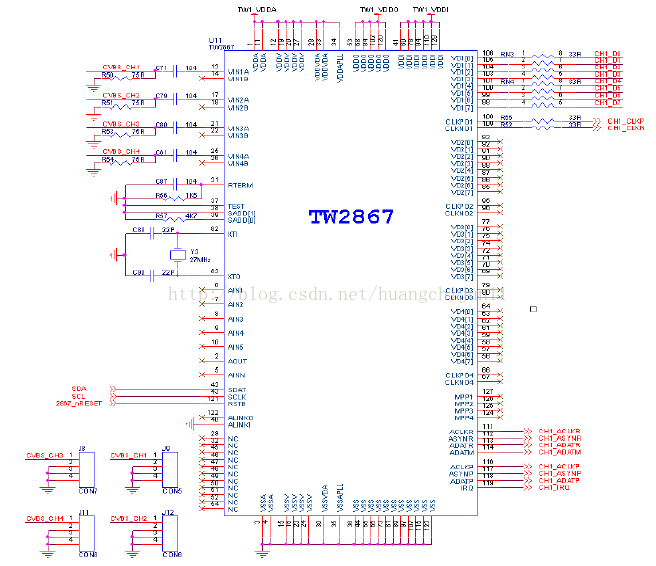

采集模块是选用了Techwell公司的TW2867,可以输入4路符合视频信号,PAL/NTSC/SECAM自动识别,输出BT656,可多路复用总线,FPGA端解复用,节省IO,其中TW2867的IIC接口和复位引脚与STM32F103相连,通过STM32F103来对TW2867进行初始化和控制操作,其他引脚与FPGA相连。在图5中,可以看到4路视频输入接口跟TW2867相连接,实现4路视频输入。

与ARM对应引脚如下表1所示:

表1 ARM引脚对应表

| 引脚名称 |

ARM引脚 |

| SDA |

39 |

| SCL |

40 |

| 2867_NRESET |

41 |

图5视频输入接口实物图

与FPGA对应引脚如下表2所示:

表2 FPGA引脚对应表

| 引脚名称 |

FPGA引脚 |

| cvbs_in_cikp |

P20 |

| cvbs_in_cikn |

N19 |

| cvbs_in_data[0] |

M19 |

| cvbs_in_data[1] |

N20 |

| cvbs_in_data[2] |

M20 |

| cvbs_in_data[3] |

T17 |

| cvbs_in_data[4] |

P17 |

| cvbs_in_data[5] |

R17 |

| cvbs_in_data[6] |

N18 |

| cvbs_in_data[7] |

N17 |

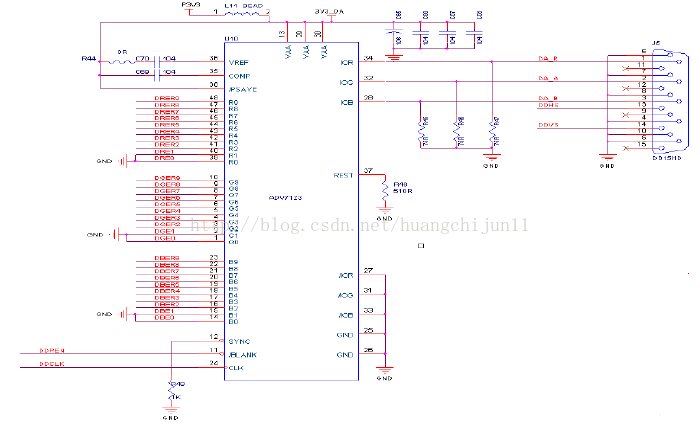

图6电路设计连接图

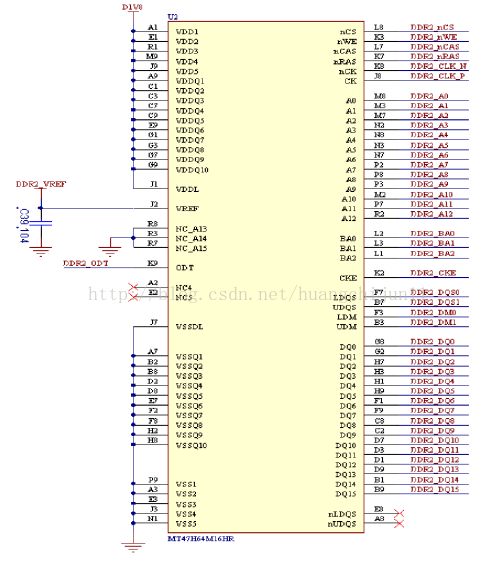

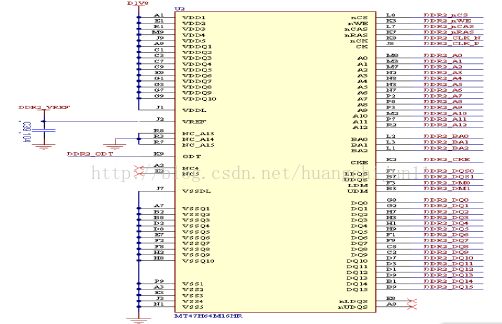

2,存储模块

本部分完成图像数据在DDR2中的帧存,为后端图像进一步处理做好准备,图像数据采集后需要进行图像处理,在处理进行前和处理进行中,未得到处理的图像数据信息需放置在帧缓存中。存储模块是使用了DDR2芯片,容量为1Gbit,两片DDR2芯片构建32bit总线模式,2G容量,带宽高达10Gb,可以满足4路1080p视频处理的需求。

图7 DDR2实物图

图8 DDR2电路图

在下表3中可以看到DDR2引脚对应表:

表3 DDR2引脚对应表

| 引脚名称 |

FPGA引脚 |

引脚名称 |

FPGA引脚 |

| mem_addr[0] |

U10 |

mem_addr[8] |

AA3 |

| mem_addr[1] |

Y6 |

mem_addr[9] |

U13 |

| mem_addr[2] |

T16 |

mem_addr[10] |

V6 |

| mem_addr[3] |

R14 |

mem_addr[11] |

AB3 |

| mem_addr[4] |

AA4 |

mem_addr[12] |

U14 |

| mem_addr[5] |

T11 |

mem_ba[0] |

U7 |

| mem_addr[6] |

AB5 |

mem_ba[1] |

AB10 |

| mem_addr[7] |

T14 |

mem_ba[2] |

T9 |

| mem_cas_n |

R15 |

mem_dq[15] |

W10 |

| mem_cke[0] |

U8 |

mem_dq[16] |

AB15 |

| mem_clk[0] |

AA17 |

mem_dq[17] |

W13 |

| mem_clk_n[0] |

AB17 |

mem_dq[18] |

AB14 |

| mem_cs_n[0] |

Y17 |

mem_dq[19] |

AA13 |

| mem_dm[0] |

V5 |

mem_dq[20] |

AB13 |

| mem_dm[1] |

AA7 |

mem_dq[21] |

AA14 |

| mem_dm[2] |

AA10 |

mem_dq[22] |

U12 |

| mem_dm[3] |

AA16 |

mem_dq[23] |

AA15 |

| mem_dq[0] |

V8 |

mem_dq[24] |

T15 |

| mem_dq[1] |

W6 |

mem_dq[25] |

V15 |

| mem_dq[2] |

W8 |

mem_dq[26] |

W17 |

| mem_dq[3] |

W7 |

mem_dq[27] |

AB16 |

| mem_dq[4] |

Y3 |

mem_dq[28] |

V14 |

| mem_dq[5] |

Y7 |

mem_dq[29] |

AB20 |

| mem_dq[6] |

AA5 |

mem_dq[30] |

W15 |

| mem_dq[7] |

U9 |

mem_dq[31] |

AB18 |

| mem_dq[8] |

AA9 |

mem_dqs[0] |

V10 |

| mem_dq[9] |

AB8 |

mem_dqs[1] |

AB9 |

| mem_dq[10] |

Y10 |

mem_dqs[2] |

Y13 |

| mem_dq[11] |

AA8 |

mem_dqs[3] |

V13 |

| mem_dq[12] |

AB7 |

mem_odt[0] |

R16 |

| mem_dq[13] |

V11 |

mem_rs_n |

T10 |

| mem_dq[14] |

Y8 |

mem_we_n |

V7 |

3,显示模块

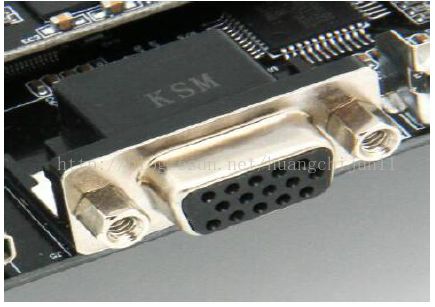

本部分完成从DDR2中读出图像数据,通过视频编码芯片ADV7123输出模拟视频信号,通过VGA接口连接电脑LCD液晶显示器,在电脑屏幕上就可以看见处理的各种结果。图9可以看到VGA接口的实物图,有15个针孔,供接线用。

图9 VGA接口实物图

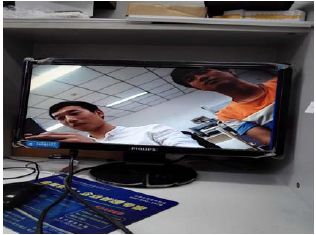

图10VGA接线实物图 图11 LCD显示器实物显示

图12 ADV7123原理图

图10是直接展示了VGA接口跟带VGA接口线的LCD显示器的实物连接图,图11则展示了连接后的LCD效果图,在图12中可以看到ADV7123芯片与VGA接口的链接原理图。

表4给出了对应的引脚接线:

表4引脚对应表

| 引脚名称 |

FPGA引脚 |

引脚名称 |

FPGA引脚 |

| vga_out_clk |

M6 |

vga_out_rgb_g[2] |

T4 |

| vga_out_hs |

N6 |

vga_out_rgb_g[3] |

M1 |

| vga_out_vs |

V3 |

vga_out_rgb_g[4] |

M2 |

| vga_out_de |

P2 |

vga_out_rgb_g[5] |

N1 |

| vga_out_rgb_b[0] |

R1 |

vga_out_rgb_g[6] |

N2 |

| vga_out_rgb_b[1] |

R2 |

vga_out_rgb_g[7] |

P1 |

| vga_out_rgb_b2] |

M7 |

vga_out_rgb_r[0] |

J1 |

| vga_out_rgb_b[3] |

M8 |

vga_out_rgb_r[1] |

K8 |

| vga_out_rgb_b[4] |

P7 |

vga_out_rgb_r[2] |

L6 |

| vga_out_rgb_b[5] |

N7 |

vga_out_rgb_r[3] |

M3 |

| vga_out_rgb_b[6] |

R7 |

vga_out_rgb_r[4] |

L8 |

| vga_out_rgb_b7] |

P6 |

vga_out_rgb_r[5] |

M4 |

| vga_out_rgb_g[0] |

P4 |

vga_out_rgb_r[6] |

N5 |

| vga_out_rgb_g[1] |

R5 |

vga_out_rgb_r[7] |

P3 |

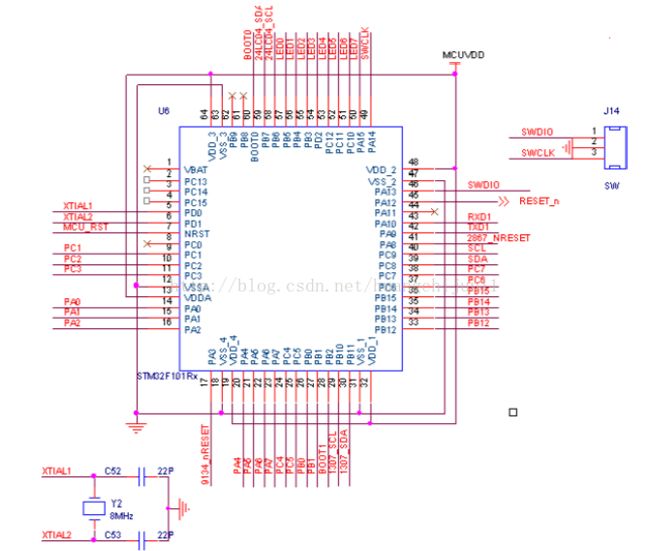

4,ARM控制器

STM32F103使用高性能的ARM® Cortex™-M3 32位的RISC内核,工作频率为72MHz,内置高速存储器(高达128K字节的闪存和20K字节的SRAM),丰富的增强I/O端口和联接到两条APB总线的外设。所有型号的器件都包含2个12位的ADC、3个通用16位定时器和1个PWM定时器,还包含标准和先进的通信接口:多达2个I2C接口和SPI接口、3个USART接口、一个USB接口和一个CAN接口。

STM32F103中等容量增强型系列产品供电电压为2.0V至3.6V,包含-40°C至+85°C温度范围和-40°C至+105°C的扩展温度范围。一系列的省电模式保证低功耗应用的要求。STM32F103xx中等容量增强型系列产品提供包括从36脚至100脚的6种不同封装形式;本系统使用的是64引脚的芯片。

图13 STM32F103实物

图14 STM32F103原理图

3.3器件选择与参数确定

(1),FPGA型号选择及参数

FPGA是选用的ALTERA公司的CYCLONEIV系列的EP4CE30F23C6这款开发的高性能核心板,适合视频图像处理和高速数据采集等方面使用。

(2),数据采集芯片

数据采集芯片是选用了Techwell公司的TW2867,可以输入4路符合视频信号,PAL/NTSC/SECAM自动识别,输出BT656,可多路复用总线,FPGA端解复用,节省IO,其中TW2867的IIC接口和复位引脚与STM32F103相连,通过STM32F103来对TW2867进行初始化和控制操作,其他引脚与FPGA相连。

(3),DDR2

存储模块是使用了DDR2芯片,选用了MICRON公司的MT47H64M16HR这款DDR2芯片,容量为1Gbit,两片DDR2芯片构建32bit总线模式,2G容量,带宽高达10Gb,可以满足4路1080p视频处理的需求。

(4),VGA输出编码芯片

VGA显示部分,使用了ADI公司的ADV7123,最高可以支持1080p@60Hz输出。

(5),ARM

ARM选择的是STM32F103,其使用高性能的ARM® Cortex™-M3 32位的RISC内核,工作频率为72MHz,内置高速存储器,丰富的增强I/O端口和联接到两条APB总线的外设。

(6),模拟摄像头

采用CCD摄像头,红外发射灯,人眼不可见。在黑暗的环境里可以实现实时视频监控,夜视距离10m以内。

4、系统软件设计

-

I2C总线

I2C总线是Philips公司提出的一种允许芯片间在简单的二线总线上工作的串行接口和软件协议,主要用于智能集成电路和器件间的数据通信。I2C总线具有以下特征:

1只有两条总线线路:1条串行数据线(SDA)和1条串行时钟线(SCL)。

2每个连接到总线上的器件都可以由软件以唯一的地址寻址,并建立简单的主从关系,主器件既可以作为发送器,也可以作为接收器。

3它是一个真正的多主机总线,带有竞争检测和仲裁电路,可使多个主机任意同时发送数据而不破坏总线上的数据信息。

4同步时钟允许器通过总线以不同的波特率进行通信。

5同步时钟可以作为停止和重新启动串行总线的握手方式。

(1)I2C总线时序

I2C总线上的数据传输由起始信号,START条件发起,停止信号STOP条件结束。在I2C总线技术规范中,起始和停止条件的定义如图15所示。当时钟线SCL为高电平时,数据线SDA从高电平向低电平切换表示开始传送数据;当SCL线为高电平时,SDA线由低电平向高电平表示停止传送数据。起始和停止条件一般由主机产生。总线在起始条件后被认为处于忙状态,在停止条件产生一段时间后中总线被认为再次处于空闲状态。

图15 I2C总线时序

(2)I2C总线配置

TW2867的I2C总线配置时其接口的功能可以由两个模块来实现,其中I2C_CTR用来控制产生I2C总线的时序,I2C_cmd用来配置TW2867的命令参数的配置。

为了对总线上的设备进行控制,必须制定一个特定的协议,即为I2C总线协议:首先I2C总线控制器建立一个数据传输开始的条件:SCL为高,SDA由高电平变向低电平。外围设备监控SDA和SCL,等待开始条件和正确的传输地址。开始条件到达以后,紧接着送出一个8位寄存器地址(7位地址和1位读写信号)。当SCL为高、SDA从低到高时,表示一次传输完成,等待下一次传输开始。

-

TW2867寄存器配置

通过设定TW2867的内部寄存器来设定、实现TW2867的各种功能。本设计的TW2867功能是采集PAL制式的模拟信号,并在27MHz频率下进行D/A转换,以输出8位宽、格式为YCbCr 4:2:2的数字信号。寄存器配置表如表5寄存器配置表

表5寄存器配置表

| 寄存器地址 |

80 |

60 |

61 |

FC |

7F |

D0 |

E1 |

| 设置参数 |

3F |

15 |

03 |

FF |

80 |

88 |

C0 |

| 寄存器地址 |

D2 |

D3 |

D7 |

D13 |

DC |

E0 |

F8 |

| 设置参数 |

01 |

10 |

32 |

E1 |

00 |

10 |

C4 |

| 寄存器地址 |

E2 |

E3 |

F0 |

F1 |

F2 |

70 |

|

| 设置参数 |

AA |

AA |

83 |

B5 |

09 |

08 |

|

| 寄存器地址 |

73 |

7B |

7C |

7E |

89 |

D1 |

|

| 设置参数 |

01 |

15 |

15 |

C0 |

01 |

88 |

|

-

视频信号采集

(1)ITU_RBT.656标准

目前,数字视频的国际标准是国际电联的ITU_RBT.656格式。ITU_RBT.656标准是在国际电信联盟无线电通信部门656—3号建议书中提出来的,它的全称是工作在ITU-RBT.656建议的4:2:2级别上的525行和625行电视系统中的数字分量视频信号的接口。实施这种标准是为了在525行和625行两者间具有最大的共同性,同时提出一种世界范围兼容的数字方法。该标准在单一信号源与单一终点直接提供了单向互联。数字信号采用编码成8比特字(也可认为是10比特字)的二进制信息的形式。这些信号是:视频信号、定时基准信号和辅助信号。

(2)采集数据

摄像头采集到的视频数据经过解码芯片进行A/D转换后得到的是4:2:2视频数据流。ITU解码模块将根据ITU656标准将4:2:2的数据流解码成ITU656标准视频流。ITU656并行接口除了传输4:2:2 YCbCr 视频流外,还有行、场同步所用的控制信号。PAL制式的图像525行,每秒扫描30帧,每行数据由1728字节的数据块组成。

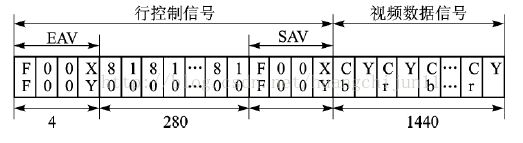

在下图16ITU656行数据结构图中,可以看到每行数据包含水平控制信号和YCbCr视频数据信号。视频数据信号字是以27mb/s的速率传输的,其顺序是:Cb、Y、Cr、Y、Cb、Y、Cr….,其中Cb、Y、Cr这三个字指的是同址的亮度和色差信号取样,后面的Y字对应于下一个亮度取样。每行开始的288字节为行控制信号,开始的4字节为EAV信号(有效视频结束),紧接着280固定填充数据,最后4字节的SAV信号(有效视频起始)。

图16 ITU656行数据结构图

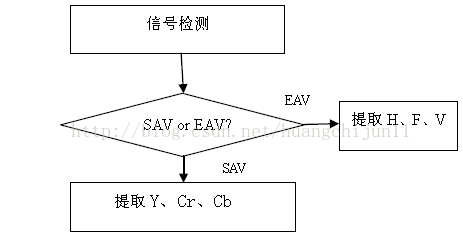

SAV和EAV信号有3字节的前导:FF、00或EAV信号,提取H、F、V信号,然后发送00;最后1字节XY表示该行位于整个数据帧的位始命令,同时开启行列计数器,开始对接下来的位置区分SAV、EAV.在每个时钟的上升沿图像数据进行解码,读取从解码芯片传来的8位数图4视频解码流程据.若检测到一行信息,判断该数据为Y、Cr还是Cb,得到数据的开始标志FF0000XY,从而检测到SAV信号Y、Cr、Cb各分量的值.视频解码流程如图17所示.

图17视频编码流程图

表6为定时基准信号格式.其中,F为场标志位,第一场为“0”,第二场为“1”;V为“0”表示处于有效数据期,为“1”表示处于场消隐期;H为“0”,则为SAV信号,表示一个数据块的开始,为“1”则是EAV信号,指示一个数据块的结束;P2、P1、P0是保护比特位,其值取决于F、H、V的值.根据这个特征,接收模块可以建立状态机,仅当状态严格完成FFG00G00的转换才开始采集有效数据,送入SDRAM进行存储.

表6 定时基准信号格式表

| 比特 |

第一个字(FF) |

第二个字(00) |

第三个字(00) |

第四个字(XY) |

| 9 |

1 |

0 |

0 |

1 |

| 8 |

1 |

0 |

0 |

F |

| 7 |

1 |

0 |

0 |

V |

| 6 |

1 |

0 |

0 |

H |

| 5 |

1 |

0 |

0 |

P3 |

| 4 |

1 |

0 |

0 |

P2 |

| 3 |

1 |

0 |

0 |

P1 |

| 2 |

1 |

0 |

0 |

P0 |

| 1 |

1 |

0 |

0 |

O |

| 0 |

1 |

0 |

0 |

O |

4,DDR2存储

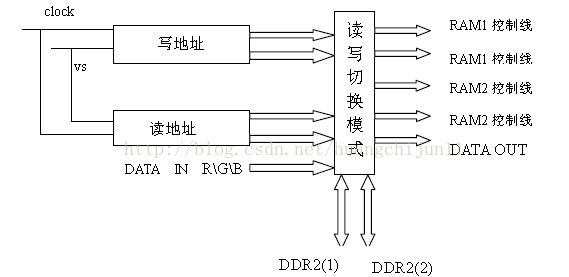

本系统使用的是SDRAM的输入输出缓存电路为FIFO结构,把SDRAM设置为4个端口模式,两个端口用于把FIFO的数据送入DDR2,另外两个端口用于把数据从DDR2中读到FIFO中。读和写操作采用的时钟频率不同,写用的是解码芯片的27MHz时钟,而读出采用VGA的25MHz时钟。

FPGA对DDR2进行控制时,首先是对DDR2的初始化进行配置,写寄存器,确定CAS的潜伏期、突发传输模式等,然后再经过激活命令激活对应地址的bank,同时输入行地址,最后通过读命令或者写命令输入列地址,将相应数据读出或写入对应的地址。DDR2的存储单元每隔一段时间刷新以保持数据稳定,否则数据丢失的可能性比较大。两个DDR2循环读写切换,分别为:在一帧时间内显示器接收的图形信号,它的产生是在同步信号(VS)经过二分频后,若VS为低电平,向一个DDR2中写入数据,反之从该DDR2中读取数据。在完成读写地址的信号切换后,数据输出切换也是必须的。

图18 DDR2工作图

5, VGA和LCD显示

从DDR2中存储的是4:2:2格式的视频数据,由于该格式视频的每个像素点都不包含色度分量和亮度分量,从中读取数据后,必须将格式转换成4:4:4的视频数据格式,因此转换后Cb、Y、Cr是全面的。为了使得VGA显示器能够显示该视频,首先VGA使用的是RGB色彩空间,必须将数据经过从Cb、Y、Cr到RGB模块转换,其次是将之前转换好的YCbCr空间再次转换为RGB空间,再次输出到VGA控制器,在此过程中,输出24位RGB数据到编码芯片ADC7123,输出的数据还包括VGA_HA\VGA_VS信号。

6,Sobel边沿检测的实现

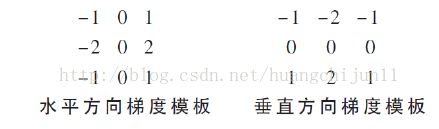

Sobel边沿检测算法是一种基于梯度的图像边沿检测方式,该算法在硬件上容易实现,且能够平滑一定的噪声,边沿检测效果较好。Sobel算子的边沿检测是在图像空间内利用2个方向模板与图像进行相邻卷积来完成的。这两个方向模板,一个为检测水平边沿,一个是检测垂直边沿。它们的方向梯度算子模板如下:

图19梯度算子图

以模板内的数字为权重系数,与图像平面所对应的像素值相乘可以求出水平梯度X和垂直梯度Y,然后根据梯度计算公式可以求出梯度G为X与Y各自平方的和的平方根。

5、系统安装调试

-

一路视频信号采集显示

从图20和21中可以看到系统成功实现了视频图形采集和VGA显示,这里只截取了两个场景的图像。

图20单视频输入1 图21单视频输入2

-

4路视频信号采集显示

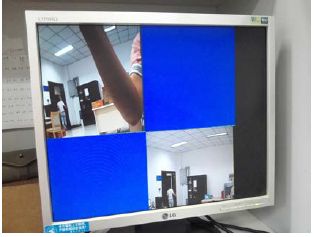

通过图22、23、24、25可以清楚地看到整个系统的接线布局图,因为只有两个摄像头,所以只能采集到两个视频输入信号,因此在屏幕上只显示出来了两个窗口信息,另外两个窗口是蓝屏显示。在原理上实现了4路视频分割4分屏显示。

图22整体系统连接图 图23 路视频输入4分屏显示1

图24路视频输入4分屏显示2 图25 实物连接图

-

边沿检测

图26未边沿检测图 图27边沿检测1对比图

从图26和图27中可以看到未边沿检测图形和边沿检测后的图形明显不同,可以看到在图27中有明显的边沿轮廓,即实现了Sobel算法的边沿检测功能。图28和29是另外两个场景的边沿检测效果图。

图28边沿检测2 图29 边沿检测3

6、出现问题与解决方法

-

I2C总线配置问题

因为最开始对TW2867的I2C总线配置没有按照I2C总线规范和标准时序来进行,所使用的时序关系跟图15中的时序关系不同。对SDA和SCL的变化规律不清除,不能把握数据传输的开始条件,也不能监控何时传输完成,因此对后面的工作产生影响。通过查阅TW2867芯片资料和网上搜集信息最后解决了这一问题。

-

寄存器配置问题

对于TW2867寄存器配置存在问题,同样是对此芯片的寄存器地址设定的参数不符合系统要求,这些参数是通过I2C_cmd模块得出来的,总开始仅仅让I2C_ctr来控制产生I2C总线的时序,却忽视了I2C_cmd的配置的重要性。

-

下载电路驱动问题

最开始连接不了开发板,因为USB的下载驱动没有安装上去,后来安装后得以成功将程序烧录到板子里,从而进行实验展示。

-

参数设定问题

对视频输入信号的格式、经过TW2867处理后的格式不了解,因为要输出显示在VGA显示器上,中间视频信号从输入到显示整个过程中的信号的A/D、D/A转换、编解码的状态不是特别清楚,以至于在有些参数设定的小问题上出现错误,另一方面对于解码芯片的时钟频率等出现模糊理解等问题,最后参考网上别人的示例才得以解决。

-

边沿检测算法的设计

边沿检测算法有很多种类,比较常见的就是本系统中使用的那样,求水平和垂直分量的平方和的根,之前采用一种更复杂的算法,因为一些原因没能得以实现,巧合中看到有前辈使用这种简单算法进行边沿检测,同样也得出了比价不错的结果。

7、总结

基于FPGA的视频图像采集与处理系统相对于使用其他硬件进行处理的效果更好,有更多的优势,而且成本低、功耗低、信噪比高、电路集成度高、速度快且接口方便。本系统在设计的过程中,选用的芯片也是比较成熟的各类处理芯片,特别是FPGA是使用ALTERA公司的CYCLONE IV系列的EP4CE30F23C6这款开发的高性能核心板,适合视频图像处理和高速数据采集等方面使用。基于FPGA的视频图像处理可以为嵌入式系统开发、人脸识别技术的产品化、无线视频传输等应用提供了一定的参考价值。本系统是完成一个基本的显示功能和边沿检测算法的实现,虽然简单但也涉及到使用FPGA进行图像处理的各个方面,为以后的研究有一定的引导作用,适合深入地研究下去,结合数字图像处理、人脸识别等图像技术在将来会有更好的工程实践效果。

8、附件

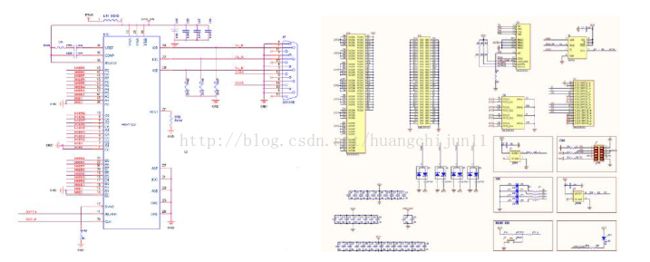

8.1原理图(用Protel制作)

ADV7123原理图 FPGA原理图

DDR2原理图

8.2程序清单

Sobel算法重点程序

Sobel Sobel_m0(

.iCLK(vga_out_clk),

.iRST_N(rst_n),

.iTHRESHOLD(8'd50),

.iDVAL(ch0_vout_rd_req_d1),

.iDATA({ch0_vout_ycbcr[23:16],2'd0}),

.oDVAL(),

.oDATA(Sobel_data)

);

8.3程序清单

采集视频信号程序

video_pro#(.MEM_DATA_BITS(MEM_DATA_BITS))video_pro_m0(

.rst_n(1'b1),

.vin_pixel_clk(cvbs_in_clkn),

.vin_vs(ch0_vs),

.vin_f(ch0_f),

.vin_pixel_de(ch0_de),

.vin_pixel_yc(ch0_yc_data),

.vin_scaler_clk(phy_clk),

.vin_s_width(12'd720),

.vin_s_height(12'd576),

.clipper_left(12'd0),

.clipper_width(12'd720),

.clipper_top(12'd0),

.clipper_height(12'd576),

.vin_t_width(12'd720),

.vin_t_height(12'd576),

.vin_K_h(16'h0100),

.vin_K_v(16'h0100),

.vout_pixel_clk(vga_out_clk),

.vout_vs(vga_out_vs),

.vout_pixel_rd_req(ch0_vout_rd_req),

.vout_pixel_ycbcr(ch0_vout_ycbcr),

.vout_scaler_clk(vga_out_clk),

.vout_s_width(12'd720),

.vout_s_height(12'd576),

.vout_t_width(12'd720),

.vout_t_height(12'd576),

.vout_K_h(16'h0100),

.vout_K_v(16'h0100),

///////////mem

.mem_clk(phy_clk),

.wr_burst_req(ch0_wr_burst_req),

.wr_burst_len(ch0_wr_burst_len),

.wr_burst_addr(ch0_wr_burst_addr),

.wr_burst_data_req(ch0_wr_burst_data_req),

.wr_burst_data(ch0_wr_burst_data),

.wr_burst_finish(ch0_wr_burst_finish),

.rd_burst_req(ch0_rd_burst_req),

.rd_burst_len(ch0_rd_burst_len),

.rd_burst_addr(ch0_rd_burst_addr),

.rd_burst_data_valid(ch0_rd_burst_data_valid),

.rd_burst_data(ch0_rd_burst_data),

.rd_burst_finish(ch0_rd_burst_finish),

.base_addr(2'd0)

);

4分屏显示重要程序

vout_display_pro vout_display_pro_m0(

.rst_n(rst_n),

.dp_clk(vga_out_clk),

.h_fp(H_FP[11:0]),

.h_sync(H_SYNC[11:0]),

.h_bp(H_BP[11:0]),

.h_active(H_ACTIVE[11:0]),

.h_total(H_TOTAL[11:0]),

.v_fp(V_FP[11:0]),

.v_sync(V_SYNC[11:0]),

.v_bp(V_BP[11:0]),

.v_active(V_ACTIVE[11:0]),

.v_total(V_TOTAL[11:0]),

.hs(vga_out_hs),

.vs(vga_out_vs),

.de(vga_out_de),

.rgb_r(vga_out_rgb_r),

.rgb_g(vga_out_rgb_g),

.rgb_b(vga_out_rgb_b),

.layer0_top(12'd0),

.layer0_left(12'd240),

.layer0_width(12'd720),

.layer0_height(12'd576),

.layer0_alpha(8'hff),

.layer0_rdreq(ch0_vout_rd_req),

.layer0_ycbcr(ch0_vout_ycbcr),

.layer1_top(12'd0),

.layer1_left(12'd960),

.layer1_width(12'd720),

.layer1_height(12'd576),

.layer1_alpha(8'hff),

.layer1_rdreq(ch1_vout_rd_req),

.layer1_ycbcr(ch1_vout_ycbcr),

.layer2_top(12'd576),

.layer2_left(12'd240),

.layer2_width(12'd720),

.layer2_height(12'd576),

.layer2_alpha(12'hff),

.layer2_rdreq(ch2_vout_rd_req),

.layer2_ycbcr(ch2_vout_ycbcr),

.layer3_top(12'd576),

.layer3_left(12'd960),

.layer3_width(12'd720),

.layer3_height(12'd576),

.layer3_alpha(12'hff),

.layer3_rdreq(ch3_vout_rd_req),

.layer3_ycbcr(ch3_vout_ycbcr)

);

参考文献

[1]王诚,蔡海宁,吴继华.AlteraFPGA/CPLD设计(基础篇)[M].2版.北京:人民邮电出版社,2011:5058

[2]夏良正.数字图像处理[M].南京:东南大学出版社,1999:154 160.

[3]姜勇.基于FPGA的实时图像处理系统的研究:[硕士学位论文].长春:长春理工大学,2003

[4]张永军.基于FPGA的图像处理系统设计与算法实现研究[D],重庆大学,2006

[5]万鸣华.基于FPGA的图像处理加速研究[D],南京理工大学,2007

[6]阮秋琦.数字图像处理学(第二版)[M].北京,电子工业出版社,2007

[7]龚声蓉,刘纯平,王强等.数字图像处理与分析[M],北京,清华大学出版社,2006

[8]蒋立东.VHDL语言程序设计及应用.北京:北京邮电大学出版社,2001.8

[9]刘文英,刘艳彬.基于FPGA的视频图像预处理系统的设计与实现。科技信息,2011,23:41-42

[10]邵应昭,任爱峰,初秀琴.基于FPGA的视频监控系统.电子元件器应用,2010,12(12):24-26

[11]张海青.基于FPGA图像处理系统的关键算法研究及硬件实现:[硕士学位论文].江苏:江苏大学,2005

[12]孙伟.基于FPGA的图像分割提取系统研究:[硕士学位论文].南京:南京航空航天大学,2010

[13]相恒伟.基于FPGA的CCD工业相机的研究与开发:[硕士学位论文].江苏:江南大学