触发器及其电路分析

概述

时序电路是数字逻辑课程的核心部分,也是学习后续硬件相关课程的重要基础部分,PC中的计数器、内存、倍频/分频器等都是典型的时序电路。

前面学习的组合电路,电路的输出只与电路的输入相关,不具备保存数据功能,电路中也不允许存在回路。而在时序电路中,一大功能便是要求保存数据。时序电路通常分为Moore型和Mealy型,Moore型电路的输出只与电路的当前状态(就是存储的数据)相关,Mealy型电路则与电路的当前状态和输入相关。

时序电路中的基本元件要求具有保存一个数据位(值为“0”或1)的功能,并且要求稳定。时序电路元件分为锁存器和触发器两种,锁存器利用电平进行控制,触发器利用时钟脉冲进行控制(请看后面的具体分析)。

基本锁存器

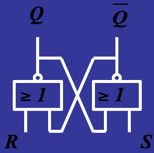

基本锁存器的示意图如下所示:

基本锁存器,只要上电(满足0和1的电压要求),必然能处在一个稳态。如图1中,Q为1时,Q为1保证!Q为0,!Q为0又保证Q为1,电路始终维持在一个稳态,这时称Q为1状态;同理,图2称Q为0状态。

R-S锁存器

显然,前面提到的基本锁存器虽然能保存数据,并且可以处于稳态,但是基本锁存器无输入端(初始电压即决定了电路的状态,并且保持不变),不受控,无法灵活运用。为此,聪明的设计师遍发明了R-S锁存器,其电路如图3所示:

图3中展示的是一个由两个或非门组成的R-S锁存器,根据示意图,可以得出如下公式:

Qt+1 = !(R+!Qt)

!Qt+1 = !(S+Qt)

对R、S置不同值进行分析:

- R = 0, S = 0,此时,若初始Q为0,!Q为1,则S和Q的共同作用,使!Q为1,!Q为1和R共同作用,确保Q为0,Q保持0状态;若初始Q为1,则S和Q的共同作用,使!Q为0,!Q为0和R共同作用,确保Q为1,Q保持1状态;

- R = 0, S = 1, 此时,若初始Q为0,!Q为1,则S和Q共同作用,使!Q为0,!Q(为0)和R,共同作用确保Q为1;若初始Q为1,!Q为0,则Q和S确保!Q为0,!Q(为0)和R,共同作用确保Q为1;

- R = 1, S = 0, 若初始Q为0,!Q为1,则Q和S共同作用,使!Q为1,!Q(为1)和R共同作用,确保Q为0;若初始Q为1,!Q为0,则Q和S共同作用,使!Q为0,!Q(为0)和R共同作用,确保Q为0;

- R = 1, S = 1, 若初始Q为0,!Q为1,则Q和S共同作用,使!Q为0,!Q(为1)和R共同作用,使Q为0;若初始Q为1,!Q为0,则Q和S共同作用,使!Q为0,!Q(为0)和R共同作用,使Q为0(在这种输入下,Q和!Q都为0,与设计初衷相违背,这种输入不能出现)

由上面四种输入组合可以看出,当R=S=0时,Q状态维持不变,当R=S=1时,与预期不一致,另外两种情况,R(Reset)表示置0,S(Set)表示置1。

R-S锁存器的状态随输出的改变而改变,并且必须满足RS不能同时为1,因此这种电路不适用。(R-S锁存器也可以用与非门视线,但是问题依然没有解决)

D锁存器和触发器

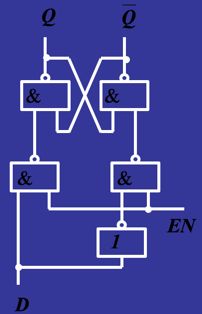

在R-S的基础上,如果能确保RS不同时为1,则这个约束可以规避,D锁存器正是在R-S锁存器的基础上进行改进。如果让R接一个原变量,S接对应的反变量,则可以消除这种约束。D锁存器的电路如下图4所示:

D锁存器随着输入改变而改变,这种输入随时改变的特性是所有锁存器的特点(CPU的计算是根据时钟脉冲同步的,时钟脉冲是稳定的,需要确保在一个时钟脉冲内Q状态必须是稳定的),利用时钟脉冲来保证Q状态稳定是触发器的基本特点。对于D触发器,其电路图如下图6所示:

下面对图6进行解释(这一部分是原理,最好能够理解。从考试和使用的角度,记住各触发器的功能特点就ok了,不理解也可以,很多高校的老师也不讲这一部分),图6中的CP(Clock Pulse)是时钟脉冲

当CP为0时,3和4两个与非门被锁住(即3和4输出均为1,Q和!Q均保持不变),6门的输出为!D,5门的输出为D(3门的输出为1);

当CP的上升沿来临时(由低向高变化的过程),3和4两个与非门被打开,此时,

* 若D为1,则(5门向)3门的输入为1,3门输出为0;3门输出为0确保5门被封住(D在这个脉冲内的变化不会影响5门),另外,3门输出为0也确保4门被封住,4门输出1,从而确保Q为1,!Q为0;

* 若D为0,则(5门向)3门的输入为0,3门输出1,(6门)向4门的输入为1,(3门)向4门的输入为1,因此,4门的输出为0(确保4门向6门的输入为0,从而封住6门,在这个脉冲内,D的变化不会影响Q的状态),确保Q为0, !Q为1

从上面的分析得知,在一个时钟脉冲内,无论D的如何变化,不会影响D触发器的稳定性,隐含的意思是:在CP上升沿到来的前一霎那的D值,确定了D触发器下一个时刻的状态,在上升沿过程中,D值变化不会影响D触发器状态。另外,D触发器由于外部输入最少(相对于R-S和J-K),广泛应用于电路中,PC中的内存条一般都是由D触发器构造。

J-K锁存器和触发器

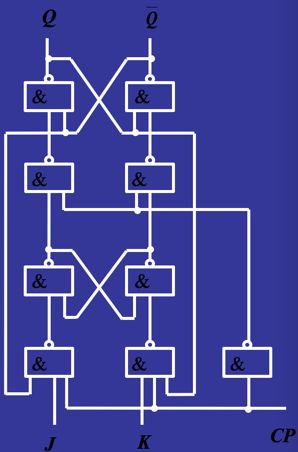

为了解决R-S锁存器中的RS约束问题,另一种方案是J-K锁存器,其电路图入下图7所示:

J-K锁存器的次态方程为(R-S锁存器和D锁存器请童鞋们自己推导或查阅其它资料,挺简单的):

Qt+1 = J*!Qt + !K*Qt

对J-K锁存器在不同的输入下进行分析:

- J = 0, K = 0, Q维持状态不变;

- J = 0, K = 1, 若初始Q=0,!Q=1, 则左上与非门输入均为1,置Q为0,Q(为0)通过右上与非门确保!Q为1;若初始Q=1,!Q=0,类似的方法进行分析;

- J = 1, K = 0, 置Q为1, !Q为0,分析方法同上;

- J = 1, K = 1. 若初始Q=0,!Q=1, Q为0封住右上的与非门(确保其输出为1)和右下的与非门(输出为1),则左下与非门的输入均为1,输出为0,从而左上的与非门输出为1,左上的与非门输出(为1)与右下的与非门(输出为1),共同作用导致右上的与非门输出为0,导致翻转;接着右上的与非门输出为1又导致左上的与非门输出为 0,左上的与非门又导致右上的与非门输出1…,一直在这里空翻。 若初始Q=1,!Q=0,同样的分析方法,结果为一直空翻。

根据上面的分析,J-K锁存器虽然解决了R-S锁存器的约束问题,但存在空翻现象。为了规避这个问题,工程师又创造了主从J-K触发器,如下图8所示:

由主从两组锁存器组成,下面一组是主锁存器,当CP为1时,输入信号J、K起作用。当CP由1变为0时,将锁存在主锁存器的状态输入从锁存器。这样,一个完整的数据存储,需要有一个完整脉冲的全过程,这个控制脉冲又称为触发脉冲,两个锁存器构成的电路称为触发器(Flip—Flop)。具体的分析方法和上面的类似(童鞋们可以自己分析一遍)

总结

在实际的电路中,一般使用触发器,通过时钟脉冲进行控制,用得最多的时D触发器和J-K触发器;触发器能保证一个脉冲内的信号稳定。当然,也存在其它类型的触发器(如T触发器和T’触发器等)。

触发器和组合电路中的译码器、编码器、选择器、分配器等组合在一起能构成所有我们需要的电路,这也是后续课程如计算机组成原理和嵌入式等课程的基础,牢记并理解组合电路和典型触发器的功能特性是进行后续课程学习保证。

如有错,请大家批评指正!谢谢!