消费者渴望更高的视频质量,推动了视频技术的发展。MPSoC 基于 Zynq-7000SoC ,包括一个可编程逻辑 (PL) 的桥接处理系统 (PS),但它在 Zynq UltraScale+ MPSoC进行了额外的扩展,因而非常适合多媒体应用领域。主要的区别包括:针对 UHD-4K 集成了支持 H.264 / H.265 的视频编解码器单元,适用但不仅仅适用于监控、视频会议、嵌入式视觉和一些广播应用等领域,实现低时延的编码,同时相对于服务器或可编程逻辑而言能效更高。该功耗优化型图形子系统基于 ARM Mali-400,这是一种业经验证的完善架构,非常适用于 2D 和 3D 图形。PL 可编程性可提供:(a) 任意到任意高速视频/ 音频接口的灵活性及可扩展性;(b)为多媒体管道带来定制图像及视频处理功能的差异化效果。

Zynq UltraScale+ MPSoC 多媒体解决方案

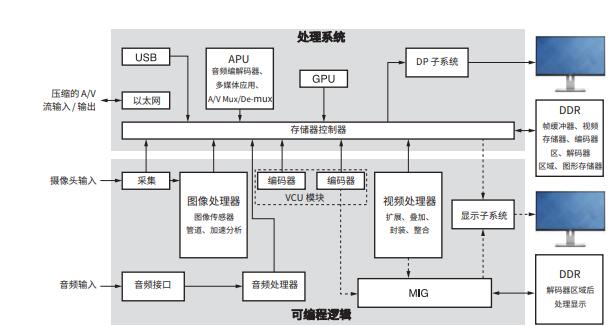

Zynq UltraScale+ MPSoC 是一款异构 SoC,包括许多处理引擎、一系列高速外设、高级 I/O 功能和 PL。处理引擎包括基于四核 ARM Cortex A53 的 APU、基于双核 ARM Cortex R5 的 RPU、Mali 图形处理单元、平台管理单元和视频编解码器单元 (VCU)。它可将图形与视频流水线化等关键应用交由专用处理块分担,也能通过高效的电源域与电源分区开关不同的块。通过多种互联选择、DSP 块和 PL 选择,Zynq UltraScale+ MPSoC 的整体灵活性能满足用户许多不同的应用需求。

Zynq UltraScale+ MPSoC框架图

该产品系列的可扩展性能完美满足设计师的要求,使用单个平台和业界标准的工具即可同时满足成本敏感型和高性能应用的需求。

为了实现高性能、先进的多媒体系统,必须采用适当的处理引擎,还要能添加定制逻辑以实现差异化。此外,也可支持当今多种多媒体设备所需的任意到任意的连接功能。此前,要满足上述要求,往往要采用多芯片解决方案。虽然多芯片解决方案可能提供所需的多媒体和连接功能,但也会导致高功耗。像Zynq UltraScale+ MPSoC 这种单芯片解决方案则能解决该问题。定制逻辑能在同一器件上满足硬件加速或任意到任意的连接需求,从而能显著节约功耗。除了处理引擎、硬件编解码器(自带功耗管理功能)和对定制逻辑的支持之外,Zynq UltraScale+ MPSoC 将这些组件放置在具有独立电轨的不同电源域中。这种配置可用于为整个系统设计优化功耗管理方案。Zynq UltraScale+ MPSoC 采用台积电 16nmFinFET 工艺节点,这就能大幅提高性能并降低功耗,也能支持下一代节能型多媒体系统的设计。

集成型视频编解码器单元 (VCU)

软件视频编解码器实现方案有很多种,但实际上 , 所有软件都要在硬件上运行。使用基于软件的编解码器解决方案,以合理的帧速率实现具有出色视频质量 (VQ) 的高压缩比,需要多个高功耗服务器类 CPU,此类 CPU 通常部署在云端。

由于必须远离设备,实时压缩通常无法实现。不过软件实施方案极为灵活,系统也能进行高度优化。但是,在软件中实现十分灵活,系统也极可能得到优化。另一种解决方案是在 PL 中实现软 IP 块。这种实现方案相对于离线软件模式或许性能较低,但能实现低时延压缩。相对于服务器级 CPU 而言,功耗得以改善,但并不像全集成解决方案那么出色。通常高级编解码器需要相对较大的可编程逻辑器件 ;但是,部署后的可编程性则为该解决方案提供了高度灵活性。

Zynq UltraScale+ MPSoCs 采用了另一种策略,即使用硬化的专用视频编解码器块。由于采用包含硬化 VCU 的单晶片,与其他策略相比,Zynq UltraScale+ MPSoC 可实现具有低时延路径、低功耗的实时压缩。由于采用了专用的编解码器引擎,应用处理单元 (APU) 和/或 PL 能用于其他计算。

VCU 可提供多标准编码解码功能,包括支持 AVC/H.264 和 HEVC/H.265 标准。它不仅同时具有编码(压缩)和解码(解压缩)功能,还支持 60Hz 下分辨率高达 4K UHD 的并行编码解码功能如果降低帧率,还能支持 4K 乃至更高的 DCI 等更高分辨率。VCU 可同时支持多达八个不同的视频流。同时处理不同视频流的总带宽要求不得超过 VCU 在 60fps 下对 4K UHD 的最大处理吞吐量。图 3 给出了不同的视频编码解码器实施策略。

视频编解码器实现策略图

VCU 是 PL 中的集成块,可支持 H.265 (HEVC) 和 H.264 (AVC) 标准,与处理系统 (PS) 非直连(硬连接)。使用赛灵思Vivado IP 集成器,设计人员可将 VCU 连接至应用处理单元 (APU) 以及 PS 和/或 PL中的存储器子系统。

与软件编码解码器不同,Zynq UltraScale+ MPSoC EV 器件中的 VCU 支持 H.264/H.265 视频数据的低功耗高性能压缩和解压缩。H.264/H.265 视频数据的低功耗、高性能压缩和解压缩。使其能够完美支持网络上的实时 UHD 视频流,可节约大量存储空间与网络带宽。VCU 同时支持 H.264 和 H.265 标准,有助于开发满足当前市场需求 (H.264) 和下一代高级需求 (H.265) 的解决方案。采用低时延方式同

时编码与解码的能力使其完美支持视频会议和 H.264、H.265 之间的转码要求。多视频流多编解码器的编码与解码能力可满足 DVR、视频服务器和多视频流 IP 摄像头的视频监控头端应用要求。由于支持高达 4:2:2 10 位 UHD-4K 的视频格式,VCU 也适合专业和高端消费级的制作与后期制作解决方案。AllProgrammable Zynq UltraScale+ MPSoCEV 器件结合集成 VCU 规范,为各种多媒体市场带来了理想的低成本、单芯片解决方案。

VCU 软件堆栈

可用 Zynq UltraScale+ MPSoC 结合常见的多媒体框架 GStreamer,来开发硬件加速型多媒体应用。GStreamer 采用的插件模型可分为三大功能 :源极、过滤和汇极插件。通过链接不同的插件 / 元素,可创建实现美的回放或捕获等具体任务的流水线。GStreamer 提供的 gst-omx 插件能在 Zynq UltraScale+ MPSoC 器件上执行硬件加速视频编码与解码。GStreamer 应用与 OpenMAX 集成层通过 gst-omx 插件互动。由 OMX IL 定义标准化的媒体组件接口,能与硬件中实现的 VCU 通讯。该层与控制软件(用户空间驱动程序)API 交互,而 API 则能调用内核空间驱动程序。

内核驱动程序与嵌入式微控制器单元 (MCU) 通讯,MCU 在 VCU 中集成编码器和解码器。MCU 上运行底层固件,控制编码器 / 解码器引擎。内核驱动程序向 MCU 发送帧级命令到,并等待 MCU 的响应。收到内核驱动程序的命令后,MCU 为编码器/ 解码器引擎调度任务,并向内核驱动程序返回状态。

根据用户的应用要求,灵活的 VCU 软件堆栈可在任何层面使用。开发人员能用控制软件 API、OMXIL 或 GStreamer 与 VCU 硬件交互,开发多媒体流水线。VCU Linux 软件堆栈的流程

根据待开发的多媒体应用的复杂程度,开发人员可可选用特定的 VCU 框架层。由于 GStreamer 具有跨平台滤镜、编解码器支持 ;可轻松创建视频编辑器、转码器、流媒体播放工具与媒体播放器,而采用即插即用的模式,系统只需读取单一格式的文件,处理之后再导出为其它格式,这使 GStreamer 成为一大广受欢迎的选择。它能灵活地集成插件组件,将组建混合匹配构成任意流水线,为编写成熟的多媒体应用提供了条件。此外,如需开发具有简单轻便设计的定制化多媒体应用/框架,应用也可采用控制软件API。

集成型图形处理单元 (GPU)

Zynq UltraScale+ MPSoC 处理系统 (PS) 中的 GPU 为 ARM Mali-400 MP2,与 APU 直接绑定,还可在帧缓存中加速视频图形渲染,从而实现显示器输出。GPU 可通过独立的并行引擎进行像素渲染,速度远高于依靠 CPU 来处理图形的友商 ASSP,而且与需要设计人员添加片外 GPU 引擎的解决方案相比,成本与功耗均更低。

Mali-400 MP2 架构设计

GPU 通过全面可编程的架构加速 2D 和 3D 图形,该架构既支持基于着色器的图形 API ,也支持固定功能图形 API 。GPU 具有抗锯齿功能,能实现最佳图像质量,且几乎不会造成额外的性能损耗。配套提供经实践检验的全套 Linux 驱动程序,能自动将图形命令从 APU 转到 CPU 处理。

Zynq UltraScale+ MPSoCGPU 的突出特性包括:

• ARM Mali-400MP2

• 最高速度等级下性能可达 667MHz

• 具有一个几何处理器,两个像素处理器

• 专用的 64KB 共享 L2 缓存

• 专用的存储器管理单元

• OpenGL ES 2.0 和 OpenGL ES 1.1 支持

• OpenVG 1.1 API 支持

• 三个引擎上均采用独立电源门控

• 像素填充率达每秒 13.34 亿 (Mpixels/sec)

• 每秒 7260 万三角形 (Mtriangles/sec)

• 浮点着色 12Gflops

上述性能数据基于 667MHz 的最高 GPU 时钟速率。

GPU 软件堆栈

Zynq Ultra Scale+ MPSoC 图形软件堆栈分为三层:内核空间、用户空间和应用空间。

内核空间

内核空间与 GPU 硬件交互,提供必要的信息,以便向集成式硬件着色器分发任务。此外还负责处理底层中断,进行存储器管理。

VCU 软件架构

用户空间驱动程序包含以下组件:

• Mali 通用用户库:该层负责 GPU 工作创建以及图形渲染流水线的任务调度。

• 扩展图形库 (EGL) :该层用于同下层窗口层交互,进而与显示驱动程序交互。负责处理包括窗口创建在内的资源管理,也处理图形环境管理、表面/ 缓存绑定、渲染同步等操作。

• OpenGL ES :该层提供标准化的抽象 API,供应用使用。

应用空间

GPU 可用的软件包包含 OpenGL ES 1.1 和 OpenGL ES 2.0、底层图形库以及 ARM 提供的工具(Streamliner 和 Graphics Debugger)。Open GL ES 支持各种操作系统,为应用提供了高度轻便的特性。其他软件组件将按需提供。

显示控制器

Zynq UltraScale+ MPSoC 提供高速互联外设,后者包含集成式 DisplayPort 接口模块。DisplayPort接口位于 PS 端,可多路复用至四个专用高速串行收发器中的两个,工作速率高达 6 Gb/s。该架构摆脱了对于额外显示芯片的需求,进一步降低了系统 BOM 成本。

DisplayPort 接口基于 VESA DisplayPort Standard Version 1 和 Revision 2a 开发,其提供的多个接口能处理来自 PS 或 PL 的实时音视频流,也能存储来自存储器帧缓存的音视频。它同时支持两个音视频流水线,支持 alpha 混合、chroma 复采样、色彩空间转换和音频混合等功能的动态渲染。DisplayPort 既可使用一个 PS PLL,也能使用 PL 的时钟生成像素时钟。

集成型可编程逻辑 (PL)

除视频编解码器和图形处理之外,多媒体应用还需要其他重要组件,如视频数据的输入输出管理 , 以及处理高速视频数据的功能。ARM Cortex-A53 核心、存储器单元和Zynq UltraScale+ MPSoC 的诸多外设相结合,为管理和捕获多个不同来源的数据发挥了关键作用,而后再向 VCU 提供数据。USB 和以太网等 PS 外设可用于摄像机、网络相机与网络摄像头等视频流设备。在 PL 内可设计定制化逻辑,用于捕获来自直播源的视频。例如,SDI RX、HDMI RX、MIPI CSI IP 等协议均可用于捕获不同来源的原始视频。 VCU 随后可将原始视频编码为AVC 或 HEVC 压缩比特流格式。同样,经解码的原始视频也能发送至外部显示单元,随后可采用 PS 中的 DisplayPort 控制器(DP 控制器)显示,或通过 HDMITX、SDI TX MIPI DSI 等其他协议创建相关 IP。

赛灵思提供一系列显示接口 IP,参见赛灵思 Vivado IP 目录,便于取得许可证的用户在 PL 中实现

显示接口 :

• HDMI 1.4/2.0 发射器子系统和 HDMI 1.4/2.0 接收器子系统

• MIPI CSI-2 接收器子系统

• MIPI DSI 发射器子系统

• UHD-SDI 发射器子系统和 UHD-SDI 接收器子系统

视觉算法可用于采集来自原始数据的重要信息,如路标识别和针对驾驶员辅助技术的动作检测、视频监控面部识别、高级拍摄应用的物体与动作识别等。除收集数据外,算法还可用于音视频广播和视频会议等用例中处理与操控原始数据。考虑到今后几年视频分辨率不可避免的攀升态势,有关算法需要具备极高的工作速度。PL 为此类算法提供了所需的硬件加速功能,便于大幅提高性能,满足下一代技术需求。

采用 Vivado 和 SDK 工具支持任意连接功能

对于硬件差异化,许多平台开发人员使用可编程逻辑实现任意互联。Vivado Design Suite 通过提供以下设计套件帮助系统设计者开发易用性系统:

• IP 集成器 (IPI) 工具

○ 使用原理方框图方法整合 IP,创建总体系统

• PS 配置向导 (PCW)

○ 用户能配置、启用或禁用 PS 外设,并实现时钟和存储器配置等。

• IP 目录

○ 使用 IPI 可将 IP 实例化并集成到更大系统中。此外,用户能将自己的定制 IP 库集成到 IP 目录中。

Vivado Design Suite 还可提供 IP 仿真、综合、布局和布线、目标器件配置以及导出至硬件等特性,能向软件开发工具提供硬件配置信息。

赛灵思软件开发套件 (SDK) 用其生成启动加载器,并在执行阶段向软件传递专门用于某个特定硬件的信息。

SDK 用于 C/C++ 嵌入式软件开发和调试,其基于 Eclipse 开源框架,并可提供系统性能监测功能,以便于用户在运行时对系统性能进行监测。

就使用 Linux 操作系统的用户而言,赛灵思可提供 PetaLinux ( 嵌入式 Linux SDK)。它可提供多面的 Linux 操作系统工具流程,能带来全面的配置、构建及部署环境。

硬件资源有限乃至根本没有硬件资源的团队因开发 RTL(VHDL 或 Verilog)所需的专业技术不足,一直面临严峻挑战,而 Zynq UltraScale+ MPSoC 则为他们提供了完美的解决方案,帮助实现可编程器件的全面优势。近期,赛灵思发布了 SDSoC ™工具,提供了熟悉的嵌入式 C/C++/OpenCL 应用开发体验,包括简单易用的 Eclipse IDE 和用于异构 Zynq UltraScale+ MPSoC 部署的全面设计环境。为缩短编程时间,SDSoC 工具还提供了系统层剖析、自动化软件加速、自动化系统连接生成等功能和库。它还支持终端用户开发人员快速定义、集成和验证系统级解决方案,并为终端客户提供定制的编程环境。用于视频数据分析和处理的复杂算法用高级软件编写,可用 SDSoC 工具在 PL 中实现加速。它能缩短开发周期,同时提升性能。

应用示例

Zynq UltraScale+MPSoC 的可扩展电源、高性能和专用引擎使其成为许多应用的理想选择。

视频会议应用

Zynq UltraScale+ MPSoC 支持高端视频会议端点。视频会议端点是用来进行点对点视频通话的终端。一个完整的双向视频会议系统由一个视频摄像头和一个基本单元组成,该基本单元与每个位置的视频显器连接。两个基础单元间的通信在 IP 网络上进行。视频基础单元由带有集成型片上视频端口的 示 DSP组成,用于处理音频和视频编码/ 解码。

逻辑资源和收发器可用来连接 UHD-4K 视频摄像头以采集原始视频,并将其馈送至已连接的存储器中。DSP 块资源用来对采集到的数据进行图像处理,而处理后的数据转发给集成 VCU 进行压缩。使用运行于 APU 子系统之上的应用软件将压缩后的数据进行分组,并通过以太网将其以流媒体的形式传输到远程端点。

终端端点也能从远程端点接收压缩数据,用 VCU 将其解码,并存储在已连接的存储器上。在 PL 中运行的软视频处理块 IP 能缩小从摄像头采集到的原始数据,并将其与解码数据混合,随后将其提供给显示控制器,在 PS 或 PL 的软 IP 中实现。

GPU 可用来创建屏幕显示 OSD,其输出可与来自视频处理单元 (VPU) 的视频输出混合,将其发送到显示控制器,并在监测器上显示。参见下图.

视频会议应用图

利用 Zynq UltraScale+ MPSoC

数据中心与云计算领域的视频转码

视频转码是指将媒体资产从一种格式转为另一种格式的过程,从而可在不同平台和设备上查看视频。大多数情况下,进行视频转码是由于以下一种或多种情况:

• 目标设备不支持原始数据的格式。

• 目标设备容量有限,需减小原始文件的大小。

• 必须将不兼容或过时的文件格式转为现代格式,从而使新设备更好地支持。

视频转码流程通常分为两步。第一步是解码,可将原始数据转为非压缩格式。第二步是对数据重新编码,即可将数据以所需的格式传送到新设备上。

随着互联网上 Netflix 和 YouTube 等流行网站的流媒体不断增长,而且 UHD 4K 摄像头在市场上地位日益突显,需要大量存储和带宽。

服务多样化不断发展,高清视频的日益普及,以及超高清格式(如 UHD)的出现,对编码效率的强烈需求远超诸如 H.264/AVC 等现有编解码器的能力。当更高的分辨率伴随着立体声或多视点捕获和显示时,需求就更为强烈。H.265/HEVC 编解码器的设计旨在支持 UHD4K 和 UHD8K,并且有关工具能充分发挥并行架构的优势。与同等质量水平的H.264 编码内容相比,HEVC 标准能够削减约 50% 的带宽占用。

大部分数据中心采用不同的压缩格式存储视频,但传输视频流的方式则需参照接收器所支持的格式。

为支持有关拓扑,数据中心需要根据目标支持的格式将一种视频格式转码为其他格式。在这种拓扑中,Zynq UltraScale+ MPSoC 器件非常适合高性能转码,因为它支持当前部署的技术 (H.264/AVC) 和未来新一代编解码器标准 (HEVC)。它还具有在可编程逻辑中编程不同的硬件编解码器的灵活性,从而支持各种编解码器标准。如果在数据中心或云计算系统中部署为加速器,Zynq UltraScale + MPSoC 上的 VCU 就能加速转码过程。例如,移动用户录制 H.264 格式的直播视频,并将视频上传到云服务器以便将来播放。如用户希望在仅支持 HEVC 格式的工作站上播放云端存储的视频,那么工作站可请求服务器进行内容转码,并以 HEVC 格式发送视频。在接收到工作站的请求后,服务器利用集成型 VCU 作为编解码器加速器执行从 H.264 到 HEVC 的转码,并将视频流传输至工作站。

视频转码图

实时转码的另一个应用是监控摄像头,摄像头支持 H.264 压缩,但播放设备支持 HEVC 编解码器。在此情况下,Zynq UltraScale+ MPSoC VCU 能完美匹配相关要求,因为它能从监控网络 IP 摄像头接收 H.264 压缩数据,然后用 VCU 模块将其转码为 H.265,再将其传输到目标播放设备显示播放内容。

汽车全景查看系统

汽车全景查看已改变了驾驶体验,而 GPU 是推进该技术发展的主要力量。全景摄像系统是一种新兴的汽车高级驾驶辅助系统 (ADAS) 技术,允许司机看到车辆周围 360 度全景视图,从而帮助司机安全泊车。

基于全景视觉图像解决方案的实时渲染利用虚拟摄像机在 GPU 上重建全视觉测距,其中虚拟摄像机参数从实体摄像机克隆并在 GPU 上实现,生成随实时参数变化的虚拟场景图像。Zynq UltraScale+ MPSoC非常适合这一领域,因为 GPU 具有极高效的固定功能单元GPU 马力用来完成综合,以阐释复合视图,生成输出像素。生成的像素可能是两个像素的组合(如输出处于重叠区)或单个像素(如输出处于非重叠区),用几何查找表 (LUT) 从输入帧提取该像素。几何 LUT 中的每个条目指定摄像机 ID 和输入帧的坐标,从而生成当前位置的输出像素。网表流程随后生成输出帧。给定一个特定的输出分辨率,每个输出位置都可以通过投影和透镜转换到输入图像中的一个位置来映射到输入图像。网表包括车辆周边环境位置的 3D 世界坐标和用于从给定位置的相邻摄像机观察场景。

进行纹理映射的相关输入位置。将输出表示为碗形,其高度根据距车辆中心的距离而变化。将包括输出网格和相关纹理映射的网表集合传递给图形处理器做进一步的渲染。应用结合网表也能生成混合LUT,除了网格表,应用程序还可以生成一个混合 LUT,它可以对每个位置接收到的图像强度信息的线性组合进行编码。采用 GL_OES_EGL_image_external 延伸,将摄像机 YUV 图像作为纹理传输给 GPU 进行渲染。

全景视图

全景视觉系统从四个鱼眼摄像头接收输入视频流,并创建合成全景视图。该系统利用几何 LUT 编码的映射来创建拼接的输出图像。

Zynq UltraScale+ MPSoC优势

Zynq UltraScale+ MPSoC 的灵活性能加速计算密集型应用程序,在 GPU、CPU 和 PL 之间共享工作负载,在 PL 中可卸载复杂的算数计算以实现硬件加速,并且在 APU 上可预先计算 OpenGL 着色语言 (GLSL) 一致变量。GPU 着色器核心上的计算仅适用于顶点和片断之间不同的值。整批顶点中所有保持常量的值在 CPU 上处理最为有效。

Zynq UltraScale+ MPSoC 优势

在某些任务中,即使对于非常大的数据集,CPU 可轻松地胜过 GPU。此外,平台上有可编程逻辑能为 OpenGL 矩阵提供硬件加速,并为复杂 3D 模型提供闪电计算。图形系统通过流水线操作序列生成图像,通常将其中最慢的阶段称为流水线瓶颈。三角形等单个图形原语具有单一图形流水线瓶颈。但是,当渲染包含多个原语的图形帧时,瓶颈可能会发生变化。例如,如果应用程序先渲染一组线条,再渲染一组亮的且有阴影的三角形,那么瓶颈将可能发生变化。由于某些流水线阶段在 CPU 上执行,其他阶段在 GPU 上执行,瓶颈会不断变化。Zynq UltraScale+ MPSoC 封装了多个处理引擎和 PL,通过提供灵活性在 GPU、PL 和 CPU 之间执行计算的工作分配,消除性能瓶颈并提高整体吞吐量从而帮助 GPU 加速 2D 和 3D 图形的处理。

结论

Zynq UltraScale+ MPSoC 堪称名副其实的异构多处理器SoC 平台。所谓“名副其实”,是指其远远超越高性能 64 位处理器耦合可编程逻辑的范畴。它采用专用引擎进行实时处理、图形处理以及视频编码与解码。这样用户就可以选择在何处实现算法,从而优化系统性能和功耗。Zynq UltraScale+ MPSoC在软硬件层面都能实现完全的灵活性,同时集成了嵌入式市场上有史以来最多样化的专用引擎。