ZYNQ 资源介绍

目录

1、简述

2、PS 资源

2.1、应用处理器单元 APU (Application Processing Unit)

2.2、存储器接口

2.2.1、DDR控制器

2.2.2、Q-SPI 控制器

2.2.3、静态存储器控制器(Static Memory Controller, SMC)

2.3、I/O 外设

2.3.1、GPIO

2.3.2、ETH X 2

2.3.3、USB X 2

2.3.4、SD/SDIO X 2

2.3.5、SPI X 2

2.3.6、CAN X 2

2.3.7、UART X 2

2.3.8、IIC X 2

2.3.9、PS MIO Pin X 54

3、PL 资源

3.1、CLB

3.2、BRAM

3.3、DSP48E1

3.4、CMT

3.5、SelectIO

3.6、GTX

3.7、XADC

3.8、PCI-E

4、内部互联

4.1、PS 内模块的互联

4.1.1、OCM 互联

4.1.2、中央互联 (InterConnect)

4.2、PS-PL互联

4.2.1、功能接口

4.2.2、配置信号

在上一篇文章中(ZYNQ 简介)对 ZYNQ 进行了简单的叙述,在做相关的内容之前,有必要对其具体内容进行详细的了解; 首先是对这款芯片所包含的内容进行简单的了解(参考 UG585 手册)

1、简述

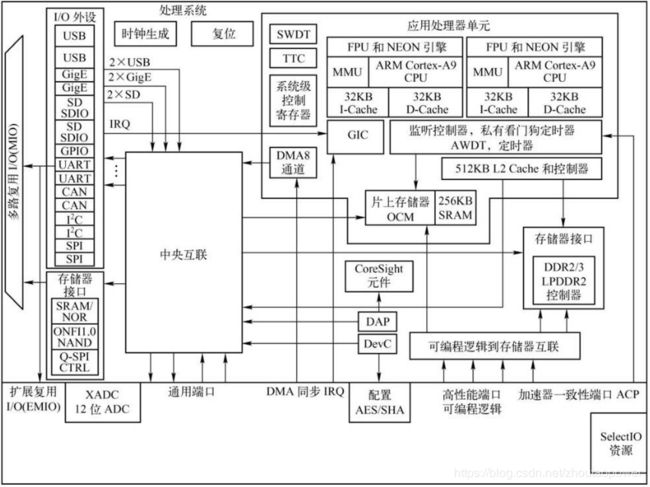

ZYNQ 的内部结构图如下图所示,可以看到是由两部分构成:

1、PS 部分:全称为 Processing System,集成了双核 ARM Cortex-A9 处理器以及外设单元;

2、PL 部分:全称为 Program-mable Logic,该结构基于 XILINX A7 系列的 FPGA 构成;

2、PS 资源

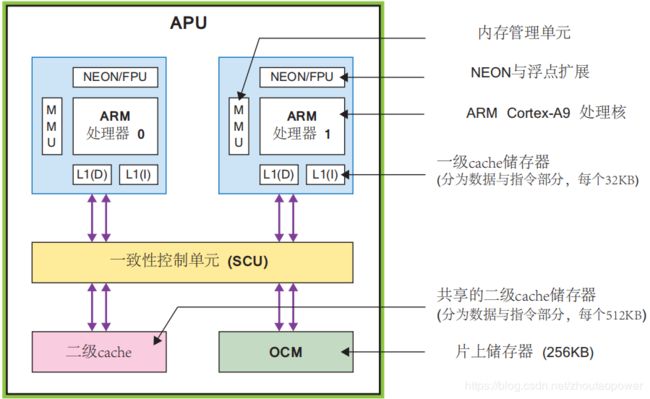

2.1、应用处理器单元 APU (Application Processing Unit)

(1)双核ARM Cortex-A9多核处理器CPU(ARM V7)。

(2)实时运行选项。允许单个处理器,以及对称或非对称的多处理(Symmetrical Multi-processing, SMP)配置。

(3)ARM V7 ISA。提供标准的ARM指令和Thumb-2指令,以及 Jazelle RTC 和 Jazelle DBX JAVA 加速。

(4)每个Cortex-A9处理器核都有独立的NEON,可以实现128位SIMD协处理器和VFPv3。

(5)每个Cortex-A9处理器核包含带有校验的32KB L1指令高速缓存和32KB L1数据高速缓存。

(6)双核Cortex-A9共享带有校验的512KB L2高速缓存。

(7)每个Cortex-A9有私有定时器和看门狗定时器。

(8)系统级的控制寄存器(System-Level Control Registers,SLCRs),一组不同的控制器用来控制PS的行为。

(9)侦测控制单元(Snoop Control Unit, SCU)包含了L1和L2的一致性要求。(10)从PL(主设备)到PS(从设备)的加速器一致性端口(Accelerator Coherency Port, ACP)。

(11)提供带有校验功能的256KB片上存储器OCM。它提供了两个访问端口。Zynq-7000内的Cortex-A9处理器、可编程逻辑及中央互联均可访问OCM。与PS内的L2处于同一层次,但没有提供缓存能力。

(12)PS内提供的64位高级可扩展接口(Advanced ExtendedInterface, AXI)从端口,提供了访问L2高速缓存和片上存储器OCM的能力,以及保证在数据交易时与L1和L2高速缓存的数据一致性。

(13)DMA控制器。其中的四个通道用于PS,实现存储器与系统内的任何存储器的数据交换;另外四个通道用于PL,实现存储器到PL及PL到存储器之间的数据交换。

(14)通用的中断控制器(General Interrupt Controller, GIC)。它们有各自独立的中断屏蔽和中断优先级。其中包含5个CPU私有外设中断(Private Periphercal Interrupt, PPI)、16个CPU软件中断(SoftwareGenerated Interrupt, SGI),以及分配来自系统、PS和PL剩余部分的共享外设中断(Shared Peripheral Interrupt, SPI)(其中20个来自PL)。

支持来自CPU发送到PL的等待中断(Wait for Interrupt,WFI)和等待事件(Wait for Event, WFE)信号,以及扩展的安全特性支持TrustZone技术。

2.2、存储器接口

存储器接口提供对不同存储器类型的支持。

2.2.1、DDR控制器

(1)支持DDR3、DDR2、LPDDR-2类型的存储器,由器件的速度和温度等级决定工作速度。

(2)该控制器提供了16/32位数据宽度。

(3)支持16位ECC。

(4)使用最多73个专用的PS引脚。

(5)模块(不是DIMM)。对于32位宽度来说,可选配置包括4 ×8位、2 × 16位、1 × 32位;对于16位宽度来说,可选配置包括2 × 8位、1× 16位。

(6)根据可配置的空闲周期,自动进入DDR低功耗状态及自动退出DDR低功耗状态。

(7)数据读选通自动标定。

(8)写数据字节使能支持每拍数据。

(9)使用高优先级读(High Pripority Read, HPR)队列的低延迟读机制。

(10)支持发给每个端口的特殊紧急信号。

(11)在64MB边界上可编程TrustZone区域

(12)对于两个不同ID来说,每个端口提供了互斥的访问能力,但不支持锁定交易功能。

2.2.2、Q-SPI 控制器

(1)提供了连接1个或两个SPI设备的能力。

(2)支持一位和两位数据宽度的读操作。

(3)用于I/O模块100MHz的32位APB3.0接口,允许包括编程、读和配置的全设备操作。

(4)100MHz 32位AXI线性地址映射接口用于读操作。

(5)支持单个芯片选择线。

(6)支持写保护信号。

(7)提供可用的4位双向I/O信号线。

(8)支持读速度为×1、×2和×4,写速度为×1和×4。

(9)主模式下最高的SPI时钟频率可以达到100MHz。

(10)252字节入口FIFO深度,用于提高四-SPI读效率。

(11)支持四-SPI器件的存储容量最高为128Mb。

(12)支持双四-SPI器件,并列的两个四SPI器件。

2.2.3、静态存储器控制器(Static Memory Controller, SMC)

SMC提供了NAND存储器和并行SRAM/NOR存储器的读/写控制功能。

(1)对于NAND存储控制器来说,提供了下面的功能:支持8/16位的I/O数据宽度;提供一个片选信号;支持ONFI规范1.0;提供16字读和16字写数据FIFO的能力;提供8字命令FIFO;用户可通过配置界面修改I/O周期的时序;提供ECC辅助功能;支持异步存储器工作模式。

(2)对于并行SRAM/NOR控制器来说,提供了下面的功能:支持8位数据宽度,以及最多25位地址信号;提供两个片选信号;提供16个字读和16个字写数据FIFO;提供8个字命令FIFO;对于每个存储器,提供用户可配置的可编程I/O周期时序;支持异步存储器操作模式。

2.3、I/O外设

Zynq-7000的PS系统提供了用于满足不同要求的I/O接口

2.3.1、GPIO

(1)PS提供了 54 个可用的 GPIO 信号。通过复用 I/O 模块MIO,将这些信号连接到Zynq-7000器件的外部引脚,并且可以通过软件程序控制这些信号的三态使能功能。

(2)通过扩展的复用I/O模块 EMIO,可以将PS内的GPIO信号引入到Zynq-7000内的PL单元,支持最多192个GPIO信号,其中64个为输入,另外128个为输出。

(3)可以基于单个或者组,对每个GPIO的功能进行动态地编程,即实现使能、按位或者分组写数据,输出使能和方向控制。

(4)根据每个GPIO所配置的中断能力,支持读取中断的状态;支持在上升沿、下降沿、任意边沿、高电平或低电平产生中断信号。

2.3.2、ETH X 2

两个三模式以太网控制器

(1)在RGMI II模式时,使用MIO引脚和外部的PHY。

(2)额外的接口使用PL内带有额外软核的PL SelectIO和外部的PHY。

(3)在SGMII模式时,使用Zynq-7000 PL内的GTX收发器模块。

(4)该控制器提供可以实现分散—聚集功能的DMA控制器。

(5)支持IEEE802.3和IEEE1588 V2.0协议。

(6)支持唤醒功能。

2.3.3、USB X 2

(1)使用相同硬件的USB2.0高速OTG(On-The-Go)双重角色USB主机控制器或者USB设备控制器操作。

(2)只提供MIO引脚。

(3)内建DMA控制器。

(4)支持USB2.0高速设备。

(5)可作为USB2.0高速主机控制器。它所提供的寄存器和数据结构遵循扩展主机控制器接口(Enhanced Host Controller Interface, EHCI)规范。

(6)支持USB收发器低引脚数接口(USB Low Pin Interface,ULPI)。ULPI支持8位。

(7)要求使用外部的PHY。

(8)支持最多12个端点。

2.3.4、SD/SDIO X 2

(1)它可以作为Zynq-7000基本的启动设备。

(2)内建DMA控制器。

(3)该控制器只支持主模式。

(4)支持SD规范2.0。

(5)支持全速和低速设备。

(6)支持1位和4位数据接口。

(7)支持低速时钟范围 0 ~400KHz。

(8)支持高速接口。全速时钟频率范围 0~50MHz,最大吞吐量 为25MB/s。

(9)支持存储器、I/O和组合卡。

(10)支持电源控制模式。

(11)支持中断。

(12)1KB数据FIFO接口

2.3.5、SPI X 2

(1)提供四个信号线,包括 MOSI、MISO、SCLK、CS。

(2)支持全双工模式,该模式支持同时接收和发送数据能力。

(3)在主机模式下,支持下面功能:手工或自动开始数据传输;手工或自动从设备选择CS模式;支持最多3个从设备选择线;允许使用外部3-8译码选择设备;软件可控制的发送延迟。

(4)在从模式下,软件可配置开始检测模式。

(5)在多主环境下,如果没有使能,则驱动为三态。如果检测到多个主设备,则识别出一个错误条件。

(6)通过MIO模块,该控制器支持最高50MHz的外部SPI时钟。当通过EMIO到PL的SelectIO引脚时,支持最高25MHz时钟频率。

(7)可选择所使用的主时钟。

(8)支持可编程的主波特率分频器。

(9)支持独立的128字节读FIFO和128字节的写FIFO,每个FIFO为8个字节宽度。

(10)软件程序可控制的FIFO门槛。

(11)支持可编程的时钟相位和极性。

(12)作为驱动中断的设备,软件能轮询状态或功能。

(13)可编程产生中断。

2.3.6、CAN X 2

(1)遵守ISO11898-1、CAN2.0A和CAN2.0B标准。

(2)支持标准(11位标识符)和扩展(29位标识符)帧。

(3)支持最高速度为1Mb/s。

(4)带有64个消息深度的发送消息FIFO。

(5)发送优先级贯穿一个高优先级发送缓冲区。

(6)Tx FIFO和Rx FIFO支持水印中断。

(7)在普通模式下,当错误或丢失仲裁时,自动重新发送。

(8)可保存64个消息的接收消息 FIFO。

(9)提供最多4个接收滤波器,用于对接收消息进行过滤。

(10)支持带有自动唤醒的休眠模式。

(11)支持侦听模式。

(12)提供闭环模式,用于诊断应用。

(13)可屏蔽的错误和状态中断。

(14)用于接收消息的16位时间戳。

(15)可读的错误计数器。

2.3.7、UART X 2

(1)可编程的波特率发生器。

(2)提供最多64字节的接收和发送FIFO。

(3)可选择的6、7或8个数据位。

(4)可选择的1、1.5或2个停止位。

(5)可选择的奇、偶,空格、标记或没有奇偶。

(6)可选择的奇、偶、帧和溢出错误检测。

(7)支持换行符生成和检测。

(8)支持自动呼应、本地环路和远程环路通道模式。

(9)支持产生中断。

(10)支持通过MIO和EMIO模块提供Rx和Tx信号。

(11)通过EMIO接口模块,可以提供CTS、RTS、DSR、DTR、RI和DCD等调制解调器控制信号。

2.3.8、IIC X 2

(1)支持16字节FIFO。

(2)支持IIC总线规范 V2。

(3)可程序控制的普通/快速总线数据率。

(4)支持主设备模式。在该模式下,支持写传输、读传输、地址扩展,以及用于慢速处理器服务的HOLD。

(5)支持从设备监控器模式。

(6)支持从设备模式。在该模式下,支持从设备发送器和从设备接收器、支持地址扩展、支持软件可编程的从设备响应地址。

(7)支持HOLD,防止溢出条件。

(8)支持TO中断标志,避免停止条件。

(9)作为中断驱动设备时,软件能轮询状态或功能。

(10)可通过软件控制产生中断。

2.3.9、PS MIO Pin X 54

(1)这54个引脚分成两组。第0组包括16个引脚,引脚范围0 ~15;第1组包括38个引脚,引脚范围16 ~53。

(2)通过配置,可以选择支持LVTTL 3.3V、LVCMOS 3.3V、LVCMOS 2.5V、LVCMOS 1.8V或HSTL 1.8V标准。

3、PL 资源

PL提供了用户可配置能力的丰富结构:

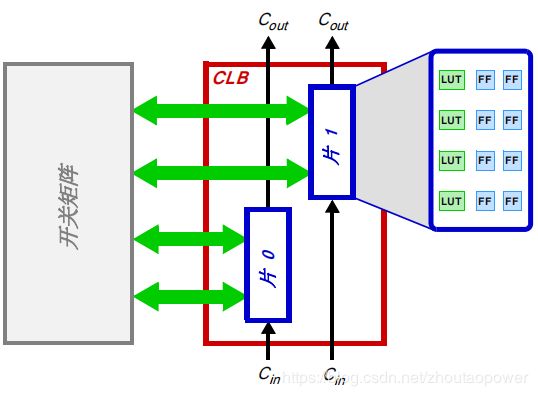

3.1、CLB

在可配置逻辑块(Configurable Logic Block CLB)内提供了下面的资源。

① 6 输入查找表(Look-UP Table, LUT)。

② LUT内的存储器能力。

③ 寄存器和移位寄存器功能。

④ 支持级联的加法器。

3.2、BRAM

36Kb容量的BRAM资源。它的特性主要如下:

① 提供了双端口访问能力。

② 支持最多72位数据宽度。

③ 可配置为双端口18Kb的存储器。

④ 可编程的FIFO逻辑。

⑤ 内建错误校准电路。

3.3、DSP48E1

数字信号处理DSP48E1资源

① 提供25 × 18宽度的二进制补码乘法器/累加器,可以实现高达48位的高分辨率信号处理器功能。

② 提供25位的预加法器,用于降低功耗及优化对称滤波器应用。

③ 提供高级特性,用于可选的可级联流水线,以及可选的ALU和专用总线。

3.4、CMT

CMT 时钟管理单元,提供了下面的功能:

① 用于低抖动时钟分布的高速缓冲区和布线。

② 频率合成及相位移动。

③ 低抖动时钟生成和抖动过滤。

3.5、SelectIO

可配置的 I/O 资源。提供了下面的功能:

① 支持高性能的SelectIO技术。

② 封装内提供高频去耦合电路,用于扩展的信号完整性。

③ 数字控制的阻抗DCI能三态,用于最低的功耗和高速I/O操作。其中,高范围(High Range, HR)IO支持电压范围为1.2 ~3.3V,高性能(High Performance, HP)IO支持电压范围为1.2 ~1.8V(仅对Z-7030和Z-7045器件有效)。

3.6、GTX

低功耗的吉比特收发器(仅Z-7030和Z-7045器件存在):

① 高性能收发器,其速率最高达到12.5Gb/s(GTX)。

② 低功耗模式用于芯片和芯片的连接。

③ 提供高级发送预加重和后加重能力,接收器线性(CTLE)和判决反馈均衡(Deci-sion Feedback Equalization, DFE),包含自适应均衡用于额外的裕量。

3.7、XADC

模拟—数字转换器(XADC):

① 两个12位模拟到数字转换器ADC,采样速率高达1Msps。

② 提供最多17个用户可配置的模拟输入端口。

③ 用户可以选择片上或外部参考源。

④ 提供用于检测温度的片上温度传感器,最大误差为±4℃。

⑤ 提供用于检测芯片各个供电电压的电源供电传感器,最大误差为± 1%。

⑥ JTAG连续的访问ADC测量结果。

3.8、PCI-E

用于PCI-E设计的集成接口模块(仅Z-7030和Z-7045器件可用):

① 兼容PCI-E基本规范2.1,提供端点和根端口能力。

② 支持Gen1(2.5Gb/s)和Gen2(5.0 Gb/s)速度。

③ 提供高级配置选项、高级错误报告(Advanced Error Report,AER)、端到端的CRC (End-to-End CRC, ECRC)高级错误报告及ECRC特性。

4、内部互联

4.1、PS 内模块的互联

在PS内用于连接各个功能模块主要包含OCM互联单元和中央互联单元。

4.1.1、OCM 互联

(1)提供来自中央互联和PL的访问,它用于对256KB OCM的访问。

(2)CPU和ACP接口。通过SCU访问OCM时,有最低的延迟。

4.1.2、中央互联 (Inter Connect)

(1)中央互联为64位宽度,通过它可以将IO端口和DMA控制器连接到DDR存储器控制器和OCM。此外,可以连接到用于互联PL逻辑的AXI_GP接口。

(2)用于连接以太网、USB和SD/SDIO控制器内的本地DMA单元。

(3)用于将PS内的主设备与IO端口连接在一起。

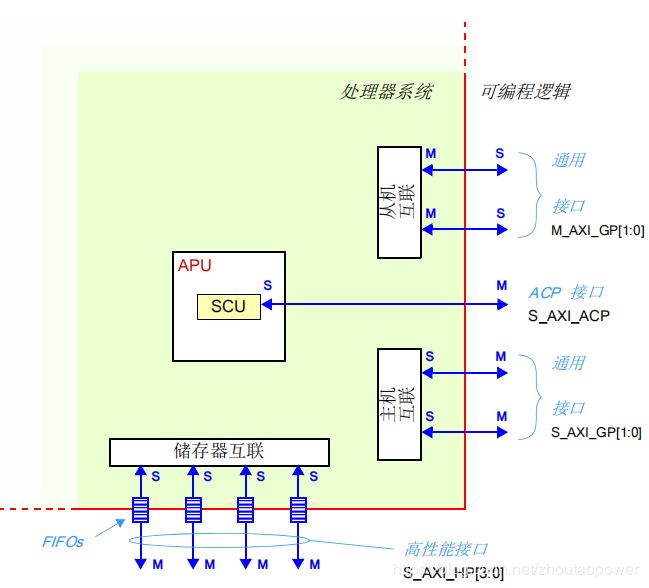

4.2、PS-PL互联

PS到PL的接口提供了可用于PL内定制外设的所有可用信号,通过PS-PL接口可以实现PL内定制的外设(也称为IP核)与PS内的Cortex-A9双核处理器及相关资源的连接。

在PS和PL之间提供了两种类型的接口。

4.2.1、功能接口

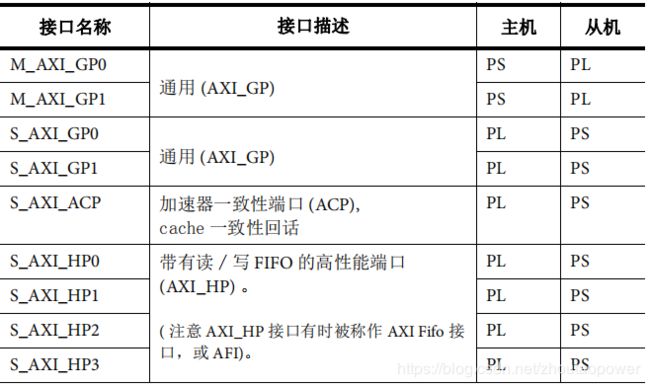

包含AXI互联,用于大多数I/O外设、中断、DMA流控制、时钟和调试接口的扩展MIO接口(EMIO)。这些信号可用于连接PL内用户设计的IP模块。PL AXI接口基于AXI3的接口规范。典型的包括AXI-GP、AXI-HP和AXI-ACP接口。每个接口由多个AXI通道构成。PL AXI接口如表所示。下面对这些接口进行详细说明。

(1)AXI_ACP 接口,它是PL内的一个64位高速缓存一致性主端口。

(2)ACI_HP,它是PL内的4个高性能/带宽主设备端口。其主要特性如下:

① 支持32位/64位数据宽度的主设备接口。

②在32位从接口配置模式下,高效地调整数据宽度及高效地扩展到64位数据宽度,用于非对齐的32位数据传输。

③ 通过AxCACHE[1],动态地实现在32位和64位接口之间宽度的转换。

④ 分开地R/W可编程发布能力,用于读和写命令。

⑤ 在PS和PL之间,提供异步时钟穿越所有AXI接口的能力。

⑥对于读和写操作,提供1KB(128 × 64位)容量的数据FIFO,用于消除长延迟传输。

⑦ 可选择使用来自PL端口的QoS信号。

⑧ 对命令FIFO和数据FIFO的填充计数值可用于PL内定制的外设。

⑨ 支持标准的AXI3.0接口。

⑩ 在14 ~70个命令(根据猝发长度)范围内,从接口可以接受更多的读操作。

⑪ 在8 ~32个命令(根据猝发长度)范围内,从接口可以接受更多的写操作。

(3)AXI_GP,提供四个通用端口。

① 它包含两个32位主接口和两个32位从接口。

② 在PS和PL之间,异步时钟域可以穿越所有AXI接口。

③ 支持标准的AXI3.0接口。

(4)AXI_ACP,提供了64位从接口。连接到侦测控制单元SCU,用于CPU和PL之间的高速缓存一致性。

4.2.2、配置信号

包含处理器配置访问端口(Processor Configuration Access Port,PCAP)、配置状态、单个事件翻转(Single Event Upset, SEU)和Program/Done/Init(编程/完成/初始化)。在PL配置块内的这些信号连接到固定的信号,用于PS控制。

更多总线互联(AXI/AHB/APB)的协议和时序等,可以参考 ARM 官方的技术文档,或者:

AMBA 协议文章