记一次ZYNQ板卡无法启动问题的调试过程

1.现象

板卡上电无法从QSPI启动,板卡为调试板卡,没有复位系统,QSPI FLASH中已经烧写boot.bin,要成功启动,分为下面四个阶段,首先bootrom上电后会根据boot mode(由配置MIO的管脚电平组合决定,即跳线帽),从对应的启动介质中读取镜像,读取开始的时候会先读取头部信息,如果成功则才会load启动代码,将fsbl读到ocm运行,然后由fsbl去启动uboot。

2.调试过程

2.1启动跳线帽问题

查看启动跳线帽的设置,发现已经打到QSPI处,多次启动没有输出后,修改fsbl的debug info,将调试信息加上,利用jtag对fabl进行调试,此时发现一个现象:

Jtag时常会起不来,跳线帽打的是jtag启动模式还是QSPI模式,都有可能jtag起不来,jtag起不来的时候,串口会输出一行“ZYNQ XLINX”,如果串口不输出,则有很大概率起来。在jtag起来后,单步fsbl,发现每次读到打boot_mode不一样,即:硬件跳线帽不改,软件不改,启动的boot mode也不确定。

结论:boot mode处的硬件关键状态不确定,导致boot mode不定

解决方法:硬件工程师去掉两个电阻,boot mode确定。

2.2 u-boot的有效性验证

利用sdk直接将生成的u-boot.elf镜像down到内存,可以拉起来,并且uboot对板卡的串口网络初始化均为成功,可以使用u-boot操作qspi flash,可以tftp下载reworks。

结论:u-boot可以启动,能够引导reworks,可用

2.3 FSBL的有效性验证

将fsbl通过jtag down到内存,运行后发现串口uboot启动,说明fsbl加载到内存后,可以正常运行,重新启动,load fsbl,单步跟踪,发现fsbl执行以下操作:

Ps7_init

Cache初始化

初始化异常处理函数

初始化并检测DDR

初始化PCAP

读取boot mode寄存器

初始化QSPI

检测是否是线性模式(是)

搬运image

启动

用示波器连接QSPI的CS管脚,因为要从QSPI读取数据,需要选中QSPI,在fsbl运行后,CS片选信号明显被拉低一段时间并保持,该段时间uboot被从qspi flash读出来并且运行。

结论:FSBL能够从QSPI搬运启动镜像,可用

2.3 BOOT.BIN烧写验证

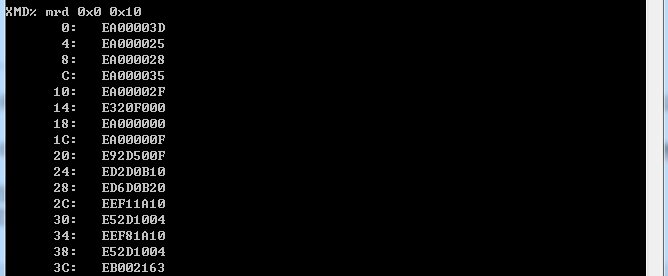

BOOT.BIN在制作的时候,会有特定的头供bootrom去读取,将我们烧写到qspi的0地址的头读出来与相似板卡的头部信息对比,发现头部信息完好,除了标志镜像大小的字段不一样,其余均为一致,且该字段为sdk在打包boot.bin的时候生成。将该boot.bin烧写到zedboard,发现可以从zedboard启动,头部同步字与烧写到z7045板卡一致。

结论:boot.bin的header 同步字完好

2.4 bootrom启动验证

fsbl是否被BootROM正常加载到OCM里面了,如果正常加载到了OCM里面,那就是fsbl执行阶段的问题,如果没有正常加载到OCM里面,那就是BootROM执行阶段的问题。如果fsbl正常加载了,那OCM里面的数据不会是空的,它里面会是BootROM读取进来的代码和数据,就像下面这样:

如果没有被BootROM正常加载,那上面的数据就是全0,在Z7045板卡上,读到的全部为0,说明fsbl根本还没有被加载,在bootrom阶段就出问题了,我将两个不同的板卡的boot.bin烧写到qspi flash里面,发现虽然串口没有输出,没有起来,但是我用jtag跟进去看到ocm里面是有数据的,也就是正常情况下,bootrom是可以将qspi里面的镜像读到ocm中的。

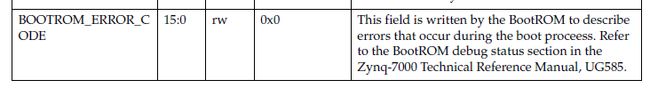

有个记录复位原因的寄存器REBOOT_STATUS,它的低16位获取到本次启动失败的原因:

通过mrd命令将该寄存器的值读出来:

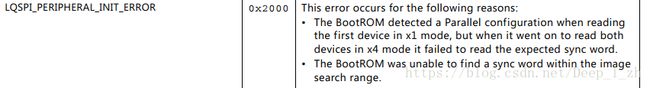

发现是0x2000,查看手册:

这句话就是说bootrom在读取qspi flash的时候出错了。

3.结论

在bootrom到qspi这段没有信号或者信号不明确。

4.解决方案

1.查看原理图和PCB图,与参考设计中bank的电压,上拉下拉的电阻阻值对比,当前是否正确合适,更换电阻等元器件。

2.更换qspi flash,建议更换型号为与参考设计一致的型号。

2018-08-08更新

问题描述:

关于zynq boot的问题,描述如下:

芯片型号:z7045

1.zynq启动顺序为bootrom->fsbl->uboot,现在我制作了一个fsbl和一个uboot,fsbl以及对应的BSP是根据vivado导出的hw_platform生成的,fsbl用jtag下载可以运行,并且可以读到qspi flash的镜像进行加载,uboot同样可以顺利用jtag拉起来运行,操作qspi flash以及tftp网络加载。

2.但是将制作的boot.bin烧写到qspi后,无法自启动。bootrom在上电后,会根据mio的配置管教去对应的介质引导,这时候会将数据读到ocm中进行加载,我在自启动失败后,用jtag attach上去后,发现ocm数据为空,也就是qspi中的引导镜像根本都不会被读到cpu去运行。

3.利用jtag查看错误状态寄存器,发现返回的错误指示bootrom读到了错误的hreader信息。于是,我将烧写到qspi的镜像头部全部读出来看了下,发现与完好可以启动的头部信息除了镜像大小的位不一样,其余都一样,并且与手册对比,发现无误。

4.由于上电bootrom在操作qspi的时候,必然会将片选信号拉低,我用示波器捕捉,发现可以顺利启动的zynq开发板,上电cs管脚是高电平,随后拉低保持一段时间,这段时间恰好是读取qspi的时候,读完又会被拉高。但是该板卡,上电后,只有一个很短暂的下降脉冲,其余一直为高电平。

5.该板卡的电路设计参考zedboard,一开始的时候启动配置的mio管脚电平不稳定,去掉了两个电阻后,boot mode才确定,现在查看电路,下拉电阻的阻值和参考设计相差1K,总值为21K。

6.该板卡配置的bank电压为bank0 2.5v,qspi在vivado中的配置MIO confiiguration为single SS-4bit IO,且没有配置feed backCLK。

7.将制作的改办卡的boot.bin烧写到zedboard上,能够启动;

最终问题确认:

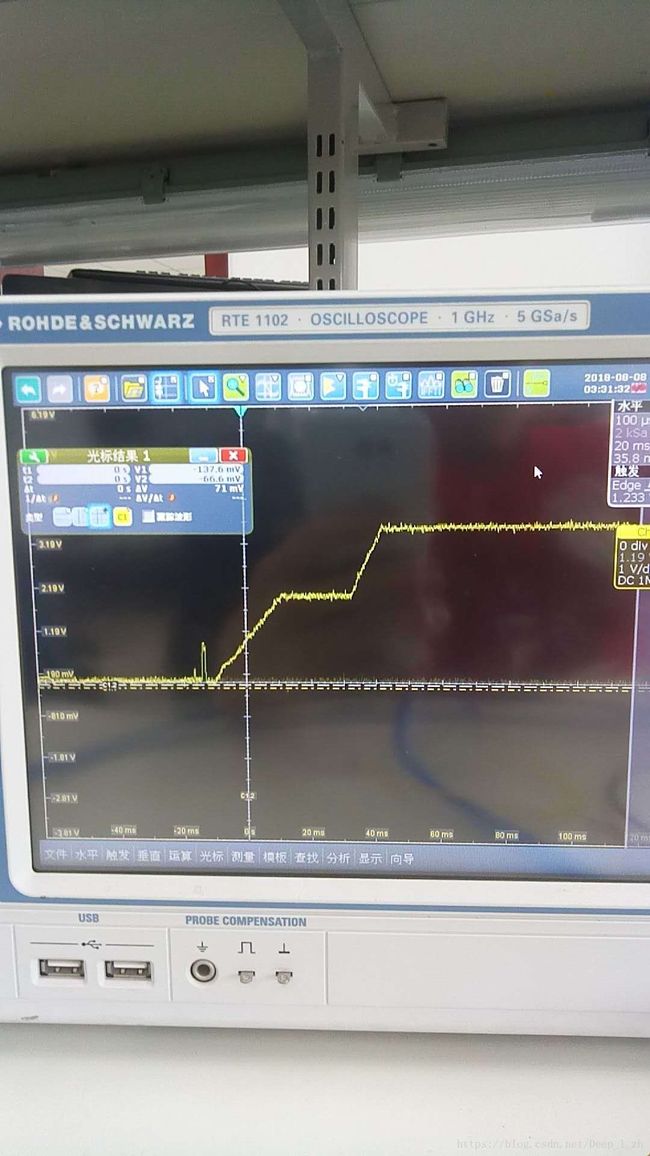

上电瞬间flash的管脚信号非常不稳定,怀疑flash的供电问题,启动时用示波器去抓,发现CPU供电运行时间为20ms,而FLASH的供电运行时间为60ms,flash上电后电源信号如下图:

这就导致在CPU启动后,去读取FLASH的时候,FLASH还没有启动,所以导致自启动失败。

解决方法:

将板卡上的稳压芯片上电时序更改,调整上电时序,使得CPU起来之后,FLASH也已经正常工作。