安森美PYTHON系列CMOS图像传感器FPGA开发方案简介

1、PYTHON系列传感器介绍

可参考这篇博客:https://blog.csdn.net/haoxingheng/article/details/90749082

2、开发所需的官方资料

- 文档:datasheet、评估板原理图、PYTHON Frame Rate Calculator (PFC) User's Manual、PYTHON Image Sensor Family Developer’s guide(需签NDA)

- 软件:PYTHON Frame Rate Calculator、Sensor Studio II(需注册账号)

- 代码:寄存器配置脚本(需签NDA)

当然,还有很多其他资料,有的可以直接下载、有的需要注册账号或签DNA。但对于FPGA开发来说不是必需的。有兴趣的可以下载查阅。

3、FPGA开发要点

本文以PYTHON5000/2000为例进行描述。其他型号大同小异。

建议读者先大致浏览一遍datasheet,便于理解。

FPGA的主要工作为:寄存器配置、LVDS解串、像素重组。

3.1 上电、复位、寄存器初始化

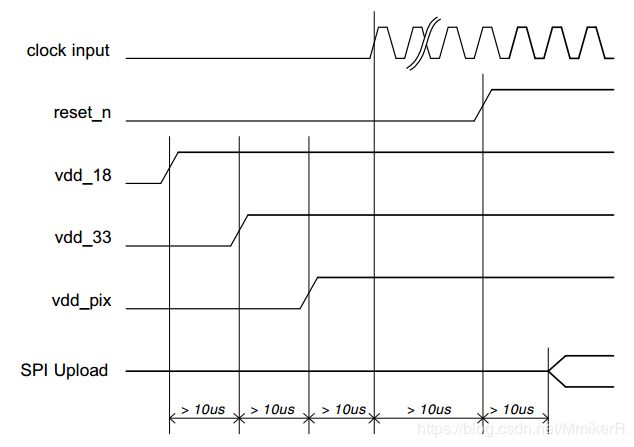

datasheet中的上电时序图

如果不遵守此时序,有可能会导致sensor上电后出现某些异常现象,甚至不能正常工作,但也不是百分百会出现。因此,为确保万无一失,还是应该严格按照图中的时序控制sensor的上电、复位、初始化。

3.2 寄存器初始化列表

上电之后的寄存器初始化分为4个步骤:

- Enable Clock Management

- Required Register Upload

- Soft Power Up

- Enable Sequencer

每个步骤具体的寄存器配置列表需要按照官方提供的脚本文件进行。(脚本文件签NDA后即可单独获取。若未签NDA,可以注册账号下载Sensor Studio软件安装,在安装目录下可以找到对应sensor的.py脚本文件)。其中,有相当一部分寄存器在datasheet中是无法查到或是被描述为reserved。对于这部分寄存器,按脚本文件的设置即可,不要做任何改动。用户可以对例如ROI、帧率、曝光时间、增益、黑电平等一些常规参数的寄存器进行自定义修改。

3.3 寄存器配置

3.3.1 SPI接口

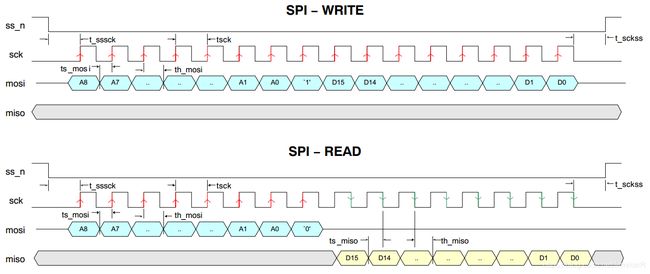

寄存器配置是通过SPI接口完成的,时序图如下:

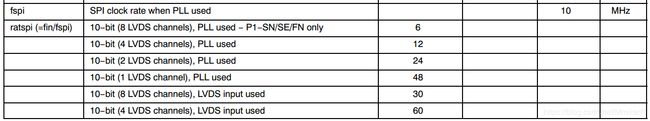

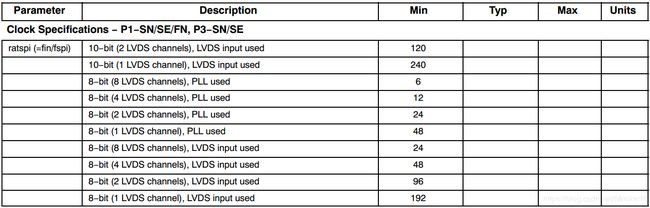

需要注意的是,SPI接口的最高频率与sensor输入时钟、像素bit位宽以及所使用的LVDS通道数有关。仅仅知道最高10M是不够的。见下图。

举个例子,sensor通过外部晶振接入72M的时钟,当配置为10bit、8路LVDS输出时,fin/fspi的最小值为6,fspi理论最大可以达到12M,但datasheet限制最高为10M,因此可用的SPI最高频率为10M。相同条件下,若配置为4路LVDS输出时,fin/fspi最小为12,fspi最大为6M,因此此时可用的SPI最高频率仅为6M。其他情况可按表类推。

另外,还需要注意,相邻两次SPI读/写操作需要至少间隔2个时钟周期。

3.3.2 寄存器动态配置

当sensor上电初始化完成开始正常输出图像后,用户希望对例如ROI、帧率、曝光时间、增益、黑电平等等参数进行修改,此时便涉及到寄存器的动态配置。有些寄存器可以在出图过程中修改,同时不会影响sensor的工作,有些寄存器则必须在sensor停止出图时才能修改,否则会影响sensor的正常工作。另外,调整某些参数有时需要修改多个寄存器,由于配置存在先后顺序,在此期间可能会有多幅图像输出,为了使修改后的寄存器同步生效,需要采取额外的同步措施。关于这部分内容,在datasheet中有详细介绍,此处不作赘述。

3.4 LVDS解串

LVDS解串是FPGA开发过程中比较重要的一个环节,由于sensor的输出为:8/4/2/1 data + 1 sync code + 1 clock,可以采用DDR源同步思想进行设计。Xilinx为7系列FPGA提供了一个很好的参考设计XAPP1017,稍作修改便可直接使用。

XAPP1017中LVDS解串分为2个过程:

(1)bit对齐

首先通过调节IDELAYE2的延时找到clock的边沿,由于是源同步传输,所有LVDS通道相位大致上是对齐的,因此就可以粗略确定sync code和data数据窗口中心位置对应的延时值。然后通过IDELAYE2调整sync code和data的LVDS信号的延时,使clock的边沿位于sync code和data数据窗口中心附近位置,保证采样时序最优。并且通过动态相位调整功能,在LVDS数据接收过程中持续的检测clock与sync code、data的相位关系,并及时调节IDELAYE2的延时值,始终保证clock的边沿在sync code和data数据窗口中心位置附近最小范围内波动。

动态相位调整可以消除PCB走线以及FPGA芯片package pin延时差造成的LVDS相位误差,以及温度和电压波动造成的相位抖动的影响。

每一组差分信号可以接2个ISERDESE2,2个ISERDESE2级联可以实现1:10~1:14的解串。由于动态相位调整功能需要使用1个ISERDESE2,所以只有1个ISERDESE2可以用于解串,单个ISERDESE2可以实现最大1:8的解串,对于10bit以上的并行数据需要通过逻辑(gearbox)实现二次位宽转换。

(2)word对齐

sensor初始化完成后,在没有图像输出时,data channel和sync code channel均持续输出相同的training pattern(TR),利用这个固定的training pattern便可以通过ISERDESE2的bitslip功能(8bit mode)或者逻辑(gearbox)实现bitslip功能(10bit mode)锁定data和sync code每个bit的先后顺序,从而完成word对齐。注意bit的高低位顺序不要搞反,sensor LVDS首先输出高位bit。

https://blog.csdn.net/haoxingheng/article/details/50320145这篇博客对相关的知识有比较详细的介绍。

3.5 像素重组

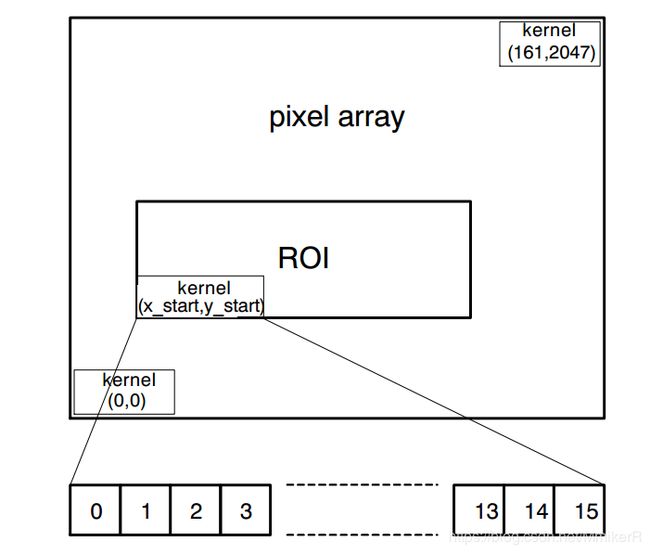

LVDS解串完成,data和sync code都被还原成并行数据,接下来就要根据sync code提取出data channel中连续的图像像素。首先,需要了解sensor内部的像素组成及输出顺序。sensor内部的像素以kernel为组,并交替分为even kernel和odd kernel。每个kernel 16个像素点。

even kernel和odd kernel的像素点与LVDS通道对应顺序是相反的。对每个data通道LVDS输出的像素点进行重新排列即可得到一幅完整的图像。

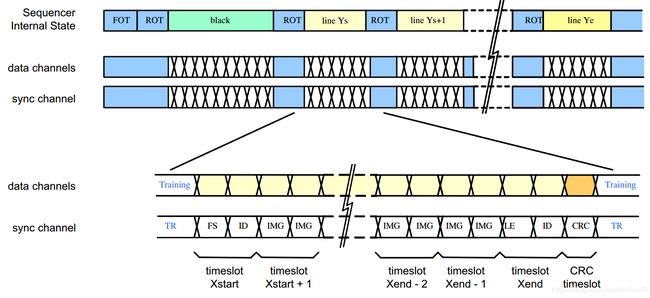

下面附上datasheet中的关于sync code的一张图,sync code在datasheet和developer’s guide中均有介绍。需要注意的是8bit mode和10bit mode对应不同的sync code。

对于单个ROI的应用场景,如果只要实现全画幅像素点提取功能需要关注的sync code只有如下4个:

FS(Frame Start)、FE(Frame End)、LS(Line Start)、LE(Line End)。

如果要实现单个任意长宽及位置的ROI像素点提取,由于even kernel和odd kernel的像素顺序不同,所以需要加以区分,此时要将FS、FE、LS、LE分为even和odd两类,即even FS、odd FS、even FE、odd FE、even LS、odd LS、even LE、odd LE。这可通过配置sensor寄存器来实现,参考datasheet和developer’s guide。

FS和FE可以用于产生场同步信号,LS和LE可以用于产生行同步信号。

另外,还有个高级功能,每一行像素对应的所有LVDS通道的最后都会附上本通道像素的CRC。这可以被用来测试LVDS的误码率,检测信号完整性或sensor工作稳定性问题。如果想验证每个LVDS通道像素的CRC是否正确,还需考虑sync code为CRC时提取末尾的CRC校验码,并在FPGA中对每一行像素对应的每个LVDS通道的数据进行CRC值的计算和比对。

10bit CRC计算公式:

8bit CRC计算公式:

CRC计算的FPGA代码可以通过:https://www.easics.com/webtools/crctool网页中的在线工具自动生成。将生成的代码作为1个function,以组合逻辑的形式在代码中调用即可。

3.6 曝光采图模式

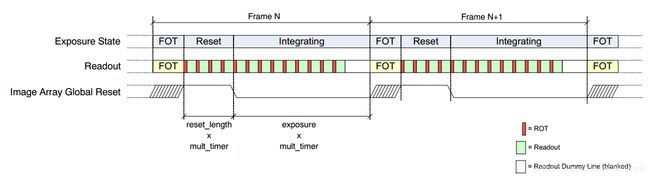

sensor一共有3种曝光采图方式:

1、Pipelined Global Shutter (连续自动方式):设置完帧率和曝光寄存器,将reg192的bit0置1后,sensor便按照设定的帧率和曝光时间自动连续输出图像。

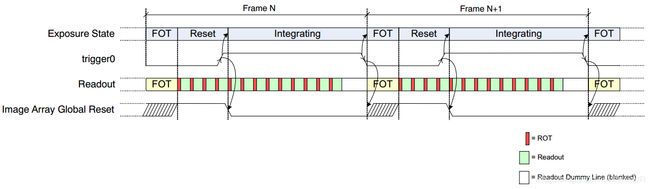

2、Triggered Global Shutter (Master)(master外触发方式):sensor的trigger0脚输入脉冲上升沿触发曝光,脉冲频率决定帧率,寄存器配置控制曝光时间。此时帧率控制寄存器不再起作用。

3、Triggered Global Shutter (Slave) (slave外触发方式):sensor的trigger0脚输入脉冲上升沿触发曝光,脉冲频率决定帧率,脉冲宽度控制曝光时间。此时曝光时间和帧率控制寄存器都不再起作用。

对于后2种外触发模式,FPGA需要产生脉冲信号通过tigger0引脚触发sensor曝光出图。

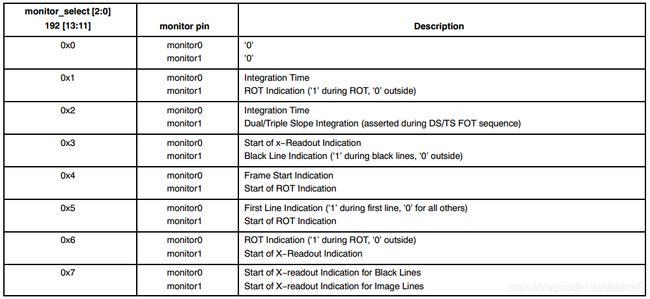

3.7 Monitor信号

sensor有两个对外输出信号monitor0和monitor1,可以监控senosr在输出图像过程中的状态。利用这些信号可以便于实现一些额外的功能,例如在sensor处于曝光期间精确控制闪光灯补光,输出同步信号控制其他外设等等。

4、PYTHON Frame Rate Calculator软件使用

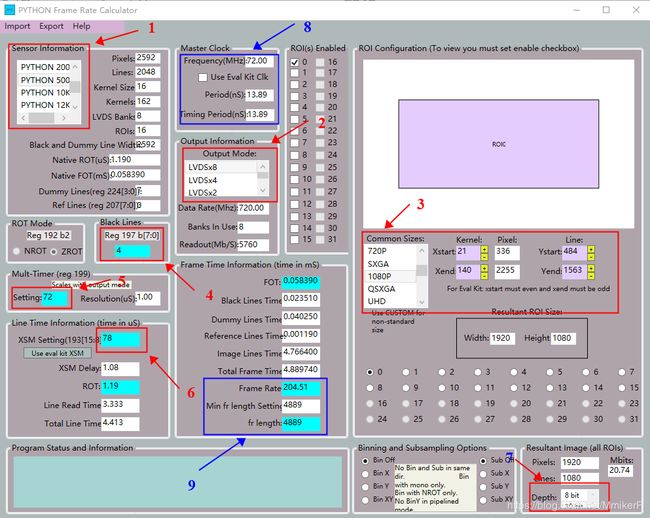

安森美官方提供了1个PYTHON Frame Rate Calculator软件,这个软件可以用于调节某些参数,然后评估不同参数下sensor可以达到的最高帧率。软件的使用手册为:PYTHON Frame Rate Calculator (PFC) User's Manual。常规的使用方法如下:

1、选择sensor型号

2、选择输出的LVDS通道数

3、配置输出的ROI尺寸及偏移

4、配置black line的行数,black line位于每一幅图像有效像素之前,主要用于sensor内部的黑电平自动校正。这个参数根据寄存器配置脚本默认的配置值即可,一般不作修改。

5、Mult-timer配置,这个参数与输入时钟频率和LVDS通道数有关,是曝光时间和帧率的最小时间单位。计算公式为:

最小时间单位=输入时钟周期×mult-timer/(sensor最大LVDS通道数/当前配置的LVDS通道数)

按图中的设置,输入时钟频率为72M,则13.889ns×72/(8/8)=1000ns=1us

6、xsm delay设置,这个参数用于控制行与行之间的消隐时间,值越大消隐时间越大。具体参考developer’s guide。计算公式:

xsm delay时间=输入时钟周期×xsm delay/(sensor最大LVDS通道数/当前配置的LVDS通道数)。

按图中的设置,输入时钟频率为72M,则13.889ns×78/(8/8)≈1083ns≈1.08us

7、8bit、10bit模式设置,这个设置没什么用,只是软件里显示的数据输出带宽(Mb/S)会产生变化,可忽略。

8、输入时钟频率设置,这个参数在软件中没法直接修改,只能通过import导入脚本的方式才能修改。

9、最终根据用户上述参数设置,软件会自动计算出当前参数配置下sensor输出的最高帧率和相应的帧率设置(fr length)。

另外binning和subsampling设置也会影响帧率,一般情况下用不到这两个功能,有兴趣的可以自行研究。

5、图像校正

https://blog.csdn.net/haoxingheng/article/details/90749082中提到在FPGA中需要做固定偏移噪声(FPN)和像素响应非均匀性(PRNU)校正。developer’s guide中也建议用户对PYTHON系列sensor输出的原始图像按列进行FPN和PRNU校正。

就sensor输出的原始图像而言,FPN和PRNU的影响较弱,除了拍摄亮度或者颜色很均匀的物体,肉眼很难察觉。针对亮度和颜色均匀的物体,校正之后的图像质量确实有明显改善。校正的基本原理可以用下面的公式表示:

主要就是计算上面两个coe校正系数,关于校正的原理和过程在developer’s guide中有详细介绍。