Linux嵌入式开发入门(二)——快速看懂原理图,对接软件开发

这里只是为了看懂原理图,不牵扯具体的计算等内容(比如电路电流多少啊,三极管放大等等)。因为对于嵌入式开发人员来说,只需要明白不同的电平对于开发板的结果即可,不需要知道具体电路的情况。

微机原理:侧重于讲计算机结构

数字电子技术基础:侧重于门电路

- GPIO和门电路

- GPIO类

GPIO:通用的输入输出端口,可以通过输入来测量外界的电平情况;可以通过输出来控制电路

- GPIO类

只要上面的2440芯片对应的引脚应该为输出引脚。如果对应的输出引脚输出3.3V的高电平LED就会被点亮;如果输出引脚输出低电平(0V),那么LED则不亮

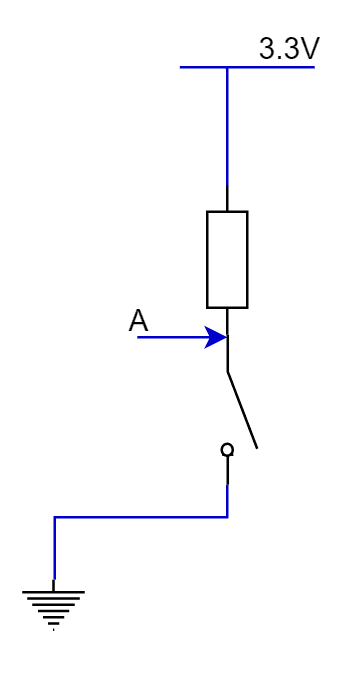

以上的线路很简单,开关闭合线路接通有电流;开关打开,线路不导通,无电流。

如果在开关打开的前提下,A点使用万用表测量,电压应该为3.3v,因为,如果此时这里不为3.3V与之相连的上方为3.3V就会形成电流,与实际不符;如果此时开关闭合,那么该线路是接通状态,应该有电流流过,那么此时,A点的电流应该为0V。

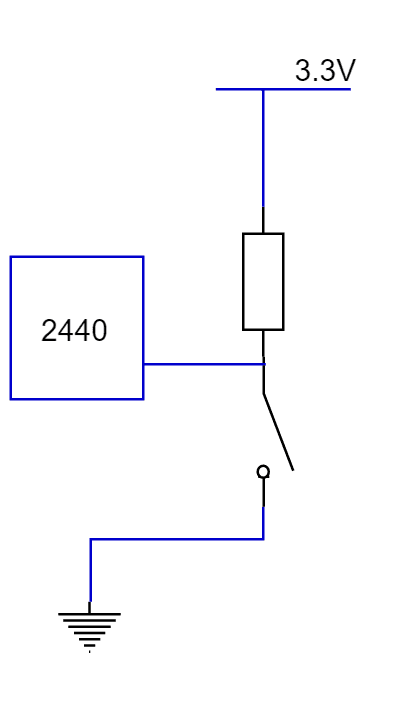

那么如果把万用表换成2440芯片会得到。

那么此时2440对应的引脚应该为输入引脚,通过读取该引脚对应的寄存器中的数据,就可以知道该引脚为高电平还是低电平。如果读到了高电平,说明此处为3.3V电路没有接通了如果读到了低电平,说此处为0V,说明电路接通了。以此可以判断开关的开闭情况。

对于现在的芯片的引脚来说,既可以作为输入引脚,同样也可以作为输出引脚。可以通过配置其中参数的某一位(具体参照手册)的方法来改变其功能。

输出引脚,写值到某个寄存器中

输入引脚,读某个寄存器中的值。

实际原理图

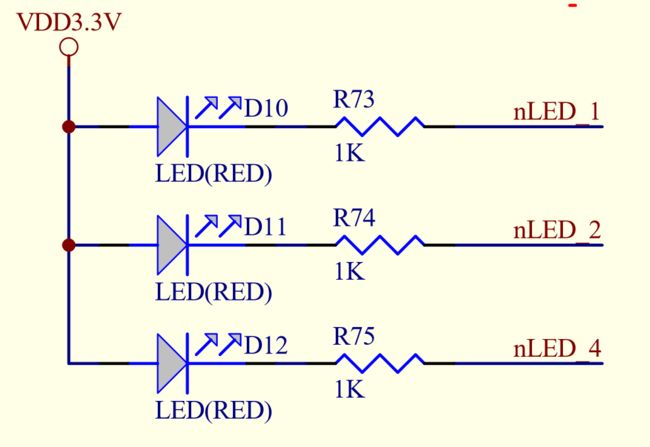

由以上两幅图可以看出,LED由某一个引脚引入到芯片中。就可以找到对应的芯片中的引脚。通过该芯片手册就可以查到该如何操作。

由LED的原理图可以看出,三个控制LED的引脚的功能都不是为了检测电压,那么都是输出引脚,也就是如果输出了低电平,则LED被点亮;输出高电平,则灯会熄灭。

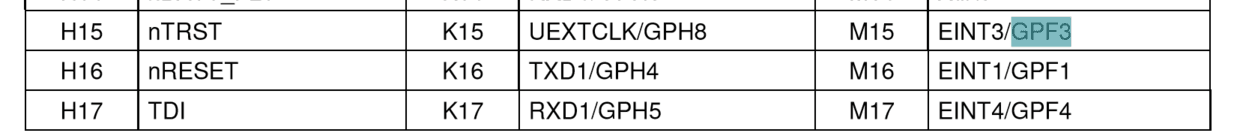

在芯片手册中查询该引脚的信息

查看到pin name为EINT3/GPF3 的引脚的pin number为M15

可以看到该引脚既可以作为输入引脚也可以作为输出引脚

可以在I/O port章节中看到,这一组引脚的应该如何配置

那么如果将GPF的寄存器配置为EINT[4]时,则该引脚会成为中断引脚

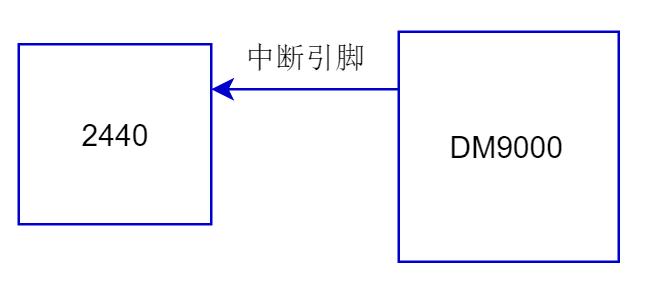

对于假设2440外连接一个DM9000的网卡,如果网卡收到了数据,如何来通知2440芯片呢?如果定时让2440去查询DM9000,是一个非常耗费资源的工作,那么这时候,如果把对应的引脚设置为中断引脚,只要DM9000获得了数据,就把想2440的中断引脚输出高电平,2440得到高电平后,向CPU发送中断信号,以执行相应的操作即可。

中断引脚,有输入功能,可以中断CPU(同样可以通过GPFDAT来获得数据已得到是否中断,但是比较耗费资源)

GPFCON就是配置GPF引脚的内存地址为0x56000050

参照接下面的表格可以看出,对于GPF4来说,需要操作8、9两位来控制该引脚的输入输出功能。具体的设置情:00 = Input 01 = Output 10 = EINT[4] 11 = Reserved

那么如何设置该引脚输出低电平来点亮LED呢?

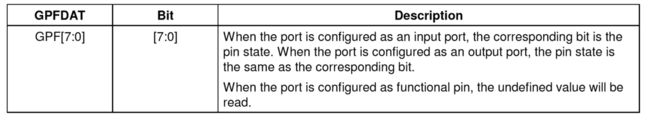

在GPFDAT中可以看到数据配置信息的地址为:0x56000054

可以看到,如果配置为输入引脚,那么对应的位中的数据就是读取到的数据,也就是读到1为高电平,读到0为低电平。如果配置为输出引脚,如果写入1为输出高电平,如果写入0则输出低电平。

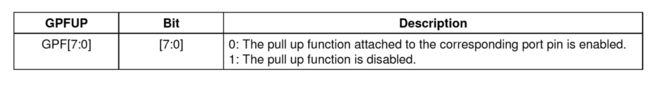

在手册中不难看出,还有一个GPFUP

这个是上拉电阻的意思,至于上拉电阻的问题,还需要看看三极管。

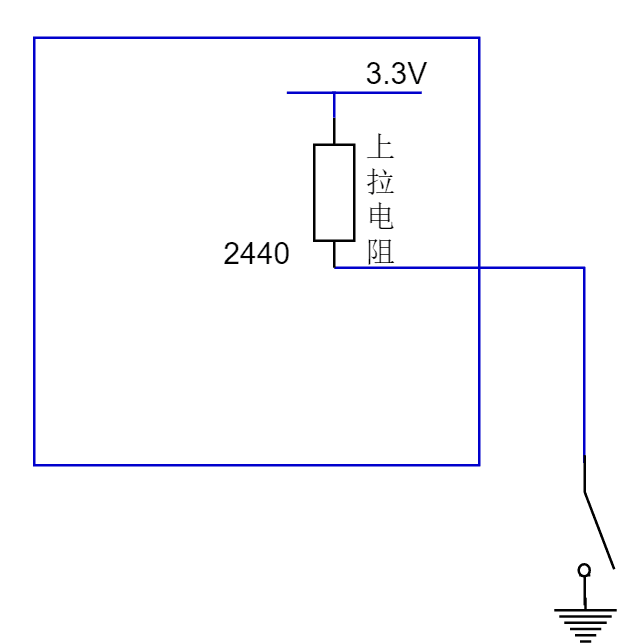

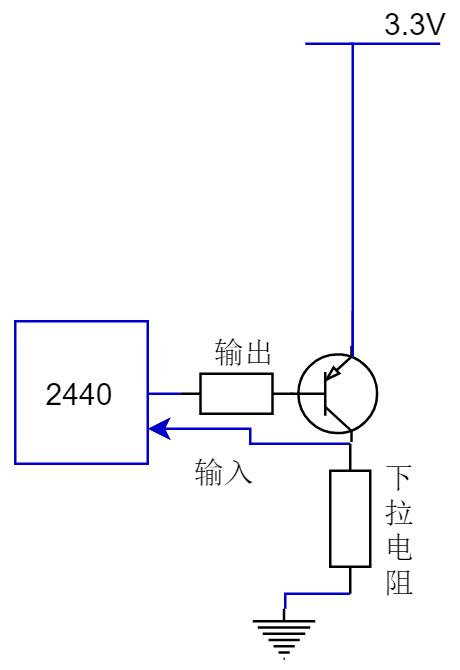

对于NPN三极管来说,如果此时2440芯片的引脚为输出引脚,并且输出的为低电平,那么此时,三极管处于不导通的状态。但是对于三极管另外一个管脚来说,状态未知,所以,在此管脚上接通一个电阻,以方便得到他的状态。

那么此时,如果输出一个低电平,三极管不导通,那么,此时的输入管脚会得到一个高电平。而反之,如果输出为高电平,那么输入会得到一个低电平。所以输出和输入为反相的情况。

那么引脚的上拉功能是什么呢?可以假设在芯片内部存在一个上拉电阻,当寄存器设置为1则该电阻不通电。

假设这样的电路,其中上拉电阻是位于芯片内部的,对应的引脚是输入引脚,如果上拉电阻设置为断开,此时开关也不打开,对于中间一段电路来说是“悬空的”,无法获取其中的电路。

如果此时设置了上拉功能,就出现了图上的情况,是一个完整的电路,也就可以测量出芯片外的电平情况。如果获取到的信息为高电平说明开关未被按下;如果获取低电平,说明此时形成了回路,开关被按下。

上拉电阻的作用,对于输入引脚,可以用它来确定电平状态。

还存在一种下拉电阻的情况

对于PNP类型的三极管来说,如果2440芯片输出低电平,那么此时三极管处于导通的状态,此时输入能够得到一个高电平;那么反之,如果输出是一个高电平,三极管不导通,那么此时输入会得到低电平。

上拉电阻和下拉电阻的作用主要是为了,确定“悬空的引脚”的确定的状态。

- 门电路

-

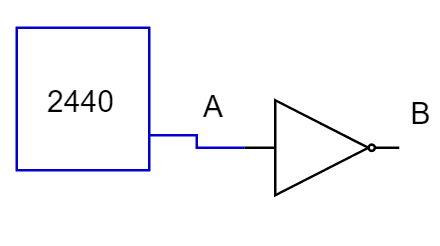

非门

对于非门来说,如果2440输出高电平,在B端会得到低电平;反之,2440输出高电平,在B端会得到低电平

-

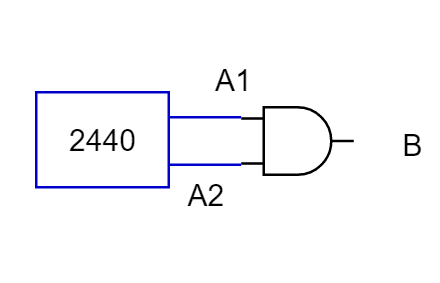

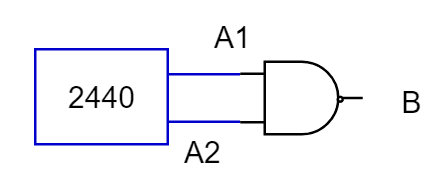

与门

-

对于与门是对A1和A2做与运算B = A1 & A2,如果A1和A2中只要任意一个或者同时输出了低电平,那么B会输出低电平;如果A1、A2同时输出高电平,在B会得到高电平

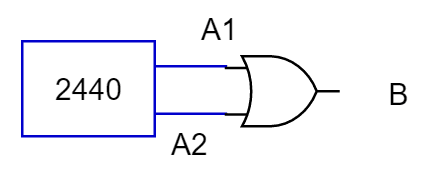

- 或门

对于或门来说,就是对A1和A2做或运算,

B = A1 || A2,当A1、A2中,只要输出至少一个高电平,对于B来说都会得到高电平。如果A1、A2同时输出低电平,那么B会得到低电平

- 与非门

- 或非门

-

协议类

协议类遵循的原则:

1.双方约定的信号协议(互相可以理解彼此的语言)

2.双方满足是时序要求(语速别人可以理解)

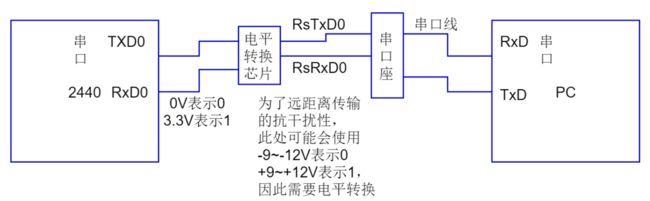

- UART串口(Universal Async Receive Transmit )

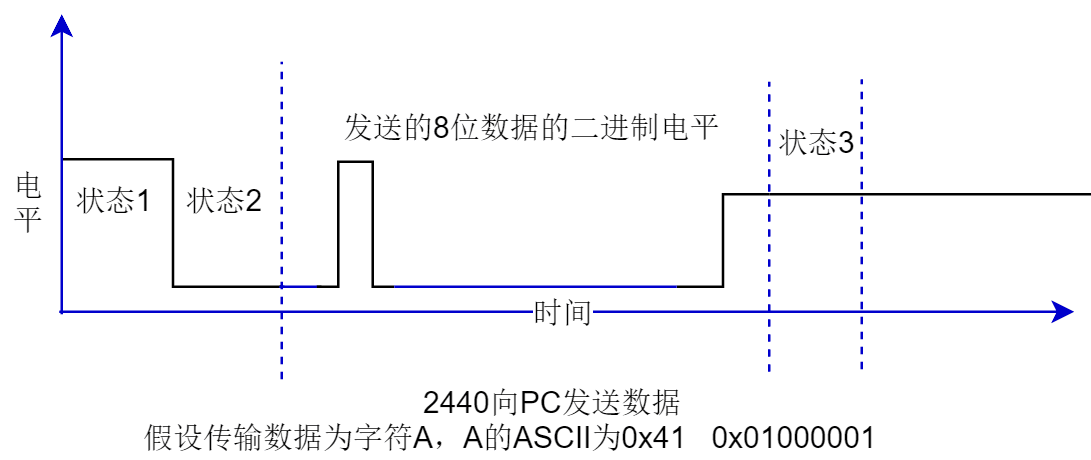

- UART如何传输数据

- 状态1:空闲。空现阶段为高电平

- 状态2:起始位。2440数据时,让RxD0为低电平,并保持一段时间T;PC机接收到低电平,就得到了2440即将发送信息消息;需要保持的时间为事先约定好的T,没办法自动约定。

- 状态3:停止位:保持高电平至少一个时间T。

- UART如何传输数据

我们不可能手动的发送电平,来和PC机通信。那么在2440上有一个串口控制器,我们只需要把串口控制器设置好,并且把数据发送给串口控制器即可,它会自动帮我们发送起始位、停止位、数据以及校验位的电平。

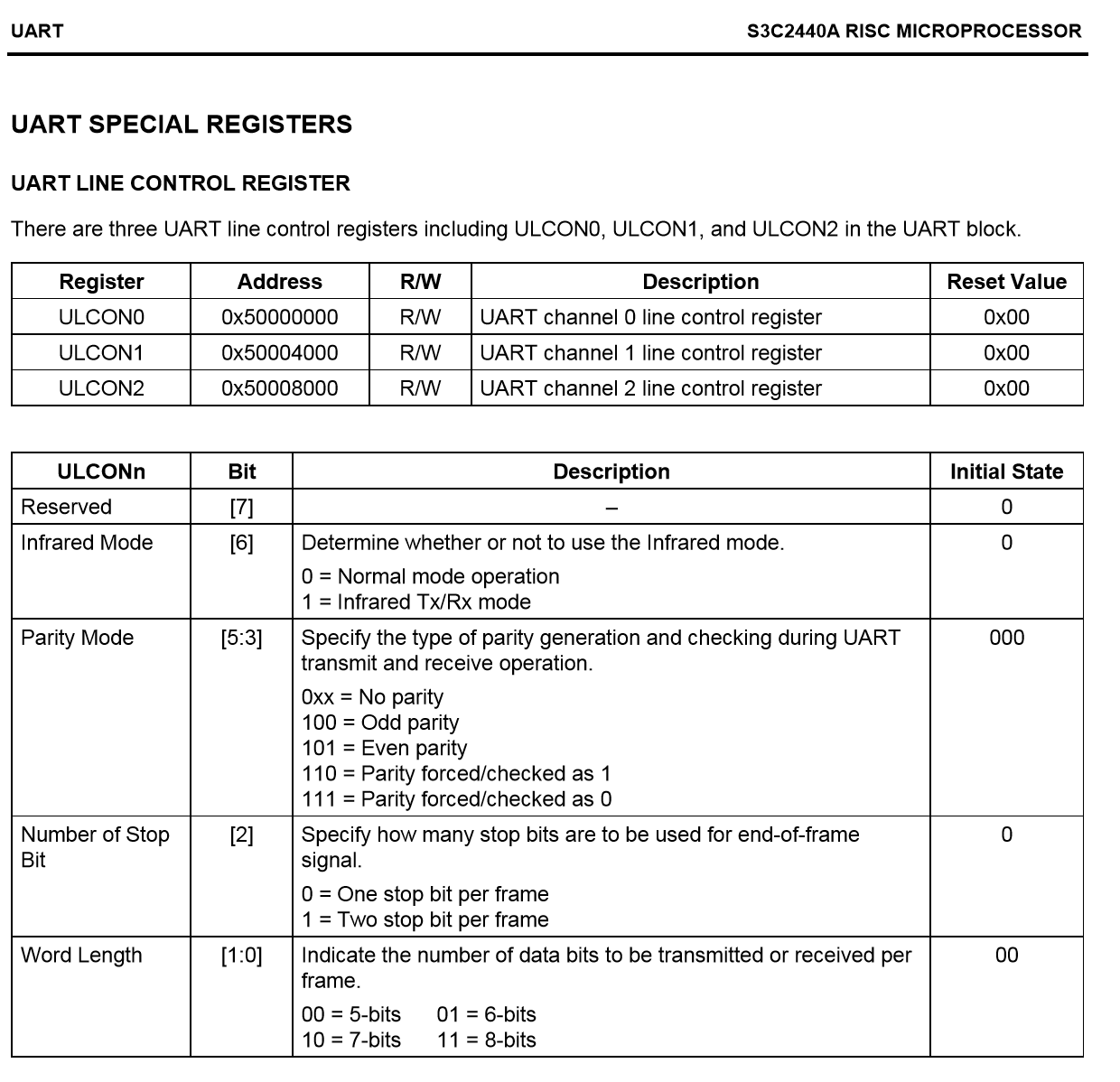

- UART串口(Universal Async Receive Transmit )

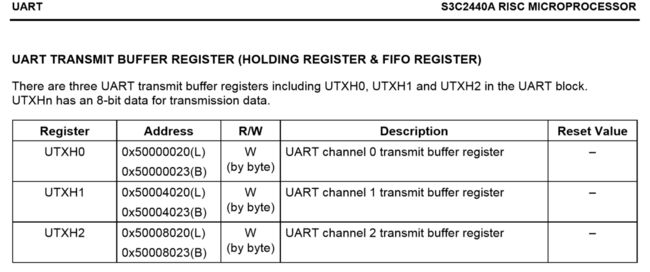

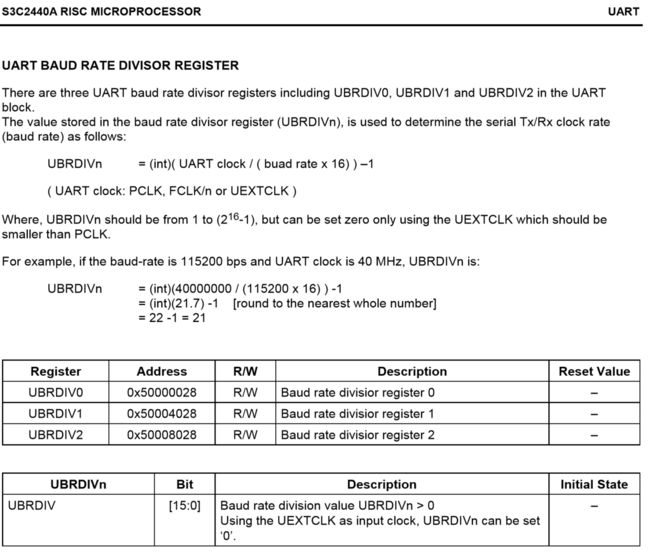

由手册可以看到,2440芯片具有三个串口的寄存器。寄存器中数据的不同位分别表示了数据长度、停止位、校验位等信息。

现在已经知道如何设置串口控制器的一些参数,以及数据应该放在哪个寄存器中。但是还有一个关键数据没有设置,那就是发送数据的速度——波特率

硬件上其实相对比较简单,最少只需要三条线即可完成串口,一条发送、一条接受还有一条参考地线。

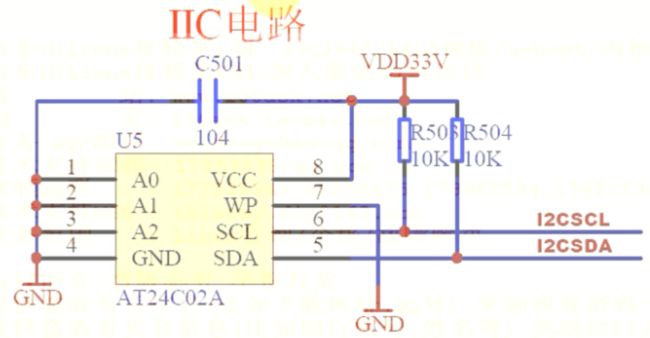

- I2C

每个I2C设备中一定有一个地址,只有地址相同的时候,才会响应。

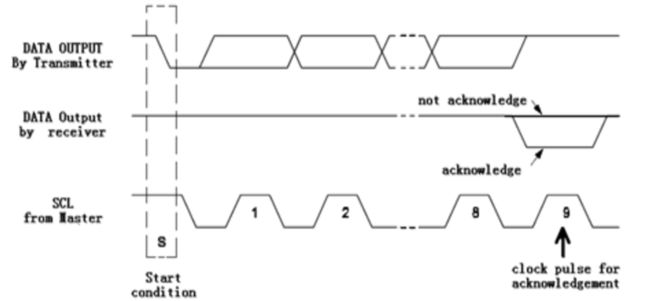

I2C开始发送数据,开始会先发送7位数的从机地址[可以在芯片手册里面获取](pow(2, 7) 为128,也就是最多可以有128个外置设备被同一个芯片控制),第8位表示读写状态。地址匹配完成会得到响应信号(ACK),说明这个设备是存在的。

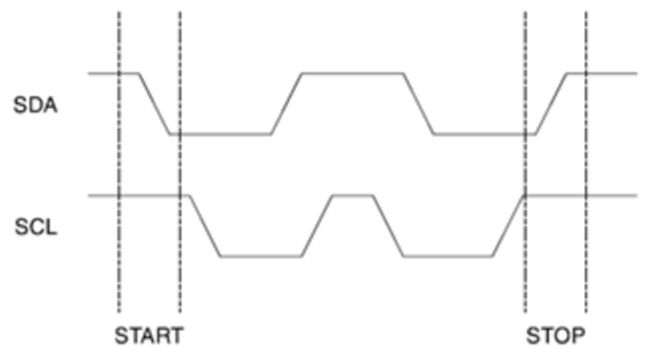

开始信号:2440让时钟SCL保持高电平,数据SDA由高电平调转到低电平

停止线号:2440让式中SCL保持高电平,数据SDA由低电平跳转到高电平。

响应信号(ACK):接收器在接收到8位数据后,在第9个时钟周期,拉低SDA为低电平。

也就是在第9个时钟周期,2440会将SDA设置为接受引脚,有AT24C02来驱动,以检测是否成功接收数据。

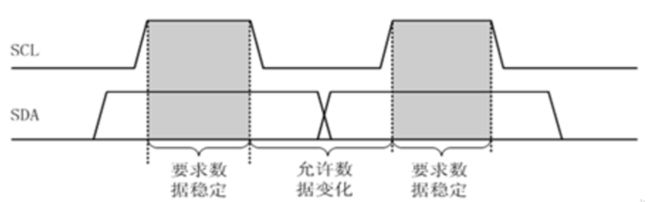

SDA上传输的数据必须在SCL为高电平的期间保持稳定,外部设备会在SCL在高电平的时候读取数据

SDA上的数据只能在SCL为低电平期间发生变化

不论是何种I2C芯片,start信号之后,都会发送设备地址,以及读写信息。之后的数据的含义需要具体查看对应芯片的手册上面的规则。

我们也不需要控制I2C的引脚应该如何控制电平,我们只需要控制I2C控制器即可。

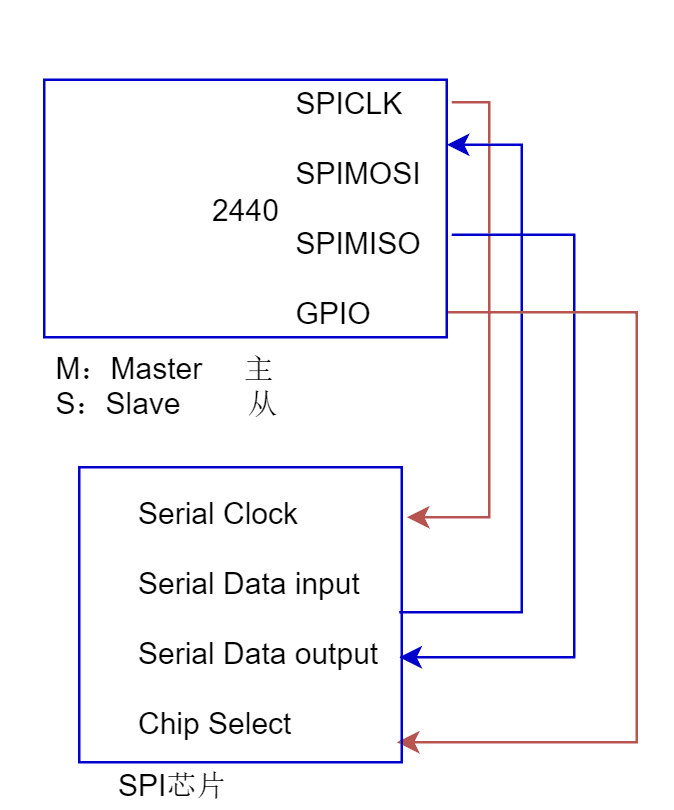

- SPI

其中片选引脚需要在2440上找一个GPIO引脚,并设置为输出引脚,以方便可以连接多个SPI设备。

与SPI的数据通信需要三条线,分别为时钟、输入、输出。

对于上方图示的SPI芯片来说,Vcc用于接电源来为SPI芯片供电。Vss接地。W接写保护,如果为低电平则无法对芯片进行写入。HOLD可以暂停任何操作,低电平有效。

对于硬件的接线,基本上是找到对应的引脚,将其连接在一起即可。数据传输,需要查看对应芯片的协议。

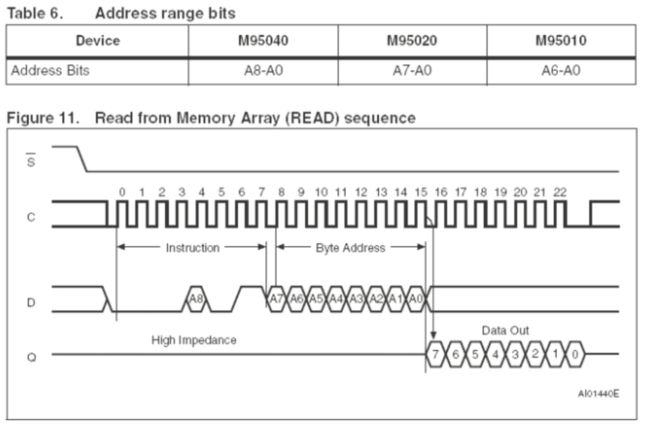

有芯片手册可以得到,开始8位被称为指令,其中包括9位地址的最高位,以及是写还是读。第二个八位数据是SPI芯片的地址。之后才是数据的传输部分。

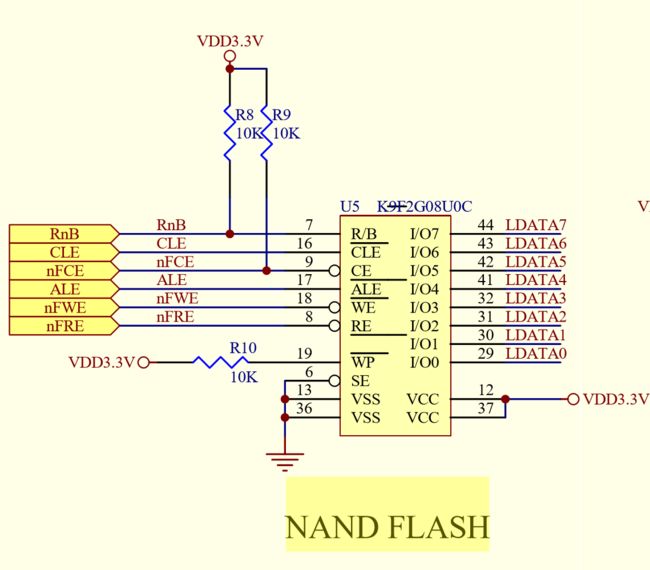

- Nand Flash

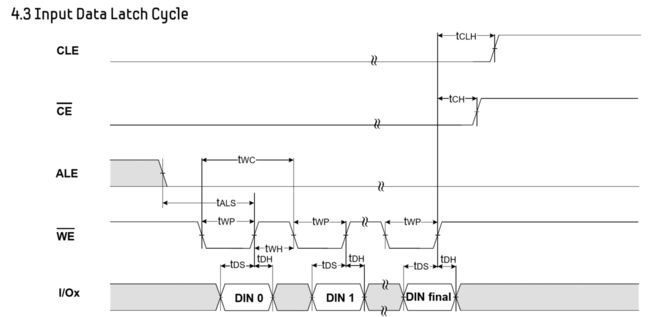

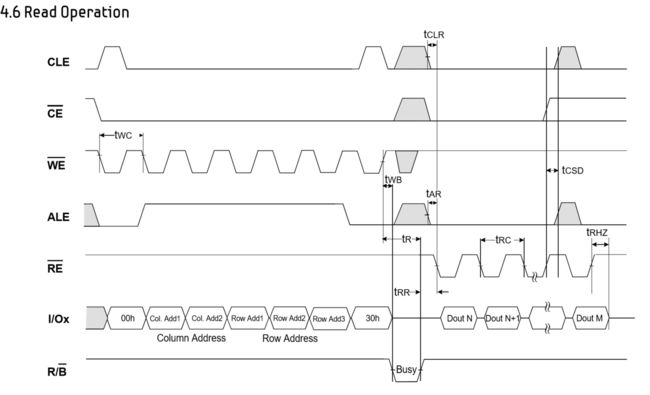

有说明可以知道,I/O0~I/O7的八个引脚可以用于传输数据、地址、命令(读写擦除等)。但是芯片如何才能区分这几个引脚传入的数据到底是地址、命令还是数据呢?

在芯片上还有CLE引脚,如果为高电平,表示这8个引脚所传输的为命令。ALE为高电平表示,8个引脚所传输的数据为内存地址。两者都是低电平是,那么说明这8个引脚上传输的是数据信息。RE为低电平是,说明信号是从2440到Nand flash,WE为低电平说明,是从Nand Flash读取信息。其中WP为写保护引脚,为低电平是为写保护状态。R/B为状态引脚,通过该引脚入股哦为高电平说明Nand已经完毕,可以操作,如果为低电平,说芯片还在工作,处于繁忙的状态

2440在发送脉冲的阶段必须有一定的时间要求,否则,可能Nand Flash不能反应过来。需要查询手册中的时序要求。

设置2440的Nand Flash控制器中的寄存器,可以使得2440发送的控制Nand Flash的信号满足要求

如何设置时序:

- 看2440手册,有哪些参数可以设置

看Nand Flash手册确定取值

-

进行计算,保证发送的信号符合Nand Flash的要求。

- LCD

协议类的的学习思路

- 看原理图:2440和外接芯片引脚对接即可

- 弄清楚接口的协议:数据如何传输,各引脚如何配合

- 设置时序:2440发出的各个信号,要让外接芯片可以反应得过来

- 看2440手册弄清楚能设置哪些参数以及这些参数的含义(以CLK时钟为单位)

- 看外设芯片手册,弄清楚这些参数的取值范围(以秒为单位)

- 根据之前的两条,计算2440寄存器的取值(进行秒和CLK之间的换算)需要计算每个信号何时发出以及发出该信号需要保持的时间

- 类似内存的接口类(RAM-like)

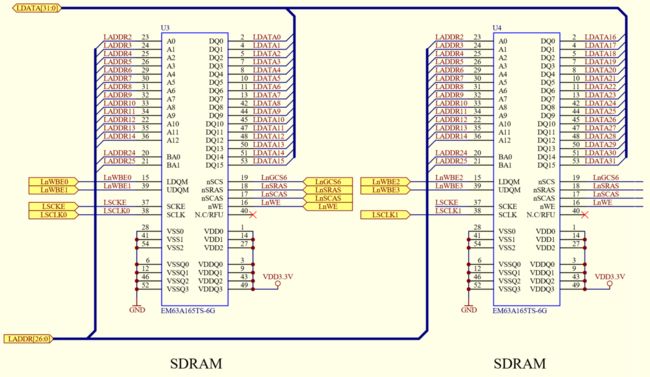

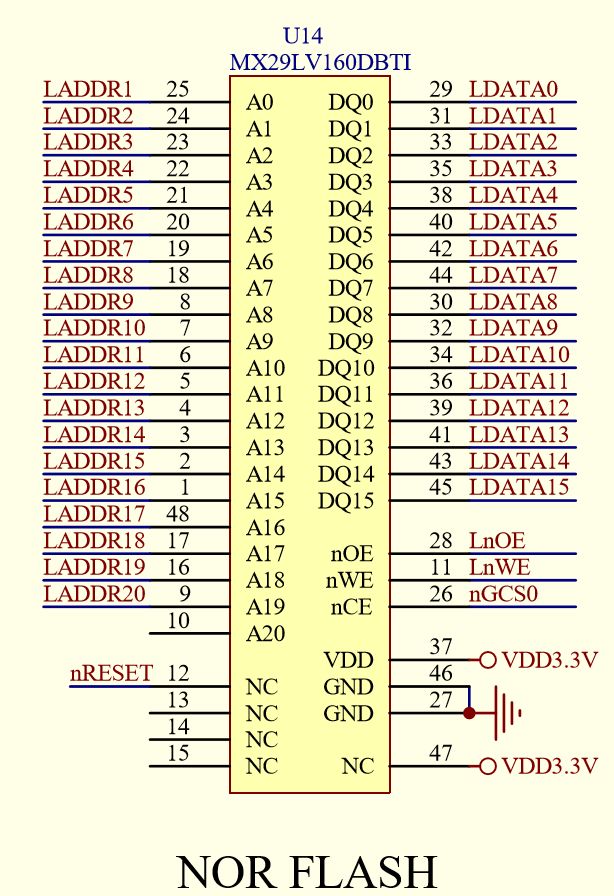

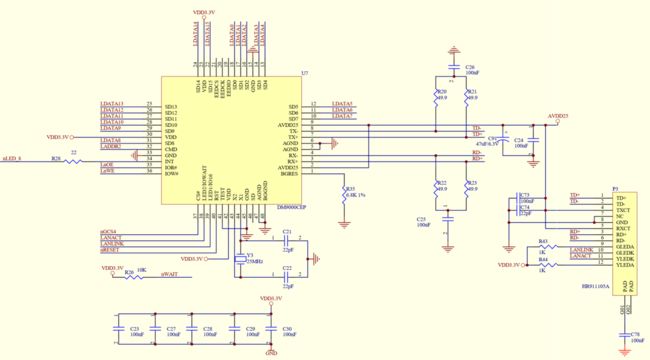

首先先看看关于几个芯片的的原理图

有这三幅图可以看出来,他们都有大量的地址线和数据线。

那么可以抽象出这样一幅图,这三个芯片上都有一组地址线通往2440芯片,同时也有一组数据线通往2440芯片。那么,2440在和SDRAM通信时,如何避免NOR FLASH和网卡不会造成干扰呢?

在这些芯片和2440连接的时候,每个芯片还都有一个独立的片选芯片/CSx (Chip Selected)。CS引脚是低电平有效,那么只需要将需要被选中的芯片的对应片选引脚输出低电平。

其中两块SDRAM芯片使用同一个片选线,那么此时可以一次性选中两块芯片,每次读取32位数据时,每个芯片可以提供16位数据。

我们不需要手工设置片选引脚。在2440中有一个内存控制器和CPU。CPU发出的地址信号发送给地址控制器,由地址控制器根据收到的内存地址来决定哪个片选引脚输出低电平。

有图上可以看出,如果是NOR启动的情况下,地址在0到0x8000000的范围以内(128M),内存控制器就会让nGCS0被选中,以此类推。

如果不是NOR启动的情况下,那么则无法选中nCGS0。

每一个片选引脚对应的地址范围成为一个Bank,对应这个芯片来说,每个Bank为128M ,其中128M是2的27次方(M为2的10次方,128为2的7次方),那么说明,数据的传送需要使用27根地址线,那么范围应该是ADDR0~ADDR26。

CPU为32位,不代表有32条地址线。CPU范围A地址,地址总长度为32为,其中bit 0 ~ bit 26,会出现在地址线上,而剩下的bit 31 ~ bit 27,是有内存控制器来决定,实际是没有用的。CPU实际是发出了32bit的地址,但是内存控制器只能控制26位。

比如64位CPU来说,实际理论可以支持的最大内存大小为2^64,相当于16,777,216TB,而实际电脑的最大内存不会有这么大,他的最大可用内存由内存控制器来决定。而32位CPU支持的仅仅最大4GB的内存,一般内存控制器可以实现。所以,这就是对于32位的电脑来说,最大的内存支持为4GB;而64位CPU所支持的最大内存可能并不相同。

那么对于内存来说,很重要的功能就是读写。有了地址线、数据线,还有一个非常重要的就是如何来区分是读取还是写入。

所以在内存的芯片上一定是有某某使能的引脚。我们看到在芯片上有nOE和nWE的引脚,他们分别是Output Enable和Write Enable的引脚,并且是以低电平有效。那么他们就是输出使能和写入使能。对于芯片来说的输出,对于2440来说就是读取数据;反之对芯片来说写入,对于2440来说就是写入数据。

从原理图可以看到,Nor Flash是从Addr1开始使用,没有从Addr0开始使用。

不同位宽外设的接线方式

CPU认为一个地址对应一个字节;NOR认为一个地址对应两个字节。(16位的NOR,一次只能读取或写入16位也就是两个字节)

假设CPU访问地址为3的一个字节,那么NOR会读取到地址为2~3的数据。再由内存控制器,从两个自己的内存里面取出自己需要的数据。

如果访问地址2的一个字节,NOR会取出2~3的内存地址的数据。内存控制器,再由其中取出需要使用的数据。

由于1字节和2字节之间相差2倍,那么对于地址的最低位其实是无用的。所以ADDR0作为最后一位的地址是无用的。所以没必要再连接这条线。

- 对于开发版来说,其实就相当于一套小电脑,如果我们组装过电脑,对与上面的组件一般都不会感觉陌生,就算没有组装过,至少也能说出一部分组件的名字。

比如在主板上会有CPU、显卡、内存、网卡等等组件。

而对于嵌入式来说,尤其是Linux嵌入式来说,主要使用的是ARM芯片,也可以称之为SOC(System on Chip),也就是对于一块ARM芯片来说,其中集成了各种模块,比如CPU、I2C、内存模块、网卡模块等等。在ARM芯片外面接上合适的元器件。

- 地址统一编址空间

对于2440芯片来说,可以直接使用内存地址来访问SDRAM和NOR Flash。但是如果需要访问Nand Flash,则需要通过Nand flash控制器来访问(也就相当于SDRAM、NOR Flash和Nand Flash 控制器是2440的儿子,而Nand Flash则是Nand Flash控制器的儿子,也就是2440的孙子)。cpu可以看到NOR的0地址,但是不能直接看到Nand的零地址。Nand不属于CPU的统一编址空间